平成27年度

東京大学 大規模集積システム設計教育研究センター **年報**

2015 VLSI Design and Education Center, The University of Tokyo Annual Report

VLSI Design and Education Center The University of Tokyo 2015

# VLSI Design and Education Center The University of Tokyo

This is the 2014 Annual Report of VDEC (VLSI Design and Education Center, University of Tokyo).

In 2014 we introduced a high-density assembling system as a tool for enhancing added-value of integrated circuits. Taking into account rapid increase of VDEC cleanroom users, the system consists of a flip-chip bonding and its peripheral apparatuses to implement a high-density chip assembly. High-density boards/chip-carriers, to which bare chips are attached, can be fabricated using the electron beam lithography that is already introduced in the cleanroom. Using the new system we are expecting to efficiently integrate bare chips with other devices for demonstrating highly value-added systems, such like sensor systems, integrated MEMS, Ultra-high frequency systems and so on.

Under the circumstance of hard access to new technologies beyond 40 nm CMOS in Japan, we carried out a test run for 28 nm FDSOI/CMOS technology of ST Microelectronics two years ago, collaborating with CMP. It was successfully finished last year, thanks to a lot of cooperation of VDEC major users. We have already made a new menu of the 28 nm FDSOI/CMOS open for all the VDEC users. Because its price per chip area is, however, considerably high, we received many requests from committee members of the VDEC council for chip fabrication menus with moderate prices between 40 nm and 90 nm. So, we have been discussing in VDEC about a possibility of new foundries for these requests, including oversea companies. Fortunately, it was found that the 65 nm CMOS/SOTB, developed by the national project, LEAP (Low-power Electronics Association and Project), will be available via Renesas Electronics even after the end of the project. We have already included it in the chip fabrication menu of VDEC from this year. Though we have to pay attention to the regulation of VDEC academic CAD licenses, the new technology is open for commercial use and oversea countries, as well. We are expecting that it will be used for seamless research and development from academia to industry. We are also recognizing importance of introducing commercial CAD licenses for direct transfer of research results from academia to industry. Though we have been discussing and negotiating on this matter with persons concerned, it will still take a time before providing them from VDEC. Now, new commercial services, such like the cloud CAD tools, are about starting, along with the second/third CAD vendor tools, almost compatible with the mainstream of CAD tools with reasonable prices. It would be important for academia to establish LSI design environments based on these new comers.

As the annual event of the D2T (Design-to-Test) research division, donated by Advantest Corporation, the 9<sup>th</sup> symposium was successfully held on August 26<sup>th</sup> 2014, inviting distinguished lecturers from oversea and domestic institutes. We are scheduling the 10<sup>th</sup> symposium in August 21<sup>st</sup> this year, too. The main subject of the 10<sup>th</sup> symposium will be "Reliability for automotive and other applications." We would like to express our sincere thanks to invited lecturers, audiences and Advantest Corporation for the continuous support.

We will continue to do our best efforts for the original mission of VDEC, "promotion of education and research in LSI design by means of practical chip-design and implementations", in order to realize research and education for enhancing the value of the semiconductor technology. We thank you for your continuous supports again.

June 2015

VLSI Design and Education Center, University of Tokyo Director Kunihiro Asada

KuliAsada

# **Message from Director of VDEC**

#### Activity Report of VDEC 2 Chapter 1

#### 1.1 Introduction of VDEC activities and activity report of FY2014 ----- 2

- 1.2 VDEC CAD Tools ----- 5

- 1.3 VLSI Chip Fabrication ----- 7

- 1.4 Seminar ----- 10

- 1.5 Facilities ----- 14

- 1.6 Activity plan for 2015 ----- 16

- 1.7 Venture companies related to VDEC ----- 17

- I.8 "Nanotechnology Platform" ----- 18 Ultra Small Lithography and Nanometric **Observation Site**

# **Chapter 2**

#### **Activity Report of** "ADVANTEST D2T Research Division" 19

----- 24

- 2.1 Introduction of "ADVANTEST D2T Research Division" ----- 19

- 2.2 Report of "9th D2T Symposium" ----- 20

- 2.3 Research Activity Reports of "Advantest D2T Research Division" ----- 22

- 2.4 Publications ----- 23

Chapter 3 Research in VDEC

# **Chapter 1 Activity Report of VDEC**

1.1 Introduction of VDEC activities and activity report of FY2014

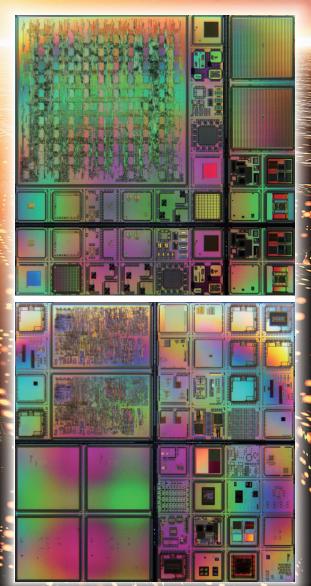

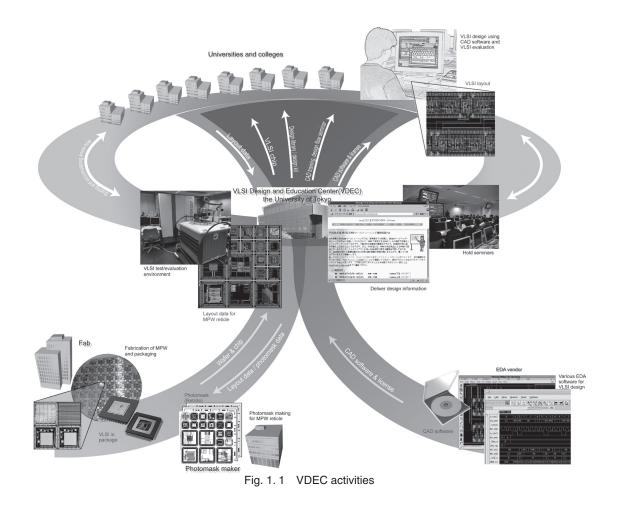

VLSI Design and Education Center(VDEC), University of Tokyo was established in May 1996. VDEC has been operating for the following 3 major roles: "spreading the latest information on VLSI design and education," "providing licenses of CAD tools," and "supporting on VLSI chip fabrications for academic use." The VDEC activity report of FY 2014 is described hereafter according to Fig. 1. 1.

The missions of VDEC are for advancement of researches and education on LSI design in public and private universities and colleges in Japan and send many distinguished VLSI designers into industry. After 18 years of VDEC establishment, educations on CAD software, LSI design and design flow in universities have been well established. On the other hand, advancement on nanometer CMOS technologies forces design flow and CAD software complicated. We have been continuing CAD tool seminar by the lecturers from EDA vendors for twice a year. We hold the seminar in VDEC and provide distance learning through video streaming. We expect spread of the up-to-date LSI design methodology by using CAD tools.

We assume our LSI design flow seminars as educations on basic LSI design concepts and practical experience of LSI design with CAD tool chain. VDEC holds "LSI design education seminar", a.k.a. VDEC Refresh Seminar, once a year. This year we shifted these seminars from November-January time frame to May-July time frame. We also added "Digital design course" in addition to three courses "Analog design course" and "RF design course", and initiated "MEMS design course". We invite experienced professors among universities as lecturers for the courses to conduct LSI design education courses with practical experience. We also hold "Transistor level design flow in VDEC" and "Digital design flow in VDEC EDA environment" for designers in universities. We

started to charge these two LSI design education courses, as well as VDEC Refresh Seminars.

In addition to the above seminars, we hold "VDEC Designer'Forum" among young professors and students annually. This is a workshop that the participants exchange their design examples with not only success stories but also their failure stories, in addition to invited talks. We expect students and professors who will start designs to learn kinds of know-hows. We have initiated "IEEE SSCS Japan Chapter VDEC Design Award" this year, and final examination and awarding have carried out during the "VDEC Designer'Forum". Mr. T. Kawamura (Nara Advanced Institute of Science and Technology (NAIST)) is awarded as "IEEE SSCS Japan Chapter VDEC Design Award" winner, and Mr. C. Monteiro(Gifu Univ.), Mr. T. Yamaguchi(NAIST), Mr. H. Hayami(NAIST), and Mr. T. Usui(Shizuoka Univ.) are awarded as "the best VDEC Design Award", and Dr. S. Wang (Kyushu Inst. of Tech.), Mr. F. Mochizuki (Shizuoka Univ.), S. Yamasaki(Hiroshima Univ.), Ms. A. Oshima(Kyoto Inst. of Tech.), Mr. S. Kanda(Kyoto Inst. of Tech), and Mr. S. Uenohara(Kyushu Inst. of Tech) are awarded as the "VDEC Design Award."

LSI designers come up against various difficulties during actual LSI design scene, even after the basic educations through various seminars and the forum. One of the biggest problems for beginners is the setup of CAD softwares. Many of them also get confused by "Esoteric messages" come out from CAD softwares, even after they successfully setup CAD tools. In such situations, VDEC mailing-lists make significant contributions. VDEC users can register to VDEC mailing-lists on CAD tools, and process dependent groups through VDEC web pages, and can ask questions and helps on their facing issues. It is not a responsibility for the registrant of such mailinglists to give answers to questions, however, in most cases, replies are given by the experienced users of CAD tools and experienced designers within a couple of hours to a couple of days. Moreover, emails are accumulated and are open to the VDEC users, as shown in Fig. 1. 2, who have registered VDEC accounts, as the important educational assets. We expect all the VDEC users to make the full use of this mechanism to help solve problems.

We continue chip fabrication services on 0.18mm CMOS by Rohm and 0.8  $\mu$ m CMOS by On-semi Sanyo Semiconductor. And started chip fabrication services on FDSOI CMOS 28 nm by ST Microelectronics in cooperation with CMP.

Our donated division "Design To Test(D2T)", which was founded by donation from Advantest in Oct. 2008, focuses on enrichment of education on LSI testing and bridging between design and testing.

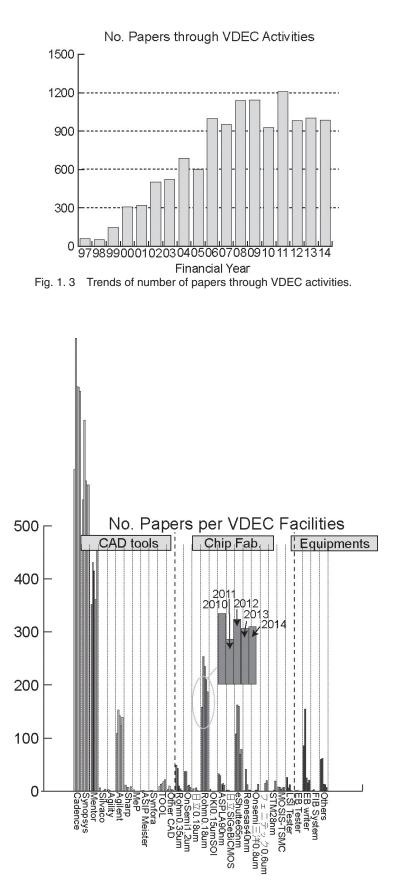

Fig. 1. 4 shows trends of number of papers through VDEC activities. Number of papers is increasing, which means researches in the field of VLSI design have been encouraged after VDEC establishment.

Fig. 1. 5 shows number of papers related to CAD usage, chip fabrications and VDEC facility usages. CAD tools are widely used to write papers. CAD tools are used not only chip designs themselves but also used for preparation of chip fabrication and they contribute to verify fundamental ideas of researches. Advanced CMOS processes are preferred for publications, and not only papers with 65 nm CMOS chips, but also with 45nmCMOS, 32nmCMOS

| アドレス(D) 🖉 http://www                                                                          | ww.vdecu-tokyo.ac.jp/                                                                                                                                                                                                                                                                                                    | ▶ 移動 リンク ※ 配・                                                                                                                   |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                                                                               | ようこそVDECのページへ                                                                                                                                                                                                                                                                                                            |                                                                                                                                 |

| 新着情報                                                                                          | アカウント登録 チップ試作 設計CAD 装置利用 案内 関連リンク                                                                                                                                                                                                                                                                                        | 内部情報 English                                                                                                                    |

| <u>良く利用される</u><br>ページー覧<br>                                                                   | ▲ 設計者のメールリストの過去の<br>Last updated: 03/05/2006 02:37:25                                                                                                                                                                                                                                                                    | 記事                                                                                                                              |

| <u> </u>                                                                                      | 過去のチップ試作においてメーリングリスドに流れたメールを以下に公開致しまでった場合の参考にして下さい。(ただしいずれのページもアクセスをチップ試作に書類を提出した方に限っております) [CAD利用者]全文検索 <ul> <li>4度CAD利用者チップ試作(日付順)##(スレッド順)##(全文)</li> </ul>                                                                                                                                                           |                                                                                                                                 |

| 画<br><u>細立サービス</u><br><u>・ソケットボード情報</u><br><u>チップ試作と支払</u><br><u>状況一覧</u><br><i>CAD関係</i>     | 【モトローラ/オンセミコンダクタ 1.2um] <u>全文検索</u><br>● 00年度第1回モトローラ/オンセミコンダクタ 1.2um予ップ試作 (日付順)<br>● 00年度第2回モトローラ/オンセミコンダクタ 1.2umチップ試作 (日付順)<br>● 01年度第2回モトローラ/オンセミコンダクタ 1.2umチップ試作 (日付加)<br>● 01年度第2回モトローラ/オンセミコンダクタ 1.2umチップ試作 (日付加)                                                                                                  | ## <u>(スレッド順)</u> ## <u>(全文)</u><br>## <u>(スレッド順)</u> ## <u>(全文)</u>                                                            |

| - CAD利用案内<br>- VDECからの御願い<br>- ライセンスファイル<br>の配布<br>- CADアクセスホスト<br>チェック!<br>- CADuserMLの登     | <ul> <li>02年度第1回モトローラ/オンセミコンダクタ12mmキップ試作(日付加)</li> <li>02年度第2回モトローラ/オンセミコンダクタ12mmチップ試作(日付加)</li> <li>03年度第1回モトローラ/オンセミコンダクタ12mmチップ試作(日付加)</li> <li>03年度第1回モトローラ/オンセミコンダクタ12mmチップ試作(日付加)</li> <li>04年度第1回モトローラ/オンセミコンダクタ12mmチップ試作(日付加)</li> </ul>                                                                         | ## (スレッド順)## (全文)<br>## (スレッド順)## (全文)<br>## (スレッド順)## (全文)<br>## (スレッド順)## (全文)<br>## (スレッド順)## (全文)<br>## (スレッド順)## (全文)      |

| 会社<br>CADuserMLの過<br>去記事<br>· CAD講習会案内<br>· CAD講習会案内<br>· CAD講習会下一夕<br>· VDEC数材<br>· 凸版サポートサー | <ul> <li>04年度第2回モトローラ/オンセミコンダクタ12mチップ試作(<u>日付順</u>)</li> <li>05年度第1回モトローラ/オンセミコンダクタ12mチップ試作(<u>日付順</u>)</li> <li>05年度第2回モトローラ/オンセミコンダクタ12mチップ試作(<u>日付順</u>)</li> <li>96年度モトローラ/オンセミコンダクタ12mチップ試作(<u>日付順</u>)</li> <li>97年度第1回モトローラ/オンセミコンダクタ12mチップ試作(<u>日付順</u>)</li> <li>97年度第2回モトローラ/オンセミコンダクタ12mチップ試作(日付順)</li> </ul> | ## <u>(スレッド順)</u> ## <u>(全文)</u><br>## <u>(スレッド順)</u> ## <u>(全文)</u><br>レッド順)## <u>(全文)</u><br>## <u>(スレッド順)</u> ## <u>(全文)</u> |

|                                                                                               | <ul> <li>・ 97年度第2回モトローフ/オンセミコンダウタ 1.20mナップ試作 (日付順):</li> <li>・ 98年度第1回モトローラ/オンセミコンダクタ 1.20mチップ試作 (日付順):</li> </ul>                                                                                                                                                                                                       |                                                                                                                                 |

Fig. 1.2 Archives of emails of VDEC mailing-list.

and 22nmCMOS are emerging in the world. We would like to prepare chip fabrication services for the advanced CMOS processes. In addition, we would like to setup chip fabrication services related to CMOS/MEMS to fulfill the researches for "More than Moore". We also encourage researchers to fully use of VDEC facilities such like LSI testers, FIB systems and EB writer for the wide spread of research purposes.

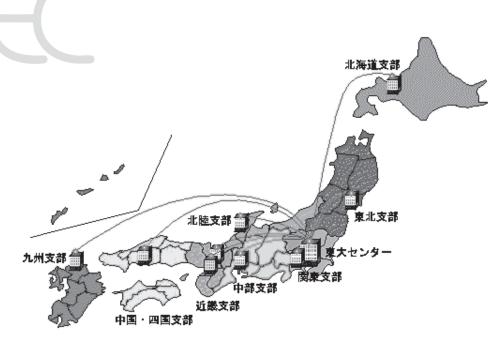

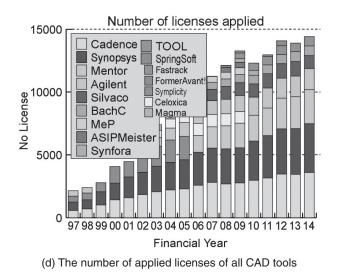

# 1.2 VDEC CAD Tools

Since 1996, VDEC has provided CAD software licenses to the registered researchers in universities and colleges in Japan. The CAD tools we provided in 2009 are shown in Table 1. 2. 1. The researchers can use those CAD tools when their local machines, whose IP addresses are registered in advance, are authorized by one of VDEC license server located in the ten VDEC subcenters shown in Fig. 1. 2. 1. For each CAD tool, VDEC provides 10-100 floating licenses. Those CAD tools can be utilized only for research and education activities in national universities, other public universities, private universities, and colleges.

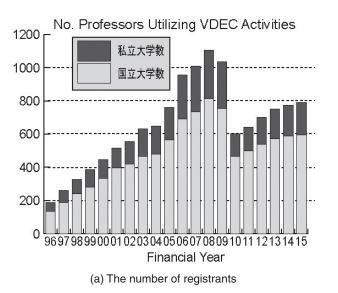

When one is going to use VDEC CAD tools and chip fabrication service (the details are described in Section 1-3), some faculty member of his/her research group in a university or a collage needs to do user registration. Fig. 1. 2. 2 shows (a) the number of registrants, (b) the number of distinguished universities/colleges of the registrants, and (c) the number of registrants who applied VDEC CAD tools.

| Name              | Function                                                                                                                                                                                                                                                                | Vendor                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Cadence tool set  | Verilog-HDL/VHDL entry, Simulation, Logic synthesis,<br>Test pattern generation, Cell-based (including macros)<br>place, route, and back-annotation, Interactive schematic<br>and layout editor, Analog circuit simulation, Logic verifi-<br>cation, Circuit extraction | Cadence Design Systems, Inc. |

| Synopsys tool set | Verilog-HDL/VHDK simulation, Logic synthesis, Test<br>pattern generation, Cell-based (including macros) place,<br>route, and back-annotation, Circuit simulation, Device<br>simulation                                                                                  | Synopsys, Inc.               |

| Mentor tool set   | Layout verification, Design rule check                                                                                                                                                                                                                                  | Mentor Graphics Co. Ltd.     |

| Silvaco tool set  | Fast circuit simulation                                                                                                                                                                                                                                                 | Silvaco                      |

| ADS/Golden Gate   | Design and verification of high-frequency circuits                                                                                                                                                                                                                      | Agilent Technologies         |

| Bach system       | BachC-based design, synthesis, and verification                                                                                                                                                                                                                         | Sharp                        |

| LAVIS             | Layout visualization platform                                                                                                                                                                                                                                           | TOOL                         |

| Laker, Verdi      | Layout editor and debugger                                                                                                                                                                                                                                              | Springsoft Inc.              |

| Table | 1. | 2. | 1 | VDEC | CAD | tools |

|-------|----|----|---|------|-----|-------|

|-------|----|----|---|------|-----|-------|

Fig. 1. 2. 1 VDEC Subcenters

No. Universities Utilizing VDEC Activities No. Universities Utilizing VDEC Activities Public Public Public 9697989900010203040506070809101112131415 Financial Year (b) The number of universities colleges of the registrants

No. Labs. using VDEC CAD tools No. Labs. using VDEC CAD tools

Fig. 1. 2. 2 The numbers of VDEC CAD Applications

# 1.3.1 Trends of VLSI Chip Fabrication Services

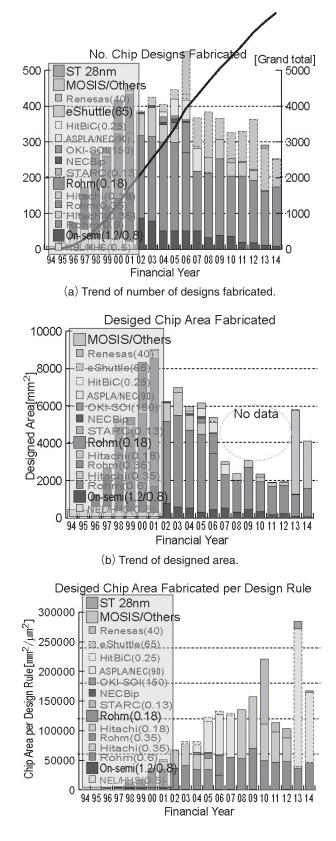

Fig. 1. 3. 1 shows a trend of number of designed chips for VDEC chip fabrication services, including pilot project prior to VDEC establishment.

VLSI chip fabrication is limited to 0.5  $\mu$ m CMOS provided by NTT Electronics during the pilot project in 1994 and 1995. VDEC chip fabrication had started in 1996 with 1.2  $\mu$ m CMOS provided by Motorola Japan, which is now On-Semiconductor as well as the 0.5  $\mu$ m CMOS. In 1997, VDEC received cooperation from Rohm and has started 0.6  $\mu$ m CMOS process. In 1998, VDEC started chip fabrication services of 0.35  $\mu$ m CMOS by Hitachi, and in 1999, VDEC started 0.35  $\mu$ m CMOS by Rohm. We had a test chip fabrication of 0.13  $\mu$ m CMOS by STARC through "IP development project" in 2001. We added 0.18 µm CMOS by Hitachi into our chip fabrication menu in 2001. From 2002, we started VDEC-MOSIS chip fabrication program initiated by Prof. Iwata of Hiroshima University. Under this program, VDEC member can access to TSMC and IBM processes with lower price. We also started Bipolar chip fabrication by NEC Compound Semiconductor Devices. In 2004, we started 0.15  $\mu$ m SOI-CMOS chip fabrication by Oki Electric as test chip fabrications. In the same year we started 90 nm CMOS chip fabrication by ASPLA/STARC. In 2006, we started 0.18 µm CMOS by Rohm and 0.25 µm SiGeBiCMOS by Hitachi. In 2008, we started 65 nm CMOS process by eShuttle, after closure of 90 nm CMOS chip fabrication in 2007. In 2010, we started 40 nm CMOS process by Renesas Electronics through "Next Generation Semiconductor Circuits & Architecture" project between METI and STAR. On the other hand, 1.2  $\mu$ m CMOS chip fabrication program came to end by the September 2011. 40 nm CMOS by Renesas Electronics and 65 nm by eShuttle also come to end by Oct. 2012 and Aug. 2013, respectively. We started CMOS 0.8 µm in Oct. 2012 by On-semiconductor-Sanyo as a test chip fabrication and opened it as the regular chip fabrication menu in 2012. We started FD-SOI 28 nm CMOS by ST-Microelectronics through CMP, France, as the advanced CMOS process in 2013.

Fig. 1. 3. 1(a) shows trends of number of chip designed for VDEC chip fabrication. For the first 6 years until 2001, the number of designed chips shows steady increase, which means drastic improve of the effectiveness researches and education of LSI design, and we assume drastic increase of number of students related to LSI chip

(c) Trend of designed area normalized by design rule.

design and education. During few years of stable number around 400 chip designs per year, we can see transition of designs toward finer process. In 2007, we saw a large drop, which was caused by sudden process transition from 0.35  $\mu$ m CMOS to 0.18  $\mu$ m CMOS, and in 2008, we also saw another drop by process transition from 90 nm CMOS to 65 nm CMOS.

Fig. 1. 3. 1(b) shows trends of designed chip area, which shows much clear trends of drop by process migration. On the other hand, Fig. 1. 3. 1(c) shows trends of designed chip area normalized by design rule, which assume to be strong relation with design efforts. Coming from the fact that the normalized chip area is still growing, we assume the major reason for decrease of number of chips and designed area is increase of design effort per chip and per unit area due to process scaling.

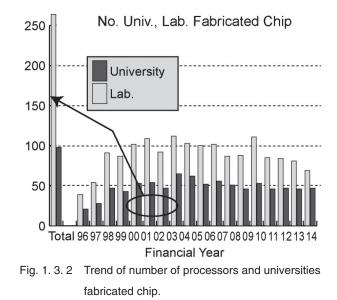

Fig. 1. 3. 2 shows trends number of professors and universities fabricated chip. Number of professors who have contracted NDA for process technologies to access design rules and design libraries are, 262, and 32, respectively, for 0.18  $\mu$ m CMOS, and 0.8 um CMOS.

Table 1. 3. 1Chip fabrication schedule in 2014 $\bigcirc$  0.8  $\mu$ m CMOS (On-Semiconductor - Sanyo)

# 1.3.2 Overview of chip fabrication in 2014

Table 1. 3. 1 lists chip fabrication schedule in 2014. Please refer to list in Chapter 2 for details of designers and contents of chip designed.

|         | Chip application deadline | Design deadline | Chip delivery    |  |  |  |

|---------|---------------------------|-----------------|------------------|--|--|--|

| 2014 #1 | 2014/ 7/14                | 2014/10/ 6      | 2014/12/18       |  |  |  |

| 2014 #2 | 2014/12/29                | 2015/ 3/23      | 2015/6(Schedule) |  |  |  |

#### $\bigcirc$ 0.18 $\mu$ m CMOS (Rohm)

|         | Chip application deadline | Design deadline | Chip delivery    |

|---------|---------------------------|-----------------|------------------|

| 2013 #5 | 2013/11/ 4                | 2014/ 1/27      | 2014/ 5/14       |

| 2014 #1 | 2014/ 1/27                | 2014/ 4/21      | 2014/ 8/ 5       |

| 2014 #2 | 2014/ 4/14                | 2014/ 7/ 7      | 2014/10/21       |

| 2014 #3 | 2014/ 6/ 9                | 2014/ 9/ 1      | 2014/ 1/28       |

| 2014 #4 | 2014/ 8/25                | 2014/11/17      | 2014/ 3/12       |

| 2014 #5 | 2014/11/ 3                | 2015/ 1/26      | 2015/5(Schedule) |

#### ○ 28 nm CMOS (STMicro/CMP)

|           | Chip application deadline | Design deadline | Chip delivery |

|-----------|---------------------------|-----------------|---------------|

| 2015 Jan. |                           | 2015/ 1/ 5      |               |

# 1.3.3 Libraries and design flows

and design flows for digital design and PDKs for analog design. Table 1. 3. 2 lists libraries available now.

VDEC have been working to prepare design libraries

| Technology                          | Name                           | Author                                                                                 | Contents                |

|-------------------------------------|--------------------------------|----------------------------------------------------------------------------------------|-------------------------|

| $0.18 \mu \mathrm{m} \mathrm{CMOS}$ | Rohm                           | Rohm Library                                                                           | Synthesis(Synopsys)     |

| (Rohm)                              | library                        | Std. Cells, IO cells, RAM<br>(Distributed with CDROM)                                  | Simulation (VerilogXL)  |

|                                     |                                |                                                                                        | P&R(LEF/DEF)            |

|                                     | Kyodai                         | y Onodera Lab., Kyoto University<br>y VDEC<br>Design flow based on library prepared by | Synthesis(Synopsys)     |

|                                     | Library                        |                                                                                        | Simulation (VerilogXL)  |

|                                     |                                |                                                                                        | P&R(Astro)              |

|                                     | Todai                          |                                                                                        | Synthesis(RTL Compiler) |

|                                     | Library                        |                                                                                        | Simulation (VerilogXL)  |

|                                     | Onodera Lab., Kyoto University | P&R(Encounter)                                                                         |                         |

|                                     | PDK                            | VDEC                                                                                   | PDK(IC6.1)              |

Table 1. 3. 2 Libraries available for VDEC chip fabrication

# 1.4 Seminar

Seminar is indispensable for the improvement of LSI design technology. Some seminar and forums, such as technical seminar for CAD use, refreshing seminar for working people, designer's forums for young professors and students were held in 2011.

### [Technological seminar for CAD use]

In a technological seminar for CAD use, VDEC invites lecturer from each tool vender, such as Cadence, Synopsys and Agilent, to hold the CAD operation course. Moreover, the course concerning the design flow in the VDEC environment was held by the VDEC staff. A technological seminar for CAD use for the beginner was held in The University of Tokyo VDEC in August and September at the year 2014. This seminar took 5 days for 2 kinds of Cadence tools, 5 days for 3 kinds of Synopsys tools, 1 days for 1 kind of Agilent tool. In addition, VDEC teachers gave lecturers on transistor level circuit design course, and digital circuit design course under the VDEC EDA environment. Teachers and students up to 40 people attended a lecture in each course, and master the use of each tool for VLSI design flow that uses the VDEC library. Moreover, another technical seminar for CAD use for matured teachers and students was held in March by Cadence 2 kind and 3 days, Synopsys 3 kinds and 4 days, Agilent 1 kind and 1 days (Table 1. 4. 1). The demand for these CAD technological seminars is very large, and VDEC has maintained the mechanism of a large-scale CAD technological seminar holding corresponding to this situation. So far, the seminar was held at the University of Tokyo OR other VDEC branch, however, we started to distribute the lecture using Web streaming, so that students around VDEC branch can take the seminar at the branch school.

Table 1. 4. 1 CAD technological seminar in summer of the year 2013

| 9<br>1<br>2<br>2<br>1 |

|-----------------------|

| 2                     |

| 2                     |

|                       |

| 1                     |

|                       |

| 13                    |

| 3                     |

| 1                     |

| 5                     |

| 12                    |

| 3                     |

| 2                     |

| 3                     |

| 17                    |

| 2                     |

| 1                     |

| 1                     |

| 5                     |

| 3                     |

| 23                    |

| 25                    |

| -                     |

| 2014/09/17-18 | Synopsys Design Compiler+Power Compiler Seminar | Univ. of Tokyo  | 13 |

|---------------|-------------------------------------------------|-----------------|----|

| 2014/09/17-19 | Synopsys Design Compiler+Power Compiler Seminar | Kanazawa Univ.  | 1  |

| 2014/09/17-20 | Synopsys Design Compiler+Power Compiler Seminar | Kyoto Univ.     | 1  |

| 2014/09/17-21 | Synopsys Design Compiler+Power Compiler Seminar | Osaka Univ.     | 6  |

| 2014/09/24-26 | Cadence IC61 Virtuoso Layout Seminar            | Univ. of Tokyo  | 22 |

| 2014/09/24-27 | Cadence IC62 Virtuoso Layout Seminar            | Kanazawa Univ.  | 3  |

| 2014/09/24-28 | Cadence IC63 Virtuoso Layout Seminar            | Hiroshima Univ. | 1  |

| 2015/03/06    | Synopsys TCAD Seminar             | Univ. of Tokyo  | 10 |

|---------------|-----------------------------------|-----------------|----|

| 2015/03/07    | Synopsys TCAD Seminar             | Tohoku Univ.    | 7  |

| 2015/03/08    | Synopsys TCAD Seminar             | Kanazawa Univ.  | 2  |

| 2015/03/09    | Synopsys TCAD Seminar             | Nagoya Univ.    | 1  |

| 2015/03/10    | Synopsys TCAD Seminar             | Osaka Univ.     | 4  |

| 2015/03/11    | Synopsys TCAD Seminar             | Hiroshima Univ. | 3  |

| 2015/03/10    | Agilent ADS Momentum Seminar      | Univ. of Tokyo  | 10 |

| 2015/03/11    | Agilent ADS Momentum Seminar      | Tohoku Univ.    | 4  |

| 2015/03/12    | Agilent ADS Momentum Seminar      | Nagoya Univ.    | 1  |

| 2015/03/11    | Synopsys XA+VCS mixed sim Seminar | Univ. of Tokyo  | 7  |

| 2015/03/12    | Synopsys XA+VCS mixed sim Seminar | Hokkaido Univ.  | 5  |

| 2015/03/13    | Synopsys XA+VCS mixed sim Seminar | Tohoku Univ.    | 5  |

| 2015/03/14    | Synopsys XA+VCS mixed sim Seminar | Hiroshima Univ. | 1  |

| 2015/03/18    | Synopsys HSPICE Seminar           | Univ. of Tokyo  | 17 |

| 2015/03/19    | Synopsys HSPICE Seminar           | Hokkaido Univ.  | 3  |

| 2015/03/20    | Synopsys HSPICE Seminar           | Tohoku Univ.    | 5  |

| 2015/03/21    | Synopsys HSPICE Seminar           | Nagoya Univ.    | 1  |

| 2015/03/22    | Synopsys HSPICE Seminar           | Kyoto Univ.     | 1  |

| 2015/03/23    | Synopsys HSPICE Seminar           | Osaka Univ.     | 5  |

| 2015/03/24    | Synopsys HSPICE Seminar           | Hiroshima Univ. | 1  |

| 2015/03/25    | Synopsys HSPICE Seminar           | Nagasaki Univ.  | 2  |

| 2015/03/26    | Synopsys HSPICE Seminar           | Miyazaki Univ.  | 6  |

| 2015/03/12-13 | Cadence OrCAD Seminar             | Univ. of Tokyo  | 5  |

| 2015/03/12-14 | Cadence OrCAD Seminar             | Hokkaido Univ.  | 4  |

| 2015/03/12-15 | Cadence OrCAD Seminar             | Tohoku Univ.    | 3  |

| 2015/03/25-27 | Cadence EDI Seminar               | Univ. of Tokyo  | 6  |

| 2015/03/25-28 | Cadence EDI Seminar               | Hokkaido Univ.  | 5  |

| 2015/03/25-29 | Cadence EDI Seminar               | Nagoya Univ.    | 1  |

| 2015/03/25-30 | Cadence EDI Seminar               | Osaka Univ.     | 7  |

| 2015/03/25-31 | Cadence EDI Seminar               | Hiroshima Univ. | 1  |

# [Refresh Seminar for Working People]

Teachers of universities and designers in the first line of the enterprise were invited to the lecturer at "VLSI design refresh seminar" was held aiming at the latest, advanced knowledge and technical learning concerning VLSI design as a refreshing education for working people involved in the integrated circuit industry (Table 1. 4. 2). Though this seminar started chiefly in year 1998 under the support of Ministry of Education Technical Education Division to give practicing education of the latest VLSI design technology, it continues under many supports from many societies.

Course A: analog integrated circuit design (5/26-5/28), Course D:digital integrated circuit design (6/3-6/5), Course M1: MEMS design (6/12-6/13), Course M2:MEMS fabrication (6/25-6/27), and Course R: RF circuit design (7/3-7/4). Teachers from industry and universities involved in the integrated circuit research and the education were invited as the lecturer, and they introduced a state-of-the-art VLSI design technology including the practice using a lecture concerning VLSI design and the latest CAD tool. The participants for the course A, D, M1, M2, R were 22, 21, 7, 6, 17, respectively.

Fig. 1. 4. 1 Refresh Seminar at VDEC seminar room at the University of Tokyo, VDEC.

#### Table 1. 4. 2 Refresh Seminar

Course A: Analog Circuit Design (3 days)

Analog Circuit Design and simulation Integrated Circuits Verification (LVS, DRC)

Masahiro Sugimoto (Chuo Univ.), Hidetoshi Onodera (Kyoto Univ.), Koji Kotani (Tohoku Univ.)

Course M1: MEMS Design (2 days)

MEMS Basic 1: Fabrication Process MEMS Basic 2: Operation Principle Structual Design Layout Design

Yoshio Mita (Univ. of Tokyo)

Course M2: MEMS Fabrication (3 days)

CAD Design and Analysis Lithography, Etching, Release Vibration measurement and analysis

Yoshio Mita (Univ. of Tokyo)

| Course D: Digital Circuit Desig | ו (3days) |

|---------------------------------|-----------|

|---------------------------------|-----------|

Verilog HDL Logic Synthesis, P&R, Layout Verification Embede Analog Macros and SRAM

Makoto Ikeda (Univ. of Tokyo)

Course R: CMOS-RF Circuit Design (3days)

Modulation/Demodulation, Cascaded connection Basic Performace, Tranceiver Architecture Circuit Element, Design Flow

Hiroyuki Ito (Tokyo Institute of Technology)

# [Designer's forum for young teachers and students]

VDEC LSI designer forum intended for students and young teachers has been held. The VDEC LSI designer forum has aimed to sharing information that cannot be obtained at a society and a academic society, for example, the failure case and the solution in which LSI designer has a hard time, the inside story of CAD industry, the construction method in the design milieu in the laboratory, and so on. This year, we had the meeting in Noro Hot Spring, in August. No less than 31 participants were flourishing at the gathering.

| 8/29 (Fri)  |                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------|

| Time        |                                                                                                       |

| 10:30-11:00 | Reception                                                                                             |

| 11:00-13:00 | VDEC Design Award second selection:<br>Short presentation & Poster session & voting/totaling          |

| 13:00-14:00 | lunch                                                                                                 |

| 14:20-14:30 | Opening remark                                                                                        |

| 14:30-15:20 | Plenary Talk<br>Toshio Yoshida (Fujitsu)<br>SPARC64 XIfx: Fujitsu's Next Generation Processor for HPC |

|             | break                                                                                                 |

| 15:30-18:00 | VDEC Design Award presentation by the finalists                                                       |

| 18:00-20:00 | Design Award final totaling, award ceremony                                                           |

Table 1.4.3 Program of Designers Forum in 2011.

#### 8/30 (Sat)

| Time        |              |

|-------------|--------------|

| 10:00-12:00 | Ph.D session |

# 1.5 Facilities

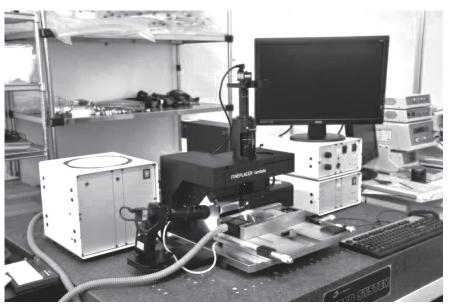

The VDEC has provided the big facilities for universities in Japan from its establishment (1996). Big facilities refer to those which are impossible to acquire and or maintain by an individual research unit. Table 1. 5. 1 shows the available facilities of VLSI testers and some process machines, which are placed at the tester room and the super clean room of the Takeda building. In 2004, the VLSI tester (T2000) and the EB lithography machine (F5112+VD01) were donated to the VDEC by the ADVANTEST. In the year 2012, VDEC joined MEXT (Ministry of Education)'s Nanotechnology platform to enforce its multi-use capability. (For Nanotechnology Platform refer section 1. 8). In the FY 2014, VLSI chip integration apparatuses were installed in the cleanroom. The apparatus include Precision Manual Flip-chip Bonding machine (Finetech Fineplacer Lambda, Fig. 1) that can align two chips face-to-face under TV-camera observation. The precision is XY  $\pm$  0.5µm, and  $\theta$  =1 mrad, Semi-Auto Wire Bodner (Westbond 4700E) that can bond gold bump and or bumped wires. Also, Vapor phase HF machine was installed for stable MEMS releasing process. From April 2014 to March 2015, the EB lithography machine F5112 has been used 2074 times. The increase of number since last year (1,594 times) was very large. The reason was opening the new apparatus (F7000S-VD02) to public, yielding average exposure count increase as well (160->173 exposures/month) The facilities can be used by user after learning how to use the a couple of attended use; use result can directly be obtained by attended use.

| Facility                                  | Equipment name                                                          | Description                                                                                                                                                                                                                        | Status    | Contact                           |

|-------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------|

| Logic LSI test<br>System                  | EB tester:<br>IDS10000                                                  | The chip surface voltage during operation<br>can be measured with the LST tester.<br>The digital circuit with 384 pins, 1 GHz can<br>be tested.                                                                                    | Available | equipment@<br>vdec.u-tokyo.ac.jp  |

|                                           | LSI tester:<br>ADVANTEST T2000                                          | The digital circuit with 256 pins, 512 MHz can be tested. Analog test is optional.                                                                                                                                                 | Available | equipment@<br>vdec.u-tokyo.ac.jp  |

|                                           | FIB: IDSP2X                                                             | Cutting wires of LSIs and depositing Pt wires are available to repair the LSI design errors.                                                                                                                                       | Available | IDSP2X@<br>vdec.u-tokyo.ac.jp     |

|                                           | Auto prober:<br>PM-90-A                                                 | Automated prober for testing LSI wafers,<br>which can be used with the LSI testers. The<br>probe card for LSIs with the VDEC standard<br>pin connections is available.                                                             | Available | equipment@<br>vdec.u-tokyo.ac.jp  |

| Analog/RF<br>measurement<br>system        | Analog/RF measure-<br>ment system:<br>HP4156B, HP4284, etc              | DC parameter measurement, Capacitance<br>measurement, Network analyzer, Spectrum<br>analyzer, etc.                                                                                                                                 | Available | equipment@<br>vdec.u-tokyo.ac.jp  |

|                                           | Low-noize manual prob-<br>er:<br>Cascade Microtec                       | 6 inch wafer can be measured with six DC probles and two RF probes upto 50 GHz.                                                                                                                                                    | -         |                                   |

|                                           | Low-noize, temperature<br>controlled semi-auto<br>prober: Süss Microtec | 8<br>inch wafer can be measured. The chip temperature range is -50 to<br>$200{\rm °C}$ .                                                                                                                                           |           |                                   |

| Nanotechnology<br>Platform<br>Apparatuses | Mask lithography,<br>Direct lithography:<br>F5112+VD01                  | Minimum linewidth: 50 nm.<br>Lithography for 5 inch photomask (thick-<br>ness: 2.3 mm), 2-8 inch wafers, and chips is<br>possible.                                                                                                 | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                           | Rapid Mask and Direct<br>lithography: F7000S-<br>VD02                   | Minimum linewidth: 1xnm.<br>Lithography for 5 inch photomask (thick-<br>ness: 2.3 mm), 2-8 inch wafers, and chips is<br>possible. Stencil character projection of non-<br>square shapes such as circle, triangle is pos-<br>sible. | Available |                                   |

Table1. 5. 1 Available facility list

|                        | Chlorine ICP plasma<br>etcher CE-S                                  | High density plasma etching with $Cl_2$ and $BCl_3$ is possible.                                                                                                                                                                                 | Available |

|------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                        | Silicon DRIE MUC-21<br>ASE-Pegasus                                  | High speed, high aspect ratio etching of sili-<br>con is possible                                                                                                                                                                                | Available |

| FIB system             | FIB:<br>SII XVision200TB                                            | Repairment of photomask, sample etching,<br>etc. (Through Nanotech. Platform and<br>LCNet)                                                                                                                                                       | Available |

| Chip Bonding<br>System | Wedge Bonder:<br>Westbond 7476D                                     | $25\mu m \phi$ Al or Au wire wedge bonding machine.                                                                                                                                                                                              | Available |

|                        | Epoxy Die Bonder<br>Westbond7200C                                   | Precision Manupilator system. Epoxy and or Ag paste chip bonding and or glued wiring.                                                                                                                                                            |           |

|                        | Semi-Auto Bonder<br>Westbond4700E                                   | $18 \sim 25 \mu m \phi$ Au Ball bonding or bump creation.                                                                                                                                                                                        |           |

|                        | Precision Manual Flip-<br>Chip Bonder Finetech<br>Fineplacer Lambda | Face-to-face bonding up to 15 mm square<br>chips. Alignment is through video camera.<br>Bonding is by heating chips with TV camera.<br>(Ultrasonic Unit can additionally be pur-<br>chased.) XY $\pm$ 0.5µm, and $\theta$ =1mrad preci-<br>sion. |           |

Fig. 1 Precision Manual Flip-Chip Bonder Finetech Fineplacer Lambda

# 1.6 Activity plan for 2015

VDEC will continue activities on chip fabrication services, CAD tool support, dispatching design related information and donated division "D2T", as has been previous years.

# [Design related information dispatching/Seminar]

We will continue holding the following seminars: (1) CAD tools seminars which have been continued since 1997, (2) "Refresh seminar" since 1998, (3) "Designer Forum" since 1997. We will also continue seminars for LSI tester usage at VDEC and sub-centers, workshops on LSI testing technologies initiated by D2T.

### [CAD tool support]

We will continue Cadence tools, Synopsys tools and Mentor tools as the main stream design tools. We will continue analog RF design environment, GoldenGate and ADS by Agilent, C-based design environment, BachC by Sharp. In addition, we continue trial of several CAD tools, such as layout platform, Lavis by TOOL. Design debugging platform from SpringSoft has merged into Cadence tools and will be continued. SmartSpice by Silvaco, will be also continued.

# [Chip fabrication services]

We will continue chip fabrication services for 0.18  $\mu$ m CMOS by Rohm, FD-SOI 28 nm CMOS by ST Microelectronics through CMP and 0.8  $\mu$ m CMOS by On-semiconductor-Sanyo as the regular services. We will start regular services of SOTB CMOS 65 nm by Renesas Electronics. We will ask packaging for the above chip fabrications to J-Device to meet the diverse needs of the assembly.

# Table 1.7.1 Chip fabrication schedule

| [CMOS 1.2 $\mu$ m 2P2M] | On-Semiconductor | (Former Motorola Japan) |

|-------------------------|------------------|-------------------------|

|-------------------------|------------------|-------------------------|

|        | Chip application deadline | Design deadline | Chip delivery |

|--------|---------------------------|-----------------|---------------|

| 2015#1 | 2015/7/6                  | 2015/9/28       | 2015/12/28    |

| 2015#2 | 2015/12/29                | 2016/3/22       | 2016/6/20     |

#### [CMOS 0.18 µm 1P5M (+MiM)] Rohm

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2015 #2 | 2015/4/13                 | 2015/7/6        | 2015/10/30    |

| 2015 #3 | 2015/6/1                  | 2015/8/24       | 2015/12/11    |

| 2015 #4 | 2015/8/24                 | 2015/11/16      | 2016/3/18     |

| 2015 #5 | 2015/11/2                 | 2016/1/25       | 2016/5/20     |

#### [FD-SOI CMOS 28nm 1P10M] ST Microelectronics

Based on the chip fabrication schedule through CMP.

#### [SOTB CMOS 65nm] Renesas Electronics

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2015 #1 | 2015/6/1                  | 2015/7/13       | 2016/1/5      |

| 2015 #2 | 2015/12/1                 | 2016/1/12       | 2016/7/6      |

# 1.7 Venture companies related to VDEC

Some professors related to VDEC started venture companies. The following is a list of the venture companies related to VDEC.

### [1] AIL Co.,Ltd. (http://www.ailabo.co.jp/)

Related professor : Professor Kazuo Taki, Kobe Univ. (President-Director)

### [2] Synthesis Corporation (http://www.synthesis.co.jp/)

Related professor : Professor Emeritus Isao Shirakawa, Osaka Univ. (Director)

Description of business : (1) Hardware/software co-design

- (2) System LSI design, design services

- (3) Development and sales of IPs

- (4) Development of EDA tools

### [3] Nanodesign Corporation (http://www.nanodesign.co.jp/)

Related professor : Professor Kazuyuki Nakamura, Kyushu Institute of Technology. (Representative Director)

### [4] A-R-Tec Corp. (http://www.a-r-tec.jp/)

Related professor : Professor Emeritus Atsushi Iwata, Hiroshima Univ. (Representative Director) Description of business : (1) Measurement and analysis of LSI substrate noise

- (2) Design of analog-RF mixed signal LSIs

- (3) Training of analog design on the JOB method

# I.8 "Nanotechnology Platform": Ultra Small Lithography and Nanometric Observation Site

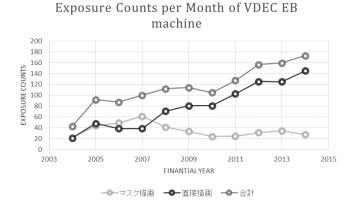

VDEC is operating an open-use nanotechnology platform "Ultra Small Lithography and Nanometric Observation Site" together with the Institute of Engineering Innovation of Graduate School of Engineering. The site is supported by Japanese Ministry of Education (MEXT)'s Nanotechnology Platform grant. Any researchers in Japanese Universities, Laboratories, and Companies can take full advantage of The University of Tokyo's cutting-edge nanotechnology apparatuses and know-hows. The accessible technology includes Lithography and Etching environment, Ultra High-Voltage Acceleration (1MV) transmission electron microscope (TEM) that is capable of visualizing upto light materials such as Nitrogen. VDEC takes part in the lithography at Takeda Sentanchi Super Cleanroom. Through VDEC's key apparatus F5112+VD01 donated from Advantest Corporation as well as F7000S-VD02 purchased by national budget, VDEC is supporting post-VLSI activities such as MEMS. The machine is capable of rapidly writing patterns on arbitrary-shaped targets sizing from 1cm-sqare chip to 8-inch round wafers. The performance is measured by the number of research reports and machine use. The University of Tokyo site has received 179 (150 for precedent year) research reports including 17 (9) from big companies, 10 (3) from Small and Medium-size Enterprises (SMEs), 36 (32) from other universities, 109 (100) from UTokyo researchers (including external collaboration but excluding VDEC), and 7 (6) from public research institutes. The exposure count was 2074 for 12 months (172.4/month), which is the record since beginning of existing statistics (460 for FY 2000). As shown in the Fig. 1, usage is monotonously increasing. "Open ratio", which is the number of days in which users outside the University of Tokyo came, divided by machine open days, was 99%. Due to the strong support of nanotech. Platform, even a novice user can obtain fine lithography result by using the apparatuses with the Platform Engineering Staffs of VDEC.

URL:<u>http://nanotechnet.t.u-tokyo.ac.jp/</u>

Fig. 1 Monthly Average Exposure Count of EB Machine (s).

# 2. Activity Report of "ADVANTEST D2T Research Division"

2.1 Introduction of "ADVANTEST D2T Research Division"

# 2.1.1 Aim of the establishment of "ADVANTEST D2T Research Division"

ADVANTEST D2T research division was established in VDEC in October 2007. As the name of the research division indicates, it is financially supported by ADVANTEST Corporation.

The aim of establishment of ADVANTEST D2T research division is to promote the research and education environment of VLSI testing in all universities and colleges in Japan. "D2T" means that we consider not only design but also test. As the results of our activities, we hope to provide the experts of design and test for industry. In addition, we are exchanging researchers with other universities or research institute in both Japan and overseas. Moreover, D2T research division is in a good environment to make collaboration with industry because testing of VLSI is one of the most practical research topics in industry. Based on those activities, our final goal is to become the center of excellence of VLSI Testing in Japan.

The first phase and the second phase of D2T activities had finished in September 2010 and September 2013, respectively. We are currently in its third phase that started in October 2013 through the courtesy of ADVANTEST Corporation. We have finished the middle year of the third phase with very fruitful achievements in research, education, symposium organization, and so on. Their details are presented in the following sections in this report.

# 2.1.2 Members of "Advantest D2T Research Division"

| Project Lecturer    | Rimon Ikeno                   |

|---------------------|-------------------------------|

| Assistant Professor | Nguyen Ngoc Mai Khanh         |

| Researcher          | Takahiro Yamaguchi            |

|                     | (Advantest Laboratories Ltd.) |

| Researcher          | Masahiro Ishida               |

|                     | (Advantest Corporation)       |

| Assistant Clerk     | Makiko Okazaki                |

# 2.2 Report of "9th D2T Symposium"

"The 9th D2T Symposium" was held on August 26th, 2014 at Takeda Building.

With the main theme of "System, Circuit, and Testing of Ultra-Low Voltage VLSI", the symposium had eight lectures from wide variety of technical fields like process/ device technology, circuit, system, and testing of ultralow voltage LSI operation. Following these lecture sessions, we had a panel discussion entitled "FD SOI for analog-digital compatibility in ultra-low voltage era" and a reception in the evening. The number of the attendees was more then 180, which made the record through the whole D2T Symposium history. Here we would like to express our warm gratitude again to all these participants at the symposium.

The invited lecturers are distinguished researchers and engineers in each filed. The audience must have made use of such great opportunity to exchange their thoughts with these great lectures at the sessions, the panel, and the reception, we hope.

D2T Symposium will be continuously held in the future. The date of the next, 10th, symposium is fixed in this year in the same season as the 9th symposium. We expect many attendees there again.

| 東京大学                                                                                   | <ul> <li>         提集積システム設計教育研究センター VLSI Design and Education Center VCC         <ul> <li></li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 「設計」と「テスト」<br>開催して参りました「<br>今回はシンポジウム<br>として、LSIの低調                                    | の構造しを目的とした研究・教育活動を行なっています。その一環として<br>DCTシンポジウム」も、おかげきまでもEIIEを残えることとなりました。<br>DCTシンポジウム」も、おかげきまでもEIIEを残えることとなりました。<br>EIIEA部計からアスト技術系で読のいつ野の情報を対象定して、それぞれの分野での知識の深<br>には作に関するEIIEA設計、テスト技術などの分野で活躍している国内外<br>本者付請完整門からの活動場合、講具者によるパネルディスカッショ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10:00                                                                                  | 開会の携援 プログラム                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10:15                                                                                  | VDEC の活動紹介                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <i>10:25</i><br>セッション<br>1                                                             | <ul> <li>"Phase Noise and Time Jitter: Origins, Analysis, and Design for Mitigation"</li> <li>Asad A. Abldl (University of California, Los Angeles)</li> <li>"Numerical and Theoretical Analysis on Voltage and Time Domain Dynamic Range of Scaled CMOS Circuits"</li> <li>名倉徹 (東京大学)</li> <li>"A Subsampling Stochastic Coarse-Fine ADC with SNR 55.3dB and &gt;5.8TS/s Effective Sample Rate for an on-Chip Signal Analyzer"</li> <li>山口 隆弘 (株式会社アドバンテスト研究所)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12:00                                                                                  | <b>昼食</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13:15<br>セッション<br>2                                                                    | "Present Status of Characteristics Variability in Advanced MOSFETs"<br>平本 俊郎(東京大学)<br>"Process and Design Differentiations at Ultra-Low-Voltage in UTBB FDSOI 28nm"<br>Phillppe Roche (ST Microelectronics)<br>"Ultralow-Voltage Design and Technology of Silicon-on-Thin-Buried-Oxide (SOTB)<br>CMOS for Highly Energy Efficient Electronics in IoT Era"<br>杉井 信之 (超低電圧デバイス技術研究組合(LEAP))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15:15                                                                                  | や开 信之 (2012年127771753211119578日(LLAF)) (LLAF)) (1277)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15:45                                                                                  | "Reserve to the second |

| セッション<br>3                                                                             | Mehdl B. Tahoorl (Karlsruhe Institute of Technology)<br><i>"30-Gb/s Optical and Electrical Test Solution for High-Volume Testing"</i><br>渡邊 大輔(株式会社アドバンテスト)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |