平成29年度

東京大学 大規模集積システム設計教育研究センター **年報**

# 2017 VLSI Design and Education Center, The University of Tokyo Annual Report

VLSI Design and Education Center The University of Tokyo 2017

### VLSI Design and Education Center The University of Tokyo

This is the 2016 Annual Report of VDEC (VLSI Design and Education Center, University of Tokyo).

Since VDEC was established in 1996, we held "The VDEC 20<sup>th</sup> Anniversary Symposium" on January 20<sup>th</sup> this year. After many warm addresses and messages from representatives of Government, industry and academia including oversee, successful researches and educations were reported from VDEC user universities. We also invited speakers on attractive resent topics in LSI fields. We made a fresh resolve to continue our activities. We also looked back changes in the semiconductor technology and economic situation in the past 20 years, which is almost a half of the LSI history. We thank again many attendees and speakers for success of the symposium.

LSI chip design/implementation in 2016 went well as previous years in general. The use of the 0.8 um CMOS, however, remained low and the use of the 0.18 um CMOS showed decreasing tendency, though the 65 nm SOTB was fine. We decided to reschedule the 0.18 um fabrication runs. We apologize for any inconvenience caused by the schedule change. After this we will guarantee two runs per year for each of 0.8 um and 0.18 um CMOS by restructuring VDEC budget plan for this purpose. And every time when incomes from users reach the cost of another run, we will schedule an additional run. The third run of 0.18 um would be possible so far as the user demands do not decrease so much. The demand of 0.8 um CMOS, however, seems hard to recover. For the time being VDEC will use the chip area for user designs as well as "master slices for QTAT CMOS gate array." This is one week TAT gate array with one metal programing. Though users need a small cost, it is easy to design and will be suitable for student labs. It has been used for the 3<sup>rd</sup> year education in the EE department of our University for long time. Its PDK is ready for use and we will scon make an announcement.

Number of users of the VDEC nano-fabrication facilities is still increasing. The rate of facilities operation and the occupancy of cleanroom are almost 100%. It is a result of a positive feedback that "good conditions of facilities attract new users and new users help to keep good conditions." We will keep the feedback by an appropriate budget to the cleanroom. One of the basis of the budget is "MEXT-JST nanotech-platform project." It is at the turn of the ten-year project. We want to keep the good reputation of the VDEC activities, so as to continue to the next project, too.

VDEC introduced "the cost-sharing system for VDEC academic CAD licenses" last year. The income will be used to partially compensate the constant decrease of VDEC budget from Government for the last 20 years. Now the academic CAD licenses will be provided stably for years. We thank CAD users for understanding. Recent year, however, researches targeting commercial developments are becoming active in academia. The academic CAD licenses are not applicable for these purposes. VDEC has been looking for a possible way to support them. Thanks to understanding of CAD vendors, VDEC could introduce "extended academic CAD licenses" last year, which can be used for the above purposes. The first examples were NEDO projects. We would like to support other industry-academia joint projects, too.

The D2T (Design-to-Test) research division, donated by Advantest Corporation, was renewed last October (the 4<sup>th</sup> term). The 11<sup>th</sup> D2T symposium was successfully held on September 21<sup>st</sup> 2016 and the next symposium is scheduled on September 28<sup>st</sup> of this year. We would like to express our sincere thanks to Advantest Corporation for the continuous support.

We will continue to do our best for the original mission of VDEC, "promotion of education and research in LSI design by means of practical chip-design and implementations", in order to realize research and education for enhancing the value of the semiconductor technology. We thank you for your continuous supports again.

VLSI Design and Education Center, University of Tokyo

Director Kunihiro Asada

KuliAsada

June, 2017

VLSI Design and Education Center, The University of Tokyo Annual Report 2017

# CONTENTS

### **Message from Director of VDEC**

### Chapter 1 Activity Report of VDEC

1.1 Introduction of VDEC activities and activity report of FY2016 ----- 2

· 2

- 1.2 VDEC CAD Tools ----- 5

- 1.3 VLSI Chip Fabrication ----- 7

- 1.4 Seminar ----- 10

- 1.5 Facilities ----- 14

- 1.6 Activity plan for 2017 ----- 16

- 1.7 Venture companies related to VDEC ----- 17

- 1.8 "Nanotechnology Platform" ------ 18 Ultra Small Lithography and Nanometric Observation Site

### Chapter 2

88884

#

- 2.1 Introduction of "ADVANTEST D2T Research Division" ----- 19

- 2.2 Report of "11th D2T Symposium" ----- 20

- 2.3 Research Activity Reports of "Advantest D2T Research Division" ----- 22

- 2.4 Publications ----- 24

| Chapter 3 | Research in VDEC |  |

|-----------|------------------|--|

|-----------|------------------|--|

# Chapter 1 Activity Report of VDEC

1.1 Introduction of VDEC activities and activity report of FY2016

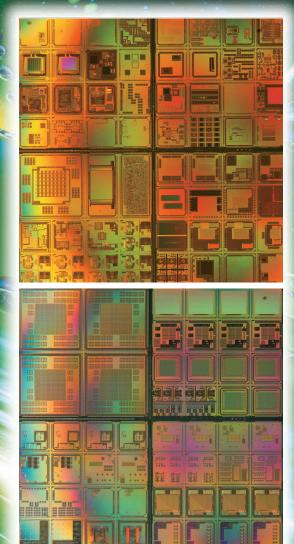

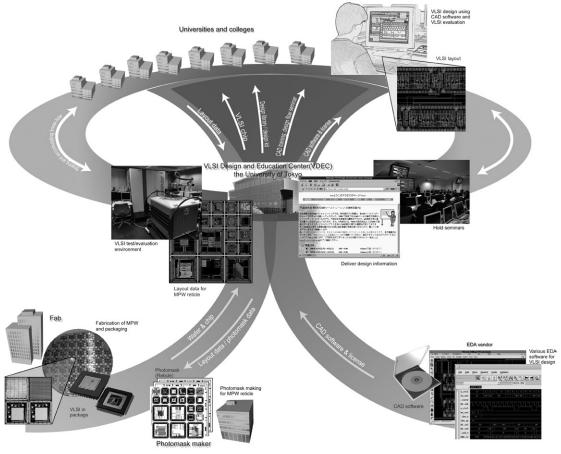

VLSI Design and Education Center(VDEC), University of Tokyo was established in May 1996. VDEC has been operating for the following 3 major roles: "spreading the latest information on VLSI design and education," "providing licenses of CAD tools," and "supporting on VLSI chip fabrications for academic use." The VDEC activity report of FY 2016 is described hereafter according to Fig. 1. 1. 1.

The missions of VDEC are for advancement of researches and education on LSI design in public and private universities and colleges in Japan and send many distinguished VLSI designers into industry. After 19 years of VDEC establishment, educations on CAD software, LSI design and design flow in universities have been well established. On the other hand, advancement on nanometer CMOS technologies forces design flow and CAD software complicated. We have been continuing CAD tool seminar by the lecturers from EDA vendors for twice a year. We hold the seminar in VDEC and provide distance learning through video streaming. We expect spread of the up-to-date LSI design methodology by using CAD tools.

We assume our LSI design flow seminars as educations on basic LSI design concepts and practical experience of LSI design with CAD tool chain. VDEC holds "LSI design education seminar", a.k.a. VDEC Refresh Seminar, once a year. This year we hold 3 courses, "Analog design course" and "RF design course", and initiated "MEMS design course" in July-September time frame. We invite experienced professors among universities as lecturers for the courses to conduct LSI design education courses with practical experience. We also hold "Transistor level design flow in VDEC" and "Digital design flow in VDEC EDA environment" for designers in universities. We started to charge these two LSI design education courses, as well as VDEC Refresh Seminars.

In addition to the above seminars, we hold "VDEC Designer'Forum" among young professors and students annually. This is a workshop that the participants exchange their design examples with not only success stories but also their failure stories, in addition to invited talks. We expect students and professors who will start designs to learn kinds of know-hows. We have initiated "IEEE SSCS Japan Chapter VDEC Design Award" this year, and final examination and awarding have carried out during the "VDEC Designer'Forum". Mr. H. Shiomi(Kyoto Univ.) is awarded as "IEEE SSCS Japan Chapter VDEC Design Award" winner, and Mr. M. Tamura (Univ. of Tokyo), Mr. A. Yoshimura (Nara Institute of Science and Technology), Mr. T. Asano (Kobe Univ.) are awarded as "the best VDEC Design Award", and Mr. T. Kaan (Tokyo Tech), Mr. S. Imanishi (Shizuoka Univ.), Dr. K. Parit (Univ. of Tokyo) are awarded as the "VDEC Design Award." Also Mr. Y. Sato (Shizuoka Univ.), Mr. H. Hayami (NAIST), and W. Nattakarn (NAIST) are awarded as the "VDEC Design Award."

LSI designers come up against various difficulties during actual LSI design scene, even after the basic educations through various seminars and the forum. One of the biggest problems for beginners is the setup of CAD softwares. Many of them also get confused by "Esoteric messages" come out from CAD softwares, even after they successfully setup CAD tools. In such situations, VDEC mailing-lists make significant contributions. VDEC users can register to VDEC mailing-lists on CAD tools, and process dependent groups through VDEC web pages, and can ask questions and helps on their facing issues. It is not a responsibility for the registrant of such mailinglists to give answers to questions, however, in most cases, replies are given by the experienced users of CAD tools and experienced designers within a couple of hours to a couple of days. Moreover, emails are accumulated and are open to the VDEC users, as shown in Fig. 1. 1. 2, who have registered VDEC accounts, as the important educational assets. We expect all the VDEC users to make the full use of this mechanism to help solve problems.

We continue chip fabrication services on FDSOI CMOS 28 nm by ST Microelectronics, 0.18 mm CMOS by Rohm and  $0.8 \,\mu$ m CMOS by On-semi Sanyo Semiconductor. And started chip fabrication services on SOTB CMOS 65 nm by Renesas Electronics.

Our donated division "Design To Test(D2T)", which was founded by donation from Advantest in Oct. 2008, focuses on enrichment of education on LSI testing and bridging between design and testing.

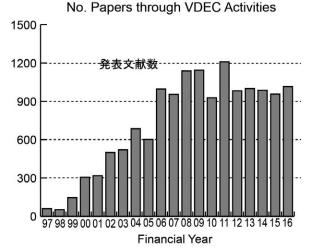

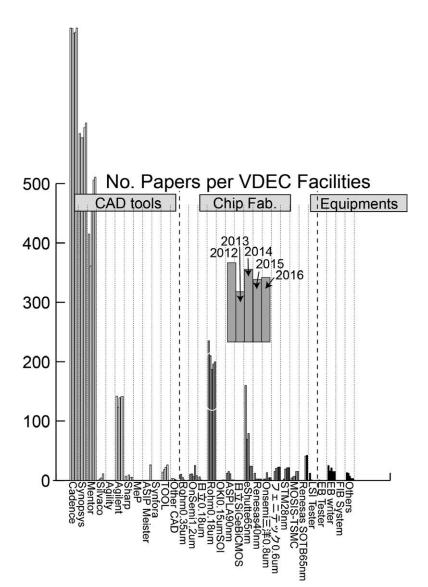

Fig. 1. 1. 3 shows trends of number of papers through VDEC activities. Number of papers is increasing, which means researches in the field of VLSI design have been encouraged after VDEC establishment.

Fig. 1. 1. 4 shows number of papers related to CAD usage, chip fabrications and VDEC facility usages. CAD tools are widely used to write papers. CAD tools are used not only chip designs themselves but also used for preparation of chip fabrication and they contribute to verify fundamental ideas of researches. Advanced CMOS processes are preferred for publications, and not only papers with 65 nm/40 nm CMOS chips, but also with 32 nm CMOS, 22 nm CMOS and 14 nm CMOS are emerging in the world. We would like to prepare chip fabrication services for the advanced CMOS processes. In

| レス(D) (創 http://www.                                    | /dec.u=tukyu.ac.jp/                                  |                                               |                                  |                                     |                            |                                                    | ▶ → 移動                                                   | 」 リンク ※ 電                                                     |

|---------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|----------------------------------|-------------------------------------|----------------------------|----------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------|

|                                                         |                                                      | 1                                             | ) 2 4 VDE                        | Co~-                                | 22                         |                                                    |                                                          |                                                               |

| 新着情報                                                    | アカウント登録                                              | チップ試作                                         | 設計CAD                            | 装置利用                                | 案内                         | 関連リンク                                              | 内部情報                                                     | English                                                       |

| ▲<br>く利用される<br>ページー覧                                    |                                                      | 設計                                            | 者のメー                             | ールリス                                | ストのi                       | 過去の                                                | 記事                                                       |                                                               |

| はじめての方へ                                                 | Last update                                          | ed: 03/05/200                                 | 6 02:37:25                       |                                     |                            |                                                    |                                                          |                                                               |

|                                                         | った場合の                                                | プ試作において、<br>参考にして下さい<br>した方に限ってお              | い。(ただしいす                         |                                     |                            |                                                    |                                                          |                                                               |

| 計作MLへの登<br>計算作ML過去記                                     |                                                      | 利用者]全文格<br>CAD利用者チッ                           |                                  | <u>順)</u> ## <u>(スレ</u>             | <u>ッド順)</u> ## <u>(</u>    | <u>全文)</u>                                         |                                                          |                                                               |

| <u>目立サービス</u><br>/ケットボード情報<br>Fップ試作と支払<br>況一覧           | <ul> <li>00年月</li> <li>00年月</li> </ul>               | ローラ/オンセミ<br>変第1回モトロー<br>変第2回モトロー<br>変第1回モトロー  | ラ/オンセミコン<br>ラ/オンセミコン             | ダクタ 1.2u                            | ーー<br>mチップ試化<br>mチップ試化     | (日付順)                                              | ## (スレッド順                                                | )## (全文)                                                      |

| 4 <i>D関係</i><br>AD利用案内<br>DECからの御願い<br>iイセンスファイル<br>配布  | <ul> <li>01年月</li> <li>02年月</li> <li>02年月</li> </ul> | 度第2回モトロー<br>度第1回モトロー<br>度第2回モトロー<br>を第1回モトロー  | ラ/オンセミコン<br>ラ/オンセミコン<br>ラ/オンセミコン | /ダクタ 1.2u<br>/ダクタ 1.2u<br>/ダクタ 1.2u | mチップ試化<br>mチップ試化<br>mチップ試化 | ⊧ <u>(日付順)</u><br>⊧ <u>(日付順)</u><br>⊧ <u>(日付順)</u> | ## <u>(スレッド順</u><br>## <u>(スレッド順</u><br>## <u>(スレッド順</u> | <u>)</u> ## <u>(全文)</u><br>)## <u>(全文)</u><br>)## <u>(全文)</u> |

| ADアクセスホスト<br><u>エック!</u><br>ADuserMLの登                  | • 03年<br>• 04年<br>• 04年                              | 変第2回モトロー<br>変第1回モトロー<br>変第2回モトロー              | ラ/オンセミコン<br>ラ/オンセミコン<br>ラ/オンセミコン | ・ダクタ 1.2u<br>・ダクタ 1.2u<br>・ダクタ 1.2u | mチップ試化<br>mチップ試化<br>mチップ試化 | ⊧ <u>(日付順)</u><br>⊧ <u>(日付順)</u><br>⊧ <u>(日付順)</u> | ## <u>(スレッド順</u><br>## <u>(スレッド順</u><br>## <u>(スレッド順</u> | )## <u>(全文)</u><br>)## <u>(全文)</u><br>)## <u>(全文)</u>         |

| <u>ADuserMLの過</u><br>記事<br>AD講習会案内<br>AD講習会データ<br>DEC教材 | <ul> <li>05年月</li> <li>96年月</li> </ul>               | 変第1回モトロー<br>変第2回モトロー<br>変モトローラ/オ)<br>変第1回モトロー | ラ/オンセミコン                         | ダクタ 1.2u                            | mチップ試作<br>プ試作(日1           | ⊧ <u>(日付順)</u><br>対順)##(ス                          | ## (スレッド順)                                               | <u>)</u> ## <u>(全文)</u><br>全文)                                |

| していません<br>当版サポートサー<br>ス                                 | • 97年月                                               | 要第2回モトロー<br>要第1回モトロー                          | ラ/オンセミコン                         | ダクタ 1.2u                            | mチップ試化                     | F(日付順)                                             | ## (スレッド順                                                | )## (全文)                                                      |

Fig. 1. 1. 2 Archives of emails of VDEC mailing-list.

addition, we would like to setup chip fabrication services related to CMOS/MEMS to fulfill the researches for "More than Moore". We also encourage researchers to fully use of VDEC facilities such like LSI testers, FIB systems and EB writer for the wide spread of research purposes.

Fig. 1. 1. 4 Number of papers related to VDEC facilities.

# 1.2 VDEC CAD Tools

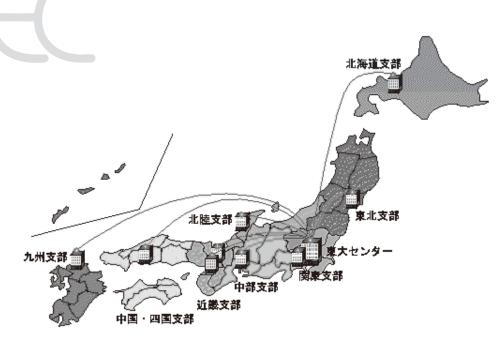

Since 1996, VDEC has provided CAD software licenses to the registered researchers in universities and colleges in Japan. The CAD tools we provided in 2017 are shown in Table 1. 2. 1. The researchers can use those CAD tools when their local machines, whose IP addresses are registered in advance, are authorized by one of VDEC license server located in the ten VDEC subcenters shown in Fig. 1. 2. 1. For each CAD tool, VDEC provides 10-100 floating licenses. Those CAD tools can be utilized only for research and education activities in national universities, other public universities, private universities, and

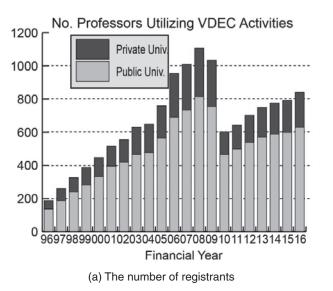

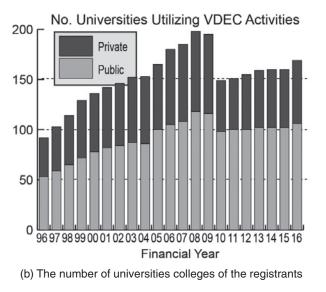

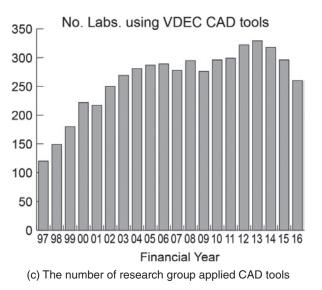

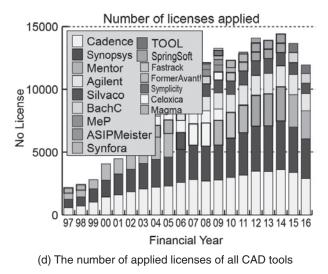

When one is going to use VDEC CAD tools and chip fabrication service (the details are described in Section 1-3), some faculty member of his/her research group in a university or a collage needs to do user registration. Fig. 1. 2. 2 shows (a) the number of registrants, (b) the number of distinguished universities/colleges of the registrants, and (c) the number of registrants who applied VDEC CAD tools.

| Table 1. 2. 1 VDEC CAD tools |                                                                                                                                                                                                                                                                      |                              |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

| Name                         | Function                                                                                                                                                                                                                                                             | Vendor                       |  |  |

| Cadence tool set             | Verilog-HDL/VHDL entry, Simlation, Logic synthesis, Test<br>pattern generation, Cell-based (including macros) place,<br>route, and back-annotation, Interactive schematic and<br>layout editor, Analog circuit simulation, Logic verification,<br>Circuit extraction | Cadence Design Systems, Inc. |  |  |

| Synopsys tool set            | Verilog-HDL/VHDK simulation, Logic synthesis, Test pat-<br>tern generation, Cell-based (including macros) place, route,<br>and back-annotation, Circuit simulation, Device simulation                                                                                | Synopsys, Inc.               |  |  |

| Mentor tool set              | Layout verification, Design rule check                                                                                                                                                                                                                               | Mentor Graphics Co. Ltd.     |  |  |

| Silvaco tool set             | Fast circuit simulation                                                                                                                                                                                                                                              | Silvaco                      |  |  |

| ADS/Golden Gate              | Design and verification of high-frequency circuits                                                                                                                                                                                                                   | Keysight Technologies        |  |  |

| Bach system                  | BachC-based design, synthesis, and verification                                                                                                                                                                                                                      | Sharp                        |  |  |

| LAVIS                        | Layout visualization platform                                                                                                                                                                                                                                        | TOOL                         |  |  |

Fig. 1. 2. 1 VDEC Subcenters

Fig. 1. 2. 2 The numbers of VDEC CAD Applications

### 1.3.1 Trends of VLSI Chip Fabrication Services

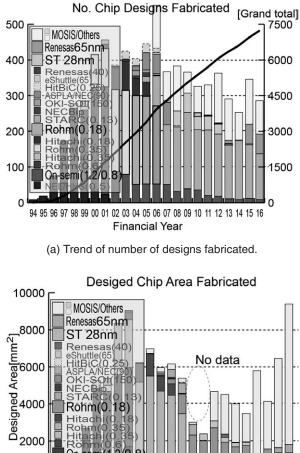

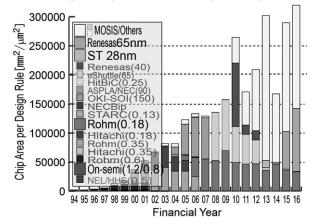

Fig. 1. 3. 1 shows a trend of number of designed chips for VDEC chip fabrication services, including pilot project prior to VDEC establishment.

VLSI chip fabrication is limited to 0.5 mm CMOS provided by NTT Electronics during the pilot project in 1994 and 1995. VDEC chip fabrication had started in 1996 with 1.2 mm CMOS provided by Motorola Japan, which is now On-Semiconductor as well as the 0.5 mm CMOS. In 1997, VDEC received cooperation from Rohm and has started 0.6 mm CMOS process. In 1998, VDEC started chip fabrication services of 0.35 mm CMOS by Hitachi, and in 1999, VDEC started 0.35 mm CMOS by Rohm. We had a test chip fabrication of 0.13 mm CMOS by STARC through "IP development project" in 2001. We added 0.18 mm CMOS by Hitachi into our chip fabrication menu in 2001. From 2002, we started VDEC-MOSIS chip fabrication program initiated by Prof. Iwata of Hiroshima University. Under this program, VDEC member can access to TSMC and IBM processes with lower price. We also started Bipolar chip fabrication by NEC Compound Semiconductor Devices. In 2004, we started 0.15 mm SOI-CMOS chip fabrication by Oki Electric as test chip fabrications. In the same year we started 90 nm CMOS chip fabrication by ASPLA/STARC. In 2006, we started 0.18 mm CMOS by Rohm and 0.25 mm SiGeBiCMOS by Hitachi. In 2008, we started 65 nm CMOS process by eShuttle, after closure of 90 nm CMOS chip fabrication in 2007. In 2010, we started 40 nm CMOS process by Renesas Electronics through "Next Generation Semiconductor Circuits & Architecture" project between METI and STAR. On the other hand, 1.2 mm CMOS chip fabrication program came to end by the September 2011. 40 nm CMOS by Renesas Electronics and 65 nm by eShuttle also come to end by Oct. 2012 and Aug. 2013, respectively. We started CMOS0.8 µm in Oct. 2012 by On-semiconductor-Sanyo as a test chip fabrication and opened it as the regular chip fabrication menu in 2012. We started FD-SOI 28 nm CMOS by ST-Microelectronics through CMP, France, as the advanced CMOS process in 2013. We started SOTB 65 nm CMOS by Renesas Electronics in 2015.

Fig. 1. 3. 1(a) shows trends of number of chip designed for VDEC chip fabrication. For the first 6 years until 2001, the number of designed chips shows steady increase, which means drastic improve of the effectiveness researches and education of LSI design, and we assume drastic increase of number of students related to LSI chip

000 Rôhm (0.18) Hitach (0.18) Hitach (0.35) On-sem (1.2/0.8) 94 95 96 97 98 99 00 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 Financial Year

(b) Trend of designed area.

Desiged Chip Area Fabricated per Design Rule

(c) Trend of designed area normalized by design rule.

design and education. During few years of stable number around 400 chip designs per year, we can see transition of designs toward finer process. In 2007, we saw a large drop, which was caused by sudden process transition from 0.35 mm CMOS to 0.18 mm CMOS, and in 2008, we also saw another drop by process transition from 90 nm CMOS to 65 nm CMOS.

Fig. 1. 3. 1(b) shows trends of designed chip area, which shows much clear trends of drop by process migration. On the other hand, Fig. 1. 3. 1(c) shows trends of designed chip area normalized by design rule, which assume to be strong relation with design efforts. Coming from the fact that the normalized chip area is still growing, we assume the major reason for decrease of number of chips and designed area is increase of design effort per chip and per unit area due to process scaling.

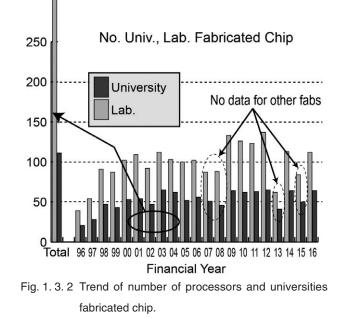

Fig. 1. 3. 2 shows trends number of professors and universities fabricated chip. Number of professors who have contracted NDA for process technologies to access design rules and design libraries are, 72, 274, and 38, respectively, for 65 nm CMOS, 0.18 mm CMOS, and 0.8 um CMOS.

### Table 1.3.1 Chip fabrication schedule in 2016 O 0.8 mm CMOS (On-Semiconductor - Sanvo)

### 1.3.2 Overview of chip fabrication in 2015

Table 1. 3. 1 lists chip fabrication schedule in 2015. Please refer to list in Chapter 2 for details of designers and contents of chip designed.

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2016 #1 | 2016/ 7/ 8                | 2016/ 9/30      | 2017/ 2/ 9    |

| 2016 #2 | 2016/12/30                | 2017/ 3/24      | 2016/ 6/20    |

#### ○ 0.18 mm CMOS (Rohm)

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2016 #1 | 2016/ 3/ 7                | 2016/ 5/30      | 2016/ 9/20    |

| 2016 #2 | 2016/ 5/ 2                | 2016/ 7/25      | 2016/11/14    |

| 2016 #3 | 2016/ 6/28                | 2016/10/17      | 2016/12/27    |

| 2016 #4 | 2016/11/28                | 2017/ 2/20      | 2017/ 6/16    |

#### ○ SOTB 65 nm CMOS

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2016 #1 | 2016/ 5/23                | 2016/ 7/ 4      | 2017/ 2/20    |

| 2016 #2 | 2016/12/12                | 2017/ 1/23      | 2017/ 8M      |

### 1.3.3 Libraries and design flows

and design flows for digital design and PDKs for analog design. Table 1. 3. 2 lists libraries available now.

VDEC have been working to prepare design libraries

| Technology   | Name               | Author                                                                     | Contents                |

|--------------|--------------------|----------------------------------------------------------------------------|-------------------------|

| 0.18 mm CMOS | Rohm library       | Rohm Library                                                               | Synthesis(Synopsys)     |

| (Rohm)       |                    | Std. Cells, IO cells, RAM<br>(Distributed with CDROM)                      | Simulation (VerilogXL)  |

|              |                    |                                                                            | P&R(LEF/DEF)            |

|              | Kyodai Library     | Onodera Lab., Kyoto University                                             | Synthesis(Synopsys)     |

|              | Todai Library VDEC |                                                                            | Simulation (VerilogXL)  |

|              |                    |                                                                            | P&R(Astro)              |

|              |                    |                                                                            | Synthesis(RTL Compiler) |

|              |                    | Design flow based on library prepared by<br>Onodera Lab., Kyoto University | Simulation (VerilogXL)  |

|              |                    |                                                                            | P&R(Encounter)          |

|              | PDK                | VDEC                                                                       | PDK(IC6.1)              |

Table 1. 3. 2 Libraries available for VDEC chip fabrication

### 1.4 Seminar

Seminar is indispensable for the improvement of LSI design technology. Some seminar and forums, such as technical seminar for CAD use, refreshing seminar for working people, designer's forums for young professors and students were held in 2016.

### [Technological seminar for CAD use]

In a technological seminar for CAD use, VDEC invites lecturer from each tool vender, such as Cadence, Synopsys and Agilent, to hold the CAD operation course. Moreover, the course concerning the design flow in the VDEC environment was held by the VDEC staff. A technological seminar for CAD use for the beginner was held in The University of Tokyo VDEC in August and September at the year 2016. This seminar took 5 days for 2 kinds of Cadence tools, 3 days for 2 kinds of Synopsys tools, 1 days for 1 kind of Keysight tool. In addition,

VDEC teachers gave lecturers on transistor level circuit design course, and digital circuit design course under the VDEC EDA environment. Teachers and students up to 40 people attended a lecture in each course, and master the use of each tool for VLSI design flow that uses the VDEC library. Moreover, another technical seminar for CAD use for matured teachers and students was held in March by Cadence 2 kind and 5 days, Synopsys 3 kinds and 4 days (Table 1.4.1). The demand for these CAD technological seminars is very large, and VDEC has maintained the mechanism of a large-scale CAD technological seminar holding corresponding to this situation. So far, the seminar was held at the University of Tokyo OR other VDEC branch, however, we started to distribute the lecture using Web streaming, so that students around VDEC branch can take the seminar at the branch school.

| Table 1. 4. 1 CAD to | echnological seminar in summer of the year 2016 |                 |    |

|----------------------|-------------------------------------------------|-----------------|----|

| 2016/08/02           | Keysight Empro Seminar                          | Univ. of Tokyo  | 13 |

| 2016/08/02           | Keysight Empro Seminar                          | Hokkaido Univ.  | 2  |

| 2016/08/02           | Keysight Empro Seminar                          | Kanazawa Univ.  | 1  |

| 2016/08/03-04        | Synopsys DesignCompiler+PowerCompilerSeminar    | Univ. of Tokyo  | 9  |

| 2016/08/03-04        | Synopsys DesignCompiler+PowerCompilerSeminar    | Hokkaido Univ.  | 2  |

| 2016/08/03-04        | Synopsys DesignCompiler+PowerCompilerSeminar    | Tohoku Univ.    | 4  |

| 2016/08/03-04        | Synopsys DesignCompiler+PowerCompilerSeminar    | Osaka Univ.     | 5  |

| 2016/08/30-31        | Cadence Virtuoso ADE Seminar                    | Univ. of Tokyo  | 16 |

| 2016/08/30-31        | Cadence Virtuoso ADE Seminar                    | Hokkaido Univ.  | 3  |

| 2016/08/30-31        | Cadence Virtuoso ADE Seminar                    | Tohoku Univ.    | 5  |

| 2016/08/30-31        | Cadence Virtuoso ADE Seminar                    | Kanazawa Univ.  | 2  |

| 2016/08/30-31        | Cadence Virtuoso ADE Seminar                    | Kyoto Univ.     | 2  |

| 2016/08/30-31        | Cadence Virtuoso ADE Seminar                    | Hiroshima Univ. | 3  |

| 2016/09/01           | Synopsys HSPICE Seminar                         | Univ. of Tokyo  | 12 |

| 2016/09/01           | Synopsys HSPICE Seminar                         | Hokkaido Univ.  | 2  |

| 2016/09/01           | Synopsys HSPICE Seminar                         | Tohoku Univ.    | 4  |

| 2016/09/01           | Synopsys HSPICE Seminar                         | Kanazawa Univ.  | 2  |

Table 1. 4. 1

CAD technological seminar in summer of the year 2016

| 2016/09/01    | Synopsys HSPICE Seminar          | Kyoto Univ.     | 3  |

|---------------|----------------------------------|-----------------|----|

| 2016/09/01    | Synopsys HSPICE Seminar          | Osaka Univ.     | 3  |

| 2016/09/01    | Synopsys HSPICE Seminar          | Hiroshima Univ. | 2  |

| 2016/09/05-07 | Cadencee Virtuoso Layout Seminar | Univ. of Tokyo  | 26 |

| 2016/09/05-07 | Cadencee Virtuoso Layout Seminar | Hokkaido Univ.  | 3  |

| 2016/09/05-07 | Cadencee Virtuoso Layout Seminar | Tohoku Univ.    | 3  |

| 2016/09/05-07 | Cadencee Virtuoso Layout Seminar | Kanazawa Univ.  | 2  |

| 2016/09/05-07 | Cadencee Virtuoso Layout Seminar | Osaka Univ.     | 3  |

| 2016/09/05-07 | Cadencee Virtuoso Layout Seminar | Hiroshima Univ. | 1  |

| Cadence Allegro Design Entry Front to Back Seminar | Univ. of Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cadence Allegro Design Entry Front to Back Seminar | Hokkaido Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cadence Allegro Design Entry Front to Back Seminar | Tohoku Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys XA-VCS CoSim Seminar                      | Univ. of Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Synopsys XA-VCS CoSim Seminar                      | Hokkaido Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys XA-VCS CoSim Seminar                      | Osaka Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys XA-VCS CoSim Seminar                      | Hiroshima Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys IC Compiler Seminar                       | Univ. of Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Synopsys IC Compiler Seminar                       | Hokkaido Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys IC Compiler Seminar                       | Osaka Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys IC Compiler Seminar                       | Hiroshima Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys HSPICE+VerilogA Seminar                   | Univ. of Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Synopsys HSPICE+VerilogA Seminar                   | Hokkaido Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys HSPICE+VerilogA Seminar                   | Kyoto Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synopsys HSPICE+VerilogA Seminar                   | Hiroshima Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cadence Encounter Digital Implementation Seminar   | Univ. of Tokyo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cadence Encounter Digital Implementation Seminar   | Hokkaido Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cadence Encounter Digital Implementation Seminar   | Osaka Univ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    | Cadence Allegro Design Entry Front to Back SeminarCadence Allegro Design Entry Front to Back SeminarSynopsys XA-VCS CoSim SeminarSynopsys IC Compiler SeminarSynopsys HSPICE+VerilogA Seminar | Cadence Allegro Design Entry Front to Back SeminarHokkaido Univ.Cadence Allegro Design Entry Front to Back SeminarTohoku Univ.Synopsys XA-VCS CoSim SeminarUniv. of TokyoSynopsys XA-VCS CoSim SeminarHokkaido Univ.Synopsys XA-VCS CoSim SeminarOsaka Univ.Synopsys XA-VCS CoSim SeminarOsaka Univ.Synopsys XA-VCS CoSim SeminarUniv. of TokyoSynopsys XA-VCS CoSim SeminarUniv. of TokyoSynopsys XA-VCS CoSim SeminarUniv. of TokyoSynopsys IC Compiler SeminarUniv. of TokyoSynopsys IC Compiler SeminarOsaka Univ.Synopsys IC Compiler SeminarOsaka Univ.Synopsys IC Compiler SeminarUniv. of TokyoSynopsys IC Compiler SeminarUniv. of TokyoSynopsys HSPICE+VerilogA SeminarUniv. of TokyoSynopsys HSPICE+VerilogA SeminarKyoto Univ.Synopsys HSPICE+VerilogA SeminarHiroshima Univ.Synopsys HSPICE+VerilogA SeminarHiroshima Univ.Synopsys HSPICE+VerilogA SeminarKyoto Univ.Synopsys HSPICE+VerilogA SeminarHiroshima Univ.Cadence Encounter Digital Implementation SeminarUniv. of TokyoCadence Encounter Digital Implementation SeminarHokkaido Univ. |

### [Refresh Seminar for Working People]

Teachers of universities and designers in the first line of the enterprise were invited to the lecturer at "VLSI design refresh seminar" was held aiming at the latest, advanced knowledge and technical learning concerning VLSI design as a refreshing education for working people involved in the integrated circuit industry (Table 1. 4. 2). Though this seminar started chiefly in year 1998 under the support of Ministry of Education Technical Education Division to give practicing education of the latest VLSI design technology, it continues under many supports from many societies.

Course A: analog integrated circuit design (7/11 -13), Course M1: MEMS design (7/4-5), Course M2:MEMS fabrication (7/25-7/27), and Course R: RF circuit design (7/27-28). Teachers from industry and universities involved in the integrated circuit research and the education were invited as the lecturer, and they introduced a state-of-the-art VLSI design technology including the practice using a lecture concerning VLSI design and the latest CAD tool. The participants for the course A, M1, M2, R were 18, 8, 6, 7, respectively.

Fig. 1. 4. 1 Refresh Seminar at VDEC seminar room at the University of Tokyo, VDEC.

#### Table 1. 4. 2 Refresh Seminar

Course A: Analog Circuit Design (3 days)

Analog Circuit Design and simulation Integrated Circuits Verification (LVS, DRC)

Masahiro Sugimoto (Chuo Univ.), Hidetoshi Onodera (Kyoto Univ.), Koji Kotani (Tohoku Univ.)

Course M1: MEMS Design (2 days)

MEMS Basic 1: Fabrication Process MEMS Basic 2: Operation Principle Structual Design Layout Design

Yoshio Mita (Univ. of Tokyo)

Course M2: MEMS Fabrication (3 days)

CAD Design and Analysis Lithography, Etching, Release Vibration measurement and analysis

Yoshio Mita (Univ. of Tokyo)

Course R: CMOS-RF Circuit Design (3days)

Modulation/Demodulation, Cascaded connection Basic Performace, Tranceiver Architecture Circuit Element, Design Flow

Hiroyuki Ito (Tokyo Institute of Technology)

# [Designer's forum for young teachers and students]

VDEC LSI designer forum intended for students and young teachers has been held. The VDEC LSI designer forum has aimed to sharing information that cannot be obtained at a society and a academic society, for example, the failure case and the solution in which LSI designer has a hard time, the inside story of CAD industry, the construction method in the design milieu in the laboratory, and so on. This year, we had the meeting in Takeda Hall in The University of Tokyo, in August. No less than 50 participants were flourishing at the gathering.

Table 1.4.3 Program of Designers Forum in 2015

8/25(Thu)

| 8/25(Thu)   |                                                                                            |

|-------------|--------------------------------------------------------------------------------------------|

| Time        |                                                                                            |

| 9:30-10:00  | Reception                                                                                  |

| 10:00-11:00 | Prenary Talk<br>Kazuhiko Takagawara (NTT)<br>Vital Sensing Technology by Wearable Devices. |

| 11:00-12:00 | VDEC Design Award Presentation                                                             |

| 12:00-13:00 | lunch                                                                                      |

| 13:00-15:00 | VDEC Design Award Presentation                                                             |

| 15:00-15:20 | break                                                                                      |

| 15:20-18:20 | VDEC Design Award Presentation                                                             |

| 19:00-      | VDEC Design Award award ceremony                                                           |

|             |                                                                                            |

#### 8/26(Fri)

| Time        |                                               |

|-------------|-----------------------------------------------|

| 9:00-12:00  | Ph.D Session                                  |

| 12:00-13:00 | lunch                                         |

| 13:00-15:00 | VDEC Design Award Idea Contest Presentation   |

| 15:00-15:20 | break                                         |

| 15:20-16:50 | VDEC Design Award Idea Contest Presentation   |

| 17:00-      | VDEC Design Award Idea Contest award ceremony |

### 1.5 Facilities

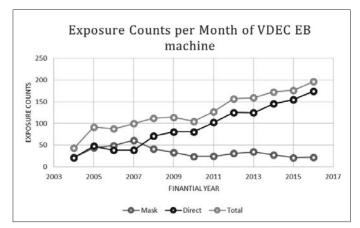

The VDEC has provided the big facilities for universities in Japan from its establishment (1996). Big facilities refer to those which are impossible to acquire and or maintain by an individual research unit. Table 1.5.1 shows the available facilities of VLSI testers and some process machines, which are placed at the tester room and the super clean room of the Takeda building. In 2004, the VLSI tester (T2000) and the EB lithography machine (F5112+VD01) were donated to the VDEC by the ADVANTEST. In the year 2012, VDEC joined MEXT (Ministry of Education)'s Nanotechnology platform to enforce its multi-use capability. (For Nanotechnology Platform refer section 1.8). From April 2015 to March 2016, the EB lithography machine F5112 has been used 1317 times. The reason of slight decrease of number since last year (89 times less from 1406 in 2015) can be attributed to user shift to new EB apparatus. The exposure count of the new apparatus (F7000S-VD02) was increased to 1042 times that is +333 increase from last year (709 exposures in 2015). Total exposure number of EB machines have therefore increased from 2115 (in 2015) to 2359 (+244).

The facilities can be used by user himself, after a couple of times'training by attendance of licensed users; also, by presence of licensed persons, a new user can readily use the machine.

| Facility                             | Equipment name                                                            | Description                                                                                                                                                            | Status    | Contact                           |

|--------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------|

| Logic LSI<br>test System             | EB tester:<br>IDS10000                                                    | The chip surface voltage during operation<br>can be measured with the LST tester.<br>The digital circuit with 384 pins, 1 GHz can<br>be tested.                        | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                      | LSI tester:<br>ADVANTEST T2000                                            | The digital circuit with 256 pins, 512 MHz can be tested. Analog test is optional.                                                                                     | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                      | Auto prober:<br>PM-90-A                                                   | Automated prober for testing LSI wafers,<br>which can be used with the LSI testers. The<br>probe card for LSIs with the VDEC standard<br>pin connections is available. | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

| Analog/RF<br>measure-<br>ment system | Analog/RF measurement<br>system:<br>B1500A, 4156B, HP4284,<br>etc         | DC parameter measurement, Capacitance<br>measurement, Network analyzer, Spectrum<br>analyzer, etc.                                                                     | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |