東京大学 大規模集積システム設計教育研究センター 年報

# 2018 VLSI Design and Education Center, The University of Tokyo Annual Report

VLSI Design and Education Center The University of Tokyo 2018

## VLSI Design and Education Center The University of Tokyo

I was appointed as director of VLSI Design and Education Center (VDEC) on April 1 following the director, Prof. Asada. VDEC was established in May 1996, and has been operating for 22 years. The first director, Prof. Hoh and the previous director, Prof. Asada have made VDEC as one of the most important and widely used organizations in Japanese academia for VLSI chip design and development. Annually around 300 research groups in academia use the design tools provided through VDEC, and nearly 200 research groups use various facilities including clean rooms and measurement tools for chip development.

Semiconductor industry has been continuously growing since the last century and is expected to continue to grow with the increasing need from IoT and related technology. It is extremely important to support academia as it is the basis of semiconductor industry. There are several organizations in the world, specifically in US, Canada, Europe, South Korea, and Taiwan, and others, whose goals are basically the same as VDEC. There have been efforts in the collaboration among these organizations. Every year, multiple meetings to discuss collaborative ways to supply various services for world-wide VLSI chip design and development are set up, and more intensive joint activities are expected to come.

D2T (Design to Test) which is an industry donated division in VDEC has been working for ten years and has received a number of world top-level visiting professors. D2T has already stimulated educational and research activities of VLSI testing in broad sense and has generated several results which have actually influenced the VLSI testing area world-wide. It is expected to continue to generate more influential results in VLSI design and testing.

VDEC is an essential organization for academic VLSI design and development. Now it is planned to expand to include not only just chip development, but also ICT system developments through tighter collaboration with various resources in information technology. With that goal in mind, VDEC continues to work for more efficient ways of chip and system developments, EDA tools which can be used commercial chips, and integration of VLSI chip and device developments. VDEC including myself appreciates your continuous support.

> VLSI Design and Education Center, University of Tokyo Director Masahiro Fujita

藤田昌宏

## **Message from Director of VDEC**

## Chapter 1 Activity Report of VDEC 2

- 1.1 Introduction of VDEC activities and activity report of FY2017 ----- 2

- 1.2 VDEC CAD Tools ----- 5

- 1.3 VLSI Chip Fabrication ----- 7

- 1.4 Seminar ----- 10

- 1.5 Facilities ----- 13

- 1.6 Activity plan for 2018 ----- 15

- 1.7 Venture companies related to VDEC ----- 16

- 1.8 "Nanotechnology Platform" ----- 17 Ultra Small Lithography and Nanometric Observation Site

## Chapter 2 Activity Report of "ADVANTEST D2T Research Division" 18

- 2.1 Introduction of "ADVANTEST D2T Research Division" ----- 18

- 2.2 Report of "12th D2T Symposium" ----- 19

- 2.3 Research Activity Reports of "Advantest D2T Research Division" ----- 21

- 2.4 Publications ----- 23

## Chapter 3 Research in VDEC 24

# **Chapter 1** Activity Report of VDEC

1.1 Introduction of VDEC activities and activity report of FY2017

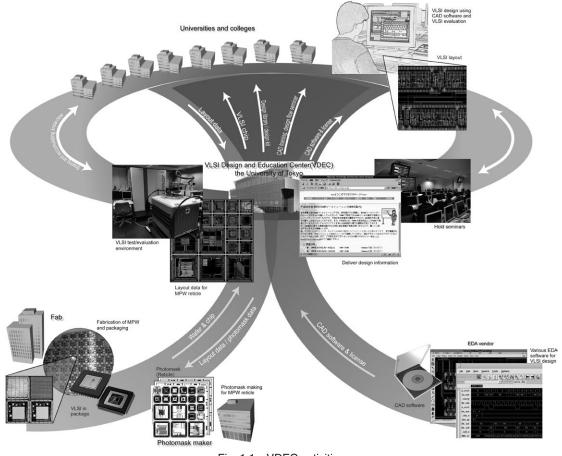

VLSI Design and Education Center(VDEC), University of Tokyo was established in May 1996. VDEC has been operating for the following 3 major roles: "spreading the latest information on VLSI design and education," "providing licenses of CAD tools," and "supporting on VLSI chip fabrications for academic use." The VDEC activity report of FY 2017 is described hereafter according to Fig. 1.1.

The missions of VDEC are for advancement of researches and education on LSI design in public and private universities and colleges in Japan and send many distinguished VLSI designers into industry. After 22 years of VDEC establishment, educations on CAD software, LSI design and design flow in universities have been well established. On the other hand, advancement on nanometer CMOS technologies forces design flow and CAD software complicated. We have been continuing CAD tool seminar by the lecturers from EDA vendors for twice a year. We hold the seminar in VDEC and provide distance learning through video streaming. We expect spread of the up-to-date LSI design methodology by using CAD tools.

We assume our LSI design flow seminars as educations on basic LSI design concepts and practical experience of LSI design with CAD tool chain. VDEC holds "LSI design education seminar", a.k.a. VDEC Refresh Seminar, once a year. This year we hold 3 courses, "Analog design course" and "RF design course", and initiated "MEMS design course" in July-September time frame. We invite experienced professors among universities as lecturers for the courses to conduct LSI design education courses with practical experience. We also hold "Transistor level design flow in VDEC" and "Digital design flow in VDEC EDA environment" for designers in universities. We started to charge these two LSI design education courses, as well as VDEC Refresh Seminars.

In addition to the above seminars, we hold "VDEC Designer'Forum" among young professors and students annually. This is a workshop that the participants exchange their design examples with not only success stories but also their failure stories, in addition to invited talks. We expect students and professors who will start designs to learn kinds of know-hows. We have initiated "IEEE SSCS Japan Chapter VDEC Design Award" this year, and final examination and awarding have carried out during the "VDEC Designer' Forum". Mr. H. Asano(Kobe Univ.) is awarded as "IEEE SSCS Japan Chapter VDEC Design Award" winner, and Mr. H. Asano(Kobe Univ.), Mr. K. Fujimoto(Nara Institute of Science and Technology), Mr. Y. Matsushita(Keio Univ.)) are awarded as "the best VDEC Design Award", and Mr. T. Yamaguchi (Nara Institute of Science and Technology), Mr. H. Hayami(Nara Institute of Science and Technology), Mr. H. Sun(Waseda Univ.) are awarded as the "VDEC Design Award." Also Mr. D. Terutsuki(Univ. of Tokyo) are awarded as the "VDEC Design Award."

LSI designers come up against various difficulties during actual LSI design scene, even after the basic educations through various seminars and the forum. One of the biggest problems for beginners is the setup of CAD softwares. Many of them also get confused by "Esoteric messages" come out from CAD softwares, even after they successfully setup CAD tools. In such situations, VDEC mailing-lists make significant contributions. VDEC users can register to VDEC mailing-lists on CAD tools, and process dependent groups through VDEC web pages, and can ask questions and helps on their facing issues. It is not a responsibility for the registrant of such mailinglists to give answers to questions, however, in most cases, replies are given by the experienced users of CAD tools and experienced designers within a couple of hours to a couple of days. Moreover, emails are accumulated and are open to the VDEC users, as shown in Fig. 1.2, who have registered VDEC accounts, as the important educational assets. We expect all the VDEC users to make the full use of this mechanism to help solve problems.

We continue chip fabrication services on FDSOI CMOS 28 nm by ST Microelectronics, 0.18 mm CMOS by Rohm and  $0.8 \,\mu$ m CMOS by On-semi Sanyo Semiconductor. And started chip fabrication services on SOTB CMOS 65 nm by Renesas Electronics.

Our donated division "Design To Test(D2T)", which was founded by donation from Advantest in Oct. 2008, focuses on enrichment of education on LSI testing and bridging between design and testing.

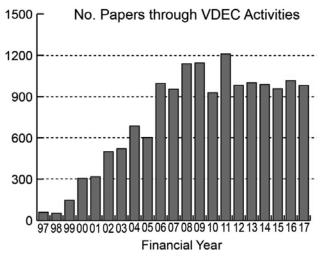

Fig. 1.3 shows trends of number of papers through VDEC activities. Number of papers is increasing, which means researches in the field of VLSI design have been encouraged after VDEC establishment.

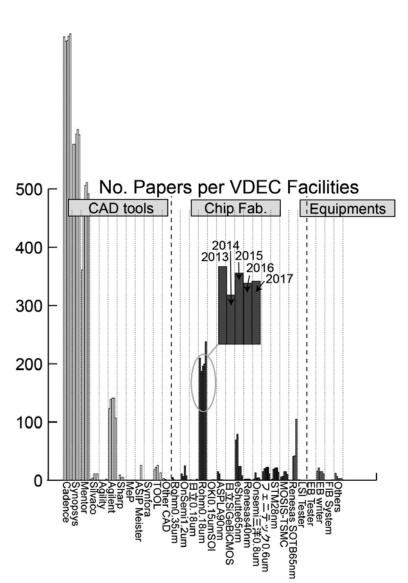

Fig. 1.4 shows number of papers related to CAD usage, chip fabrications and VDEC facility usages. CAD tools are widely used to write papers. CAD tools are used not only chip designs themselves but also used for preparation of chip fabrication and they contribute to verify fundamental ideas of researches. Advanced CMOS processes are preferred for publications, and not only papers with 65 nm/40 nm CMOS chips, but also with 32 nm CMOS, 22 nm CMOS and 14 nm CMOS are emerging in the world. We would like to prepare chip fabrication services for the advanced CMOS processes. In addition, we would

| アドレス① 🖉 http://www.                                                                                                                | rdecu-tokya.acja/ 🔄 🗃 移動   リンク » 🐑 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 新着情報                                                                                                                               | ようこそVDECのページへ<br>アカウント会秘 チップ記作 設計CAD 装置利用 案内 間違リンク 内部情報 English                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| はじめての方へ                                                                                                                            | Last updated: 03/05/2006 02:37:25     Last updated: 03/05/2006 02:37:25 |

| <u> 試作関係</u><br>- <u>該作案内</u><br>- <u>各試作の現況</u><br>- <u>チップ試作日租</u><br>- <u>チップ試作日租</u><br>- <u>チップ試作日日込</u><br>- <u>各</u> 就作加人の登 | 過去のチップ試作においてメーリングリストに流れたメールを以下に公開致します。設計上不明な点等があった場合の参考にして下さい。(ただしいずれのページもアクセスをチップ試作申し込みを行って守秘契約<br>書類を提出した方に限っております)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| - 各該作加しへの登録<br>- 各該作加し適去記<br>- 組立サービス<br>- ソケットボード情報<br>- チップ試作に支払<br>状況一覧                                                         | [CAD利用者]全文檢委           ・ 年度OAD利用者チップ試作 (日付順)## (スレッド順)## (金文)           [モトローラ/オンセミコンダクタ 12um子ップ試作 (日付順)## (スレッド順)## (金文)           ・ 00年度第1回モトローラ/オンセミコンダクタ 12umチップ試作 (日付順)## (スレッド順)## (金文)           ・ 00年度第2回モトローラ/オンセミコンダクタ 12umチップ試作 (日付順)## (スレッド順)## (全文)                                                                                                                                                                                                                                                                                                                                                                                                 |

| <u> </u>                                                                                                                           | <ul> <li>0044度第2回にトローラ/オンセミコンダクタ 12000 テップ設計 (三日道)## (スレッジ園)## (全文)</li> <li>014度第2回モトローラ/オンセミコンダクタ 12000 テップ設計 (三日位値)## (スレッジ値)## (全文)</li> <li>014度第2回モトローラ/オンセミコンダクタ 12000 テップ試作 (日位値)## (スレッジ値)## (全文)</li> <li>024年度第2回モトローラ/オンセミコンダクタ 12000 テップ試作 (日位値)## (スレッジ値)## (全文)</li> <li>024度第2回モトローラ/オンセミコンダクタ 12000 テップ試作 (日位値)## (スレッジ値)## (全文)</li> <li>034年度第2回モトローラ/オンセミコンダクタ 12000 テップ試作 (日位値)## (スレッジ値)## (全文)</li> <li>034年度第2回モトローラ/オンセミコンダクタ 12000 テップ試作 (日位値)## (スレッジ値)## (全文)</li> <li>034年度第2回モトローラ/オンセミコンダクタ 12000 テップ試作 (日位値)## (スレッジ値)## (全文)</li> </ul>                                                                                          |

| <u>チェック!</u><br><u>・CADUserMLの音</u><br><u>・CADUserMLの</u><br><u>去記事</u><br>- CAD講習会案内<br>・CAD講習会データ                                | <ul> <li>04年度第1回モローラ/オンセミコンダクタ12umチップ試作(日位順)##(スレンド値)##(全交)</li> <li>04年度第1回モローラ/オンセミコンダクタ12umチップ試作(日位順)##(スレッド値)##(全交)</li> <li>05年度第1回モローラ/オンセミコンダクタ12umチップ試作(日位値)##(スレッド値)##(全交)</li> <li>05年度第1回モローラ/オンセミコンダクタ12umチップ試作(日位値)##(スレッド値)##(全交)</li> <li>96年度 電日マローラ/オンセミコンダクタ12umチップ試作(日位値)##(スレッド値)##(全交)</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| <u>·VDEC数材</u><br>·凸版サポートサー<br>ビス                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Fig. 1.2 Archives of emails of VDEC mailing-list.

like to setup chip fabrication services related to CMOS/ MEMS to fulfill the researches for "More than Moore". We also encourage researchers to fully use of VDEC facilities such like LSI testers, FIB systems and EB writer for the wide spread of research purposes.

Fig. 1.3 Trends of number of papers through VDEC activities.

Fig. 1.4 Number of papers related to VDEC facilities.

# 1.2 VDEC CAD Tools

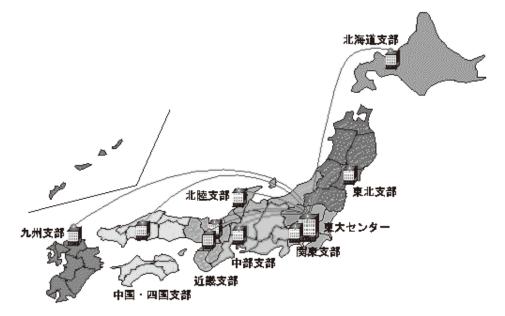

Since 1996, VDEC has provided CAD software licenses to the registered researchers in universities and colleges in Japan. The CAD tools we provided in 2018 are shown in Table.1.2.1. The researchers can use those CAD tools when their local machines, whose IP addresses are registered in advance, are authorized by one of VDEC license server located in the ten VDEC subcenters shown in Fig. re 1.2.1. For each CAD tool, VDEC provides 10-100 floating licenses. Those CAD tools can be utilized only for research and education activities in national universities, other public universities, private universities, and colleges.

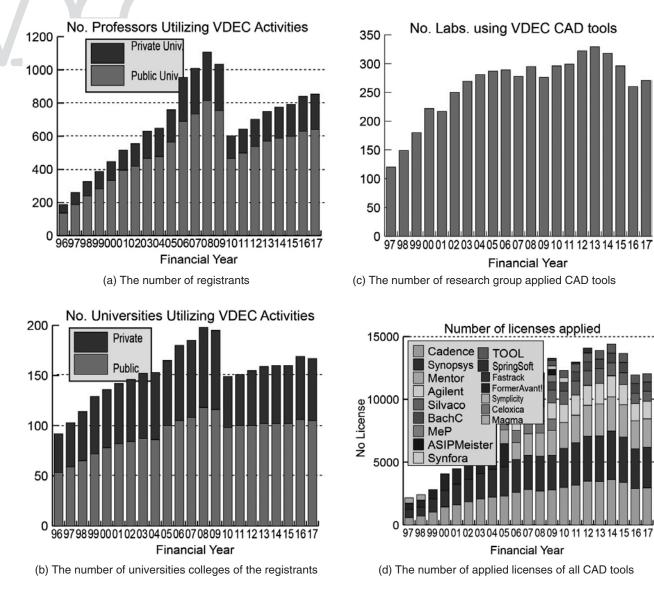

When one is going to use VDEC CAD tools and chip fabrication service (the details are described in Section 1-3), some faculty member of his/her research group in a university or a collage needs to do user registration. Fig. re 1.2.2 shows (a) the number of registrants, (b) the number of distinguished universities/colleges of the registrants, and (c) the number of registrants who applied VDEC CAD tools, (d) the number of applied licenses of all CAD tools.

| Table 1.2 | 2.1 VDEC | CAD tools |

|-----------|----------|-----------|

|-----------|----------|-----------|

| Name              | Function                                                                                                                                                                                                                                                            | Vendor                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Cadence tool set  | Verilog-HDL/VHDL entry, Simlation, Logic synthesis, Test pat-<br>tern generation, Cell-based (including macros) place, route,<br>and back-annotation, Interactive schematic and layout editor,<br>Analog circuit simulation, Logic verification, Circuit extraction | Cadence Design Systems, Inc. |

| Synopsys tool set | Verilog-HDL/VHDK simulation, Logic synthesis, Test pattern generation, Cell-based (including macros) place, route, and back-annotation, Circuit simulation, Device simulation                                                                                       | Synopsys, Inc.               |

| Mentor tool set   | Layout verification, Design rule check                                                                                                                                                                                                                              | Mentor Graphics Co. Ltd.     |

| Silvaco tool set  | Fast circuit simulation                                                                                                                                                                                                                                             | Silvaco                      |

| ADS/Golden Gate   | Design and verification of high-frequency circuits                                                                                                                                                                                                                  | Keysight Technologies        |

| Bach system       | BachC-based design, synthesis, and verification                                                                                                                                                                                                                     | Sharp                        |

| LAVIS             | Layout visualization platform                                                                                                                                                                                                                                       | TOOL                         |

Fig. 1.2.1 VDEC Subcenters

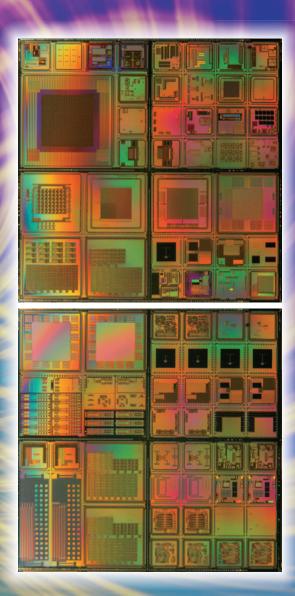

## 1.3.1 Trends of VLSI Chip Fabrication Services

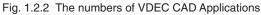

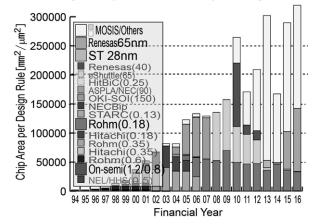

Fig. 1.3.1 shows a trend of number of designed chips for VDEC chip fabrication services, including pilot project prior to VDEC establishment.

VLSI chip fabrication is limited to 0.5 mm CMOS provided by NTT Electronics during the pilot project in 1994 and 1995. VDEC chip fabrication had started in 1996 with 1.2 mm CMOS provided by Motorola Japan, which is now On-Semiconductor as well as the 0.5 mm CMOS. In 1997, VDEC received cooperation from Rohm and has started 0.6 mm CMOS process. In 1998, VDEC started chip fabrication services of 0.35 mm CMOS by Hitachi, and in 1999, VDEC started 0.35 mm CMOS by Rohm. We had a test chip fabrication of 0.13 mm CMOS by STARC through "IP development project" in 2001. We added 0.18 mm CMOS by Hitachi into our chip fabrication menu in 2001. From 2002, we started VDEC-MOSIS chip fabrication program initiated by Prof. Iwata of Hiroshima University. Under this program, VDEC member can access to TSMC and IBM processes with lower price. We also started Bipolar chip fabrication by NEC Compound Semiconductor Devices. In 2004, we started 0.15 mm SOI-CMOS chip fabrication by Oki Electric as test chip fabrications. In the same year we started 90 nm CMOS chip fabrication by ASPLA/STARC. In 2006, we started 0.18 mm CMOS by Rohm and 0.25 mm SiGeBiCMOS by Hitachi. In 2008, we started 65 nm CMOS process by eShuttle, after closure of 90 nm CMOS chip fabrication in 2007. In 2010, we started 40 nm CMOS process by Renesas Electronics through "Next Generation Semiconductor Circuits & Architecture" project between METI and STAR. On the other hand, 1.2 mm CMOS chip fabrication program came to end by the September 2011. 40 nm CMOS by Renesas Electronics and 65 nm by eShuttle also come to end by Oct. 2012 and Aug. 2013, respectively. We started CMOS 0.8 µm in Oct. 2012 by On-semiconductor-Sanyo as a test chip fabrication and opened it as the regular chip fabrication menu in 2012. We started FD-SOI 28 nm CMOS by ST-Microelectronics through CMP, France, as the advanced CMOS process in 2013. We started SOTB 65 nm CMOS by Renesas Electronics in 2015. We initiated two more chip fabrication trials in 2017, on CMOS 0.6 um HV from Ricoh, and CMOS 40 nm from Mie Fujitsu.

Fig. 1.3.1(a) shows trends of number of chip designed for VDEC chip fabrication. For the first 6 years until 2001, the number of designed chips shows steady increase, which means drastic improve of the effectiveness

0 94 95 96 97 98 99 00 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 Financial Year

Desiged Chip Area Fabricated per Design Rule

(b) Trend of designed area.

(c) Trend of designed area normalized by design rule.

researches and education of LSI design, and we assume drastic increase of number of students related to LSI chip design and education. During few years of stable number around 400 chip designs per year, we can see transition of designs toward finer process. In 2007, we saw a large drop, which was caused by sudden process transition from 0.35 mm CMOS to 0.18 mm CMOS, and in 2008, we also saw another drop by process transition from 90 nm CMOS to 65 nm CMOS.

Fig. 1.3.1(b) shows trends of designed chip area, which shows much clear trends of drop by process migration. On the other hand, Fig. 1.3.1(c) shows trends of designed chip area normalized by design rule, which assume to be strong relation with design efforts. Coming from the fact that the normalized chip area is still growing, we assume the major reason for decrease of number of chips and designed area is increase of design effort per chip and per unit area due to process scaling.

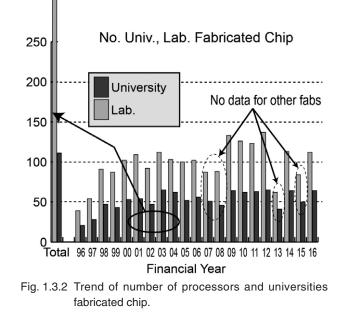

Fig. 1.3.2 shows trends number of professors and universities fabricated chip. Number of professors who have contracted NDA for process technologies to access design rules and design libraries are, 83, 283, and 45, respectively, for 65 nm CMOS, 0.18 mm CMOS, and 0.8 um CMOS.

Table 1.3.1 Chip fabrication schedule in 2017 $\bigcirc$  0.8 mm CMOS (On-Semiconductor - Sanyo)

## 1.3.2 Overview of chip fabrication in 2017

Table 1.3.1 lists chip fabrication schedule in 2017. Please refer to list in Chapter 2 for details of designers and contents of chip designed.

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2017 #1 | 2017/ 7/10                | 2017/10/ 2      | 2018/ 1/ 4    |

| 2017 #2 | 2018/ 1/15                | 2018/ 3/26      | 2018/ 6/25    |

#### ○ 0.18 mm CMOS (Rohm)

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2017 #1 | 2017/ 5/21                | 2017/ 6/26      | 2017/ 9/21    |

| 2017 #4 | 2017/ 9/ 7                | 2017/ 9/19      | 2017/12/19    |

| 2017 #2 | 2017/ 8/ 7                | 2017/10/30      | 2018/ 1/31    |

| 2017 #3 | 2017/11/27                | 2018/ 2/19      | 2018/ 5/28    |

#### ○ SOTB 65 nm CMOS

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2017 #1 | 2017/ 6/19                | 2017/ 7/18      | 2017/12/14    |

| 2017 #2 | 2017/12/18                | 2018/ 2/23      | 2017/ 8M      |

## 1.3.3 Libraries and design flows

and design flows for digital design and PDKs for analog design. Table 1.3.2 lists libraries available now.

VDEC have been working to prepare design libraries

| Table 1.3.2 L | _ibraries available | for VDEC ch | ip fabrication |

|---------------|---------------------|-------------|----------------|

|---------------|---------------------|-------------|----------------|

| Technology   | Name           | Author                                                                     | Contents                |

|--------------|----------------|----------------------------------------------------------------------------|-------------------------|

| 0.18 mm CMOS | Rohm library   | Rohm Library                                                               | Synthesis (Synopsys)    |

| (Rohm)       |                | Std. Cells, IO cells, RAM<br>(Distributed with CDROM)                      | Simulation (VerilogXL)  |

|              |                |                                                                            | P&R(LEF/DEF)            |

|              | Kyodai Library | Onodera Lab., Kyoto University                                             | Synthesis(Synopsys)     |

|              |                |                                                                            | Simulation (VerilogXL)  |

|              |                |                                                                            | P&R(Astro)              |

|              | Todai Library  | VDEC                                                                       | Synthesis(RTL Compiler) |

|              |                | Design flow based on library prepared by<br>Onodera Lab., Kyoto University | Simulation (VerilogXL)  |

|              |                |                                                                            | P&R(Encounter)          |

|              | PDK            | VDEC                                                                       | PDK(IC6.1)              |

## 1.4 Seminar

Seminar is indispensable for the improvement of LSI design technology. Some seminar and forums, such as technical seminar for CAD use, refreshing seminar for working people, designer's forums for young professors and students were held in 2016.

### [Technological seminar for CAD use]

In a technological seminar for CAD use, VDEC invites lecturer from each tool vender, such as Cadence, Synopsys and Agilent, to hold the CAD operation course. Moreover, the course concerning the design flow in the VDEC environment was held by the VDEC staff. A technological seminar for CAD use for the beginner was held in The University of Tokyo VDEC in August and September at the year 2017. This seminar took 5 days for 2 kinds of Cadence tools, 3 days for 2 kinds of Synopsys tools, 1 days for 1 kind of Keysight tool. In addition,

VDEC teachers gave lecturers on transistor level circuit design course, and digital circuit design course under the VDEC EDA environment. Teachers and students up to 40 people attended a lecture in each course, and master the use of each tool for VLSI design flow that uses the VDEC library. Moreover, another technical seminar for CAD use for matured teachers and students was held in March by Cadence 2 kind and 4 days, Synopsys 2 kinds and 2 days (Table 1.4.1). The demand for these CAD technological seminars is very large, and VDEC has maintained the mechanism of a large-scale CAD technological seminar holding corresponding to this situation. So far, the seminar was held at the University of Tokyo OR other VDEC branch, however, we started to distribute the lecture using Web streaming, so that students around VDEC branch can take the seminar at the branch school.

Table 1.4.1 CAD technological seminar in summer of the year 2016

|               | lecimological seminal in summer of the year 2010 |                   |    |

|---------------|--------------------------------------------------|-------------------|----|

| 2017/08/17-18 | Synopsys DesignCompiler+PowerCompiler Seminar    | Univ. of Tokyo    | 13 |

| 2017/08/17-18 | Synopsys DesignCompiler+PowerCompiler Seminar    | Kyoto Univ.       | 1  |

| 2017/08/17-18 | Synopsys DesignCompiler+PowerCompiler Seminar    | Osaka Univ.       | 6  |

| 2017/08/17-18 | Synopsys DesignCompiler+PowerCompiler Seminar    | Hiroshima Univ.   | 2  |

| 2017/08/22-23 | Cadence Virtuoso ADE Seminar                     | Univ. of Tokyo    | 11 |

| 2017/08/22-23 | Cadence Virtuoso ADE Seminar                     | Tohoku Univ.      | 3  |

| 2017/08/22-23 | Cadence Virtuoso ADE Seminar                     | Kyoto Univ.       | 1  |

| 2017/08/22-23 | Cadence Virtuoso ADE Seminar                     | Hiroshima Univ.   | 1  |

| 2017/08/22-23 | Cadence Virtuoso ADE Seminar                     | Akita Pref. Univ. | 2  |

| 2017/09/6-8   | Cadencee Virtuoso Layout Seminar                 | Univ. of Tokyo    | 15 |

| 2017/09/6-8   | Cadencee Virtuoso Layout Seminar                 | Kyoto Univ.       | 2  |

| 2017/09/6-8   | Cadencee Virtuoso Layout Seminar                 | Osaka Univ.       | 5  |

| 2017/09/6-8   | Cadencee Virtuoso Layout Seminar                 | Hiroshima Univ.   | 1  |

| 2017/09/6-8   | Cadencee Virtuoso Layout Seminar                 | Akita Pref. Univ. | 5  |

| 2017/09/13    | Synopsys HSPICE Seminar                          | Univ. of Tokyo    | 8  |

| 2017/09/13    | Synopsys HSPICE Seminar                          | Tohoku Univ.      | 2  |

| 2017/09/13    | Synopsys HSPICE Seminar                          | Osaka Univ.       | 4  |

| 2017/09/13    | Synopsys HSPICE Seminar                          | Hiroshima Univ.   | 1  |

| 2017/09/13    | Synopsys HSPICE Seminar                          | Akita Pref. Univ. | 5  |

| 2017/09/13    | Synopsys HSPICE Seminar                          | Ariake Tech. Col. | 9  |

| 2017/09/14    | Keysight Golden Gate Seminar                     | Univ. of Tokyo    | 9  |

|               | 1                                                |                   |    |

| 2017/09/14 | Keysight Golden Gate Seminar | Osaka Univ.       | 1 |

|------------|------------------------------|-------------------|---|

| 2017/09/14 | Keysight Golden Gate Seminar | Hiroshima Univ.   | 1 |

| 2017/09/14 | Keysight Golden Gate Seminar | Akita Pref. Univ. | 5 |

| 2018/03/08-09 | Cadence Innovus Seminar               | Univ. of Tokyo  | 16 |

|---------------|---------------------------------------|-----------------|----|

| 2018/03/08-09 | Cadence Innovus Seminar               | Osaka Univ.     | 3  |

| 2018/03/08-09 | Cadence Innovus Seminar               | Hiroshima Univ. | 3  |

| 2017/03/13    | Synopsys XA-VCS CoSim Seminar         | Univ. of Tokyo  | 13 |

| 2017/03/13    | Synopsys XA-VCS CoSim Seminar         | Hiroshima Univ. | 2  |

| 2017/03/13    | Synopsys XA-VCS CoSim Seminar         | Miyazaki Univ.  | 1  |

| 2017/03/14    | Synopsys IC Symplify Seminar          | Univ. of Tokyo  | 19 |

| 2017/03/14    | Synopsys IC Symplify Seminar          | Hiroshima Univ. | 2  |

| 2017/03/19-20 | Cadence Allegro PCB + Sigrity Seminar | Univ. of Tokyo  | 13 |

| 2017/03/19-20 | Cadence Allegro PCB + Sigrity Seminar | Hokkaido Univ.  | 2  |

| 2017/03/19-20 | Cadence Allegro PCB + Sigrity Seminar | Hiroshima Univ. | 2  |

## [Refresh Seminar for Working People]

Teachers of universities and designers in the first line of the enterprise were invited to the lecturer at "VLSI design refresh seminar" was held aiming at the latest, advanced knowledge and technical learning concerning VLSI design as a refreshing education for working people involved in the integrated circuit industry (Table 1.4.2). Though this seminar started chiefly in year 1998 under the support of Ministry of Education Technical Education Division to give practicing education of the latest VLSI design technology, it continues under many supports from many societies.

Course A: analog integrated circuit design (7/10 -12), Course M1: MEMS design (6/12-13), Course M2:MEMS fabrication (7/18-20), and Course R: RF circuit design (7/13-14). Teachers from industry and universities involved in the integrated circuit research and the education were invited as the lecturer, and they introduced a state-of-the-art VLSI design technology including the practice using a lecture concerning VLSI design and the latest CAD tool. The participants for the course A, M1, M2, R were 19, 14, 12, 3, respectively.

Fig. 1.4.2 Refresh Seminar at VDEC seminar room at the University of Tokyo, VDEC.

| Course A: A  | nalog Circuit Design (3 days)                                                            |

|--------------|------------------------------------------------------------------------------------------|

| 0            | uit Design and simulation<br>Circuits Verification (LVS, DRC)                            |

|              | ugimoto (Chuo Univ.), Hidetoshi Onodera<br>.), Koji Kotani (Tohoku Univ.)                |

| Course M1:   | MEMS Design (2 days)                                                                     |

|              | 5                                                                                        |

| ⁄oshio Mita  | (Univ. of Tokyo)                                                                         |

| Course M2:   | MEMS Fabrication (3 days)                                                                |

| ithography   | n and Analysis<br>, Etching, Release<br>easurement and analysis                          |

| ⁄oshio Mita  | (Univ. of Tokyo)                                                                         |

| Course R: C  | CMOS-RF Circuit Design (3days)                                                           |

| Basic Perfo  | Demodulation, Cascaded connection<br>rmace, Tranceiver Architecture<br>lent, Design Flow |

| lirovuki Ito | (Tokyo Institute of Technology)                                                          |

# [Designer's forum for young teachers and students]

VDEC LSI designer forum intended for students and young teachers has been held. The VDEC LSI designer forum has aimed to sharing information that cannot be obtained at a society and an academic society, for example, the failure case and the solution in which LSI designer has a hard time, the inside story of CAD industry, the construction method in the design milieu in the laboratory, and so on. This year, we had the meeting in Futsukaichi Hot Spring, in September. No less than 35 participants were flourishing at the gathering.

| 9/4 (Mon)   |                                    |

|-------------|------------------------------------|

| Time        |                                    |

| 12:00-12:30 | Reception                          |

| 12:40-14:20 | VDEC Design Award Presentation I   |

| 14:30-16:10 | VDEC Design Award Presentation II  |

| 16:20-17:40 | VDEC Design Award Presentation III |

| 19:00-      | VDEC Design Award Ceremony         |

#### Table 1.4.3 Program of Designers Forum in 2017

#### 9/5 (Tue)

| Time        |                          |

|-------------|--------------------------|

| 9:00-10:00  | Idea Contest Presentaion |

| 10:00-12:00 | Ph.D Session             |

| 12:00-13:00 | Plenary Talk             |

| 13:00-13:10 | Closing                  |

# 1.5 Facilities

The VDEC has provided the big facilities for universities in Japan from its establishment (1996). Big facilities refer to those which are impossible to acquire and or maintain by an individual research unit. Table 1.5.1 shows the available facilities of VLSI testers and some process machines, which are placed at the tester room and the super clean room of the Takeda building. In 2004, the VLSI tester (T2000) and the EB lithography machine (F5112+VD01) were donated to the VDEC by the ADVANTEST. In the year 2012, VDEC joined MEXT (Ministry of Education)'s Nanotechnology platform to enforce its multi-use capability. (For Nanotechnology Platform refer section 1.8).

In 2017, VDEC has launched a cooperative project with LPKF Laser & Electronics Corporation Japan. LPKF's UV laser printed circuit machine (ProtoLaser U3) is installed in Takeda Building room 204 (called as VDEC backend room). The machine is capable of engraving up to  $35 \mu$ m-thick copper wirings and othermaterials.

The facilities can be used by user himself, after a couple of times training by attendance of licensed users; also, by presence of licensed persons, a new user can readily use the machine.

| Facility                                  | Equipment name                                                            | Description                                                                                                                                                                                                                     | Status    | Contact                           |

|-------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------|

| Logic LSI test<br>System                  | EB tester:<br>IDS10000                                                    | The chip surface voltage during opera-<br>tion can be measured with the LST tester.<br>The digital circuit with 384 pins, 1 GHz<br>can be tested.                                                                               | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                           | LSI tester:<br>ADVANTEST T2000                                            | The digital circuit with 256 pins, 512 MHz can be tested. Analog test is optional.                                                                                                                                              | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                           | Auto prober:<br>PM-90-A                                                   | Automated prober for testing LSI wafers,<br>which can be used with the LSI testers.<br>The probe card for LSIs with the VDEC<br>standard pin connections is available.                                                          | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

| Analog/RF<br>measurement<br>system        | Analog/RF measurement<br>system:<br>B1500A, 4156B, HP4284,<br>etc         | DC parameter measurement, Capacitance<br>measurement, Network analyzer,<br>Spectrum analyzer, etc.                                                                                                                              | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                           | Low-noize manual prober:<br>Cascade Microtec                              | 6 inch wafer can be measured with six<br>DC probles and two RF probes upto<br>50 GHz.                                                                                                                                           |           |                                   |

|                                           | Low-noize, temperature<br>controlled semi-auto prob-<br>er: Süss Microtec | 8inch wafer can be measured. The chip temperature range is -50 to 200° C.                                                                                                                                                       |           |                                   |

| Nanotechnology<br>Platform<br>Apparatuses | Mask lithography, Direct<br>lithography: F5112+VD01                       | Minimum linewidth: 50 nm.<br>Lithography for 5 inch photomask (thick-<br>ness: 2.3 mm), 2-8 inch wafers, and chips<br>is possible.                                                                                              | Available | nanotech@<br>sogo.t.u-tokyo.ac.jp |

|                                           | Rapid Mask and Direct<br>lithography: F7000S-VD02                         | Minimum linewidth: 1xnm.<br>Lithography for 5 inch photomask (thick-<br>ness: 2.3 mm), 2-8 inch wafers, and chips<br>is possible. Stencil character projection of<br>non-square shapes such as circle, triangle<br>is possible. | Available |                                   |

|                                           | Chlorine ICP plasma etch-<br>er CE-S                                      | High density plasma etching with $Cl_2$ and $BCl_3$ is possible.                                                                                                                                                                | Available |                                   |

|                                           | Silicon DRIE MUC-21<br>ASE-Pegasus                                        | High speed, high aspect ratio etching of silicon is possible                                                                                                                                                                    | Available |                                   |

| Table1.5.1 | Available | facility | list |

|------------|-----------|----------|------|

|------------|-----------|----------|------|

|                        | UV Laser Printed Circuit<br>Board Engraver LPKF<br>ProtoLaser U3    | Using UV laser, copper material up to 35µm and other materials such as flexible material can be engraved.                                                                                                                                              | Available<br>at VDEC<br>204 |

|------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| FIB system             | FIB:<br>SII XVision200TB                                            | Repair of photomask, sample etching,<br>etc. (Through Nanotech. Platform and<br>LCNet)                                                                                                                                                                 | Available                   |

| LSI FIB system         | FIB: FEI V400ACE                                                    | Repair of VLSI from both frontside and backside, with CAD navigation and / or IR camera is possible. W/SiO <sub>2</sub> deposition is possible.                                                                                                        | Available                   |

| Chip Bonding<br>System | Wedge Bonder: Westbond<br>7476D                                     | $25 \ \mu m \ \phi$ Al or Au wire wedge bonding machine.                                                                                                                                                                                               | Available                   |

|                        | Epoxy Die Bonder<br>Westbond7200C                                   | Precision Manupilator system. Epoxy<br>and or Ag paste chip bonding and or<br>glued wiring.                                                                                                                                                            | -                           |

|                        | Semi-Auto Bonder<br>Westbond4700E                                   | $18 \sim 25 \ \mu m \ \phi$ Au Ball bonding or bump creation.                                                                                                                                                                                          |                             |

|                        | Precision Manual Flip-<br>Chip Bonder Finetech<br>Fineplacer Lambda | Face-to-face bonding up to 15 mm square<br>chips. Alignment is through video cam-<br>era. Bonding is by heating chips with TV<br>camera. (Ultrasonic Unit can addition-<br>ally be purchased.) XY $\pm$ 0.5 $\mu$ m, and $\theta$<br>=1mrad precision. |                             |

# 1.6 Activity plan for 2018

VDEC will continue activities on chip fabrication services, CAD tool support, dispatching design related information and donated division "D2T", as has been previous years.

# [Design related information dispatching/Seminar]

We will continue holding the following seminars: (1) CAD tools seminars which have been continued since 1997, (2) "Refresh seminar" since 1998, (3) "Designer Forum" since 1997. We will also continue seminars for LSI tester usage at VDEC and sub-centers, workshops on LSI testing technologies initiated by D2T.

## [CAD tool support]

We will continue Cadence tools, Synopsys tools and

Mentor tools as the main stream design tools. We will continue analog RF design environment, GoldenGate and ADS by Agilent, C-based design environment, BachC by Sharp. In addition, we continue trial of several CAD tools, such as layout platform, Lavis by TOOL. Design debugging platform from SpringSoft has merged into Cadence tools and will be continued. SmartSpice by Silvaco, will be also continued.

## [Chip fabrication services]

We will continue chip fabrication services for SOTB 65 nm CMOS by Renesas Electronics, 0.18 mm CMOS by Rohm, FD-SOI 28 nm CMOS by ST Microelectronics through CMP and 0.8 mm CMOS by On-semiconductor-Sanyo as the regular services.

#### Table 1.7.1 Chip fabrication schedule

[CMOS 1.2 µm2P2M] On-Semiconductor(Former Motorola Japan)

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2018 #1 | 2017/ 7/10                | 2017/10/ 2      | 2017/12/25    |

| 2018 #2 | 2018/ 1/15                | 2018/ 3/26      | 2018/ 6/25    |

#### [CMOS 0.18 µm1P5M(+MiM)] Rohm

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2018 #1 | 2018/ 4/ 2                | 2018/ 6/25      | 2018/10/12    |

| 2018 #2 | 2018/ 6/18                | 2018/ 9/10      | 2018/12/28    |

| 2018 #3 | 2018/ 8/13                | 2018/11/ 5      | 2019/ 2/22    |

| 2018 #4 | 2018/12/ 3                | 2019/ 2/25      | 2019/ 6/14    |

#### [FD-SOI CMOS 28 nm1P10M] ST Microelectronics

Based on the chip fabrication schedule through CMP.

#### [SOTB CMOS 65 nm] Renesas Electronics

|         | Chip application deadline Design deadline |            | Chip delivery |  |

|---------|-------------------------------------------|------------|---------------|--|

| 2018 #1 | 2018/ 6/18                                | 2018/ 7/30 | 2019/ 2/ 2    |  |

| 2018 #2 | 2018/12/17                                | 2019/ 1/28 | 2019/ 7/27    |  |

# 1.7 Venture companies related to VDEC

Some professors related to VDEC started venture companies. The following is a list of the venture companies related to VDEC.

#### [1] AIL Co., Ltd. (http://www.ailabo.co.jp/)

Related professor : Professor Kazuo Taki, Kobe Univ. (President-Director)

#### [2] Synthesis Corporation (http://www.synthesis.co.jp/)

Related professor : Professor Emeritus Isao Shirakawa, Osaka Univ. (Director)

Description of business : (1) Hardware/software co-design

- (2) System LSI design, design services

- (3) Development and sales of IPs

- (4) Development of EDA tools

#### [3] Nanodesign Corporation (http://www.nanodesign.co.jp/)

Related professor : Professor Kazuyuki Nakamura, Kyushu Institute of Technology. (Representative Director)

### [4] A-R-Tec Corp. (http://www.a-r-tec.jp/)

Related professor : Professor Emeritus Atsushi Iwata, Hiroshima Univ. (Representative Director)

Description of business : (1) Measurement and analysis of LSI substrate noise

(2) Design of analog-RF mixed signal LSIs

(3) Training of analog design on the JOB method

#### [5] Ishijima Electronics (http://ishi.main.jp/)

Description of business : (1) Electronic circuit development

- (2) Software development

- (3) Consulting

## 1.8 "Nanotechnology Platform": Ultra Small Lithography and Nanometric Observation Site

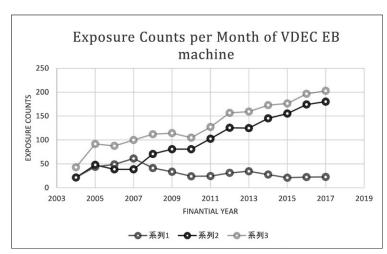

VDEC is operating an open-use nanotechnology platform "Ultra Small Lithography and Nanometric Observation Site" together with the Institute of Engineering Innovation of Graduate School of Engineering. The site is supported by Japanese Ministry of Education (MEXT)'s Nanotechnology Platform grant. Any researchers in Japanese Universities, Laboratories, and Companies can take full advantage of The University of Tokyo's cutting-edge nanotechnology apparatuses and know-hows. The accessible technology includes Lithography and Etching environment, Ultra High-Voltage Acceleration (1MV) transmission electron microscope (TEM) that is capable of visualizing upto light materials such as Nitrogen. VDEC takes part in the lithography at Takeda Sentanchi Super Cleanroom. Through VDEC's key apparatus F5112+VD01 donated from Advantest Corporation as well as F7000S-VD02 purchased by national budget, VDEC is supporting post-VLSI activities such as MEMS. The machine is capable of rapidly writing patterns on arbitrary-shaped targets sizing from 1cm-sqare chip to 8-inch round wafers. The performance is measured by the number of research reports and machine use. The University of Tokyo site has received 168 research reports, composed of 29 from big companies, 4 from Small and Medium-size Enterprises (SMEs), 35 from other universities, 91 from UTokyo researchers (including external collaboration but excluding VDEC), and 10 from public research institutes. The exposure count was 2434 for 12 months (202.8 / month), which is the first time that use per month exceeded 200. As shown in the Fig. 1, usage is monotonously increasing. "Open ratio", which is the number of days in which users outside the University of Tokyo came, divided by machine open days, was 99%. Due to the strong support of nanotech. Platform, even a novice user can obtain fine lithography result by using the apparatuses with the Platform engineering staffs of VDEC. Consequently, free machine time is decreasing so the team is trying to acquire financial support to increase the number of machines. Also in FY2017, the French Nanotechnology Network project CNRS-RENATECH asked to the UTokyo VDEC to launch an engineerclass international exchange program. The program is financially fully supported by VDEC's project and one Ph.D-holding research engineer from France (FEMTO-ST, Besancon) is with VDEC Mita Lab for one year.

#### URL:http://nanotechnet.t.u-tokyo.ac.jp/

Fig. 1 Monthly Average Exposure Count of EB Machine (s).

## 2. Activity Report of ADVANTEST D2T Research Division

2.1 Introduction of ADVANTEST D2T Research Division

## 2.1.1 Aim of the establishment of ADVANTEST D2T Research Division

The ADVANTEST D2T research division was established in VDEC in October 2007. As the name suggests, it is financially supported by ADVANTEST Corporation.

The aim of establishment of the ADVANTEST D2T research division is to promote the research and education environment of VLSI testing in all universities and colleges in Japan. "D2T" means that we consider not only design but also testing. Through our activities, we hope to provide expertise in design and testing for the industry. In addition, we are exchanging researchers with other universities and research institutes in both Japan and overseas. Moreover, the D2T research division is suitable for collaborations with the industry because the testing of VLSI is one of the most practical research topics in the industry. Based on these activities, our final goal is to become a center of excellence of VLSI testing in Japan.

The D2T research division has spent 10 years in total for the 1st (Oct. 2007–Sep. 2010), 2nd (Oct. 2010–Sep. 2013), and 3rd (Oct. 2013–Sep. 2016) project phases, and now we are in the 4th phase of the D2T project courtesy of ADVANTEST Corporation. In this financial year, we invited Professor Adit Singh from Auburn University (2018/1–) for research and educational collaboration with VDEC.

The details of our group's activities are presented in the following sections.

## 2.1.2 Members of ADVANTEST D2T Research Division

| Project Professor  | Masahiro Fujita               |

|--------------------|-------------------------------|

| Project Professor  | Adit Singh (2018/1~)          |

| Project Lecturer   | Akio Higo (2017/10~)          |

| Project Lecturer   | Rimon Ikeno (~2017/9)         |

| Project Researcher | Parit Kanjanavirojkul         |

|                    | (2017/4~2018/3)               |

| Researcher         | Takahiro Yamaguchi            |

|                    | (ADVANTEST Laboratories Ltd.) |

|                    | (~2017/12)                    |

| Researcher         | Masahiro Ishida               |

|                    | (ADVANTEST Corporation)       |

|                    | (~2017/9)                     |

| Researcher         | Koji Asami                    |

|                    | (ADVANTEST Corporation)       |

|                    | (2017/10~)                    |

| Assistant Clerk    | Makiko Okazaki                |

|                    |                               |

## 2.2 Report of 12th D2T Symposium

The 12th D2T Symposium was held on September 28th, 2017 at Takeda Hall.

This year, we invited four lecturers from overseas for their work on research topics related to IoT and data analytics: Prof. Kwang-Ting (Tim) Cheng from Hong Kong University of Science and Technology, Prof. Shawn Blanton from Carnegie Mellon University, and Prof. Wolfgang Kunz and Prof. Dominik Stoffel from Technische Universität Kaiserslautern. The symposium also featured special lectures by Prof. Shinichi Takagi and Prof. Hiroyuki Morikawa from the University of Tokyo.

We sincerely appreciate every participant for their contribution at the symposium. We look forward to seeing many participants again at the next symposium.

## 12th D2T Symposium program

| 10:00 | Opening Remarks                                                                                 |

|-------|-------------------------------------------------------------------------------------------------|

|       | Kunihiro Asada (Director, VDEC, The University of Tokyo)                                        |

|       | Koichi Tsukui (Managing Executive Officer Executive Vice President, Corporate Relations         |

|       | Group, ADVANTEST Corporation)                                                                   |

| 10:30 | Session 1 (Chairman: Makoto Ikeda, The University of Tokyo)                                     |

|       | "Advanced MOS device technology for ultra-low-power IoT applications"                           |

|       | Shinichi Takagi (The University of Tokyo)                                                       |

|       | "Going Digital: Transformation of Society, Industry, and Life"                                  |

|       | Hiroyuki Morikawa (The University of Tokyo)                                                     |

| 12:00 | Lunch                                                                                           |

| 13:15 | Session 2 (Chairman: Tetsuya Iizuka, The University of Tokyo)                                   |

|       | "Power Supply Impedance Emulation to Eliminate Overkills and Underkills due to the Impedance    |

|       | Difference between ATE and Customer Board"                                                      |

|       | Toru Nakura (The University of Tokyo)                                                           |

|       | "Common Pitfalls in Application of a Threshold Detection Comparator to a Continuous-Time Level- |

|       | Crossing Quantization"                                                                          |

|       | Takahiro J. Yamaguchi (Advantest Laboratories Ltd., The University of Tokyo)                    |

| 14:05 | Break                                                                                           |

| 14:15 | Session 3 (Chairman: Yoshio Mita, The University of Tokyo)                                      |

|       | "Variation and Failure Characterization Through Test Data Analytics"                            |

|       | Kwang Ting Cheng (Hong Kong University of Science and Technology)                               |

|       | "Test-Chip Design for Yield Learning at the 7-nm Technology Node"                               |

|       | Shawn Blanton (Carnegie Mellon University)                                                      |

| 15:45 | Coffee Break                                                                                    |

| 16:15 | Session 4 (Chairman: Masahiro Fujita, The University of Tokyo)                                  |

|       | Rethinking Design in the IoT Era - How Formal Methods Help to Meet the Challenges"              |

|       | Wolfgang Kunz (Technische Universität Kaiserslautern)                                           |

|       | "Software in a Hardware View: New Models for Firmware Development and Safety Analysis in IoT    |

|       | Systems"                                                                                        |

|       | Dominik Stoffel (Technische Universität Kaiserslautern)                                         |

| 17:45 | Closing                                                                                         |

| 18:00 | Reception                                                                                       |

## 2.3 Research Activity Reports of ADVANTEST D2T Research Division

## High-Resolution Analog-to-Digital Converter Based on Stochastic Comparators

Takahiro J. Yamaguchi, Parit Kanjanavirojkul, Nguyen Ngoc Mai-Khanh, Rimon Ikeno, Tetsuya Iizuka, Kunihiro Asada

This project aimed to implement a high-resolution sub-ranging analog-to-digital converter (ADC) circuit based on stochastic comparators.

Process variations, together with many factors such as variations in voltage or temperature, lead to mismatched design parameters that produce input-referred offsets and hence cause non-linearity and missing output codes in an ADC. Instead of attempting to suppress such process variations as in conventional ADC, the stochastic ADC approach exploits process variations based on the assumption of a Gaussian distribution of comparator offset voltage. We identified the root cause of a voltage bounce of the source nodes of the comparator input PMOSFETs, which introduces a conversion error of the flash ADC circuit at the first stage in our sub-ranging ADC system, as quick signal transition. We improved the performance of the ADC by refining operational conditions, such as input signal frequency, slope, and voltage range, as well as by adding a delay in starting the differential current integration so as to discard the unstable current during the bouncing period.

#### **Power Integrity Evaluation Method**

Masahiro Ishida, Naoki Terao, Rimon Ikeno, Toru Nakura, Tetsuya Iizuka, Kunihiro Asada

While the required power-supply voltage has decreased owing to the advanced miniaturization of the semiconductor process, the power-supply current consumed by a semiconductor device has increased because of the huge number of transistors integrated on a single chip. This may increase the power-supply noise and cause power integrity issues of the device under test in both an ATE and practical operating environments. The purposes of this research project are to develop a power delivery network modeling method for evaluating power integrity at on-chip power-supply nodes in semiconductor devices and a new power integrity control method based on the feedback operation.

We proposed a new modeling method of series impedance connection using the nested-feedback configuration in the digital filter composition for the previously proposed feedback-based power supply impedance emulation, and we demonstrated its feasibility through computer simulation and experiments. We also extended the impedance modeling method to cases with multiple power-supply pins and carried out simulation-based studies to verify the assumed modeling methods. Furthermore, we demonstrated that the proposed method can eliminate the discrepancy of test results between two power-supply environments through an experiment with FPGA devices.

## High-Performance Analog-to-Digital Conversion Using the Wideband Spread Spectrum and Its Application

Koji Asami, Byambadorj Zolboo, Akio Higo,

Tetsuya Iizuka, Kunihiro Asada,

To measure low-cost RF devices for IoT and other applications, analog-to-digital conversion techniques with a low cost and high efficiency are required. To acquire narrow-band modulation signals scattered in a wide frequency range, a compression sampling method is studied.

In this financial year, a modulated wideband converter was investigated as a compression sampling method. After a recovery error using an arbitrary waveform was estimated, we determined that the recovery of a side lobe, as well as the main lobe, is required in a modulated waveform. Therefore, the relationship among recovery error, ADC performance (resolution and sampling rate), and the number of channels is needed to establish the cost of ADC. We study the cost of ADC, spread code, recovery algorithm, and mismatch correction between analog-to-digital channels. Rimon Ikeno, Akio Higo, Yoshio Mita, Kunihiro Asada

Maskless lithography by electron-beam direct writing (EBDW) is expected to be a low-cost lithography technology with a short turn-around time (TAT), but it has some drawbacks such as a low process throughput and low accuracy against the intended layout shapes. We are pursuing a high-speed and high-accuracy EBDW strategy utilizing the character projection (CP) method to overcome these concerns and to boost EBDW use in fields such as MEMS and photonics.

We investigated the resist and development process conditions for the high-resolution observation of lithographic results by our high-throughput and high-accuracy EB exposure strategy that combines the CP and variable-shaped beam (VSB) methods. A new CP mask for the F7000S EB writing system in the VDEC Takeda Clean Room was designed for further performance improvement. We also conducted a numerical analysis of chip temperature during the EB exposure process as well as the propagation loss of light waveguides dependent on the line-edge (wall) condition.

## International Conferences, Symposiums, Workshops

[1] Naoki Terao, Toru Nakura, Masahiro Ishida, Rimon Ikeno, Takashi Kusaka, Tetsuya Iizuka, and Kunihiro Asada, "Extension of Power Supply Impedance Emulation Method on ATE for Multiple Power Domain," 22nd IEEE European Test Symposium (ETS 2017), May 2017.

### **Domestic Conferences, Workshops, etc.**

T. Sugiyama, T. Iizuka, T. Yamaguchi, T. Nakura, K. Asada "Performance Analysis of Level-Cross Detection Method Based on Stochastic Comparator," IEICE-CAS2017-66, IEICE-ICD2017-54, IEICE-CPSY2017-63, 12/14/2017.

# Chapter 3 Research in VDEC

## Asada, Nakura and Iizuka Laboratory

(http://www.mos.t.u-tokyo.ac.jp)

### LSI Test and Improved Reliability in Ultra-Fine Process Technologies

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Naoki Terao

In LSI test, mismatch of power supply impedance between an automatic test equipment (ATE) and a customer board can cause overkills and underkills. We propose power supply impedance control method on the ATE for emulating arbitrary power supply impedance using compensation current injection. Experimental measurement results by a prototype system shows that the voltage fluctuation waveform of the ATE is adjusted to that of the customer board, meaning that the impedance on the customer board is successfully emulated by the ATE.

Our digital filter implementation method using feedback can be applied to arbitrary impedance network, not only for the power supply with single supply pin but also for the power supply with multiple power domains.

To confirm the effect of the proposed method on real LSI test, we developed a virtual ATE for demonstration. Test result of 50 real devices shows significant reduction of overkills and underkills under the power supply condition with impedance emulation.

#### PLL and LDO circuits with Time-Domain control

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Keigo Tu, Jing Wang, Naoki Ojima, Hidemasa Yoshimura

In this research, we have applied time-domain control methods to PLL circuit and its measurement. A Pulse-Width Controlled PLL (PWPLL) is a new type of PLL whose oscillator is controlled by a pulse width. The PWPLL is implementable in a very small area, on the one hand, its operating conditions are sensitive to the several variations. For example, a lock range of the PWPLL tends to be narrower than that of other PLLs.

We demonstrated a PWPLL compiler which generates GDS data and summarizes synthesized and simulation results of area, power and jitter of PWPLL with different gate length cells and choose an appropriate PWPLL design from performance specification. The inputs of the compiler are standard cell libraries, several manual cells, SPICE parameters and the target specification input-output frequency, the division ratio and the Process, Voltage, and Temperature (PVT) corner conditions. The PLL compiler calculates rough values of the design parameters, runs SPICE simulations, analyze the waveform files to adjust the design parameters, considering the variation of the PLL characteristics with the given PVT variation. When the waveform satisfies the specification, the compiler generates a verilog netlist and a GDS is designed from the netlist.

Besides, since skilled circuit designers need to spend a lot of time to make PLL(Phase Locked Loop) circuits, so a method by which everyone can create a PLL circuits in a short time is required. In this research, automatic design was made possible by creating a DCO (Digital Controlled Oscillator) in the digital PLL circuit using an inverter, NAND gate and 4-input multiplexer. We automatically simulated the DCO performance by SPICE, automatically found the appropriate parameters of the DCO circuit from the input performance of DCO and automatically created the layout of DCO using a C program.

We also do a research on LDO. Designing LDO regulators nowadays almost largely demands analog circuit design flows. Because Analog flows take time and effort, they become a bottleneck in designing LDOs. In this research, to remove the loads of analog flows, we applied a method of making LDOs with a P&R tool which is usually used in digital circuit design flows. In conventional LDOs, the parts which makes comparison between the reference and the output, such as error amplifiers or comparators, often require analog flows. The proposed circuit in the research contains two inverter chains and a phase detector. The phase detector recognizes the voltage difference between reference and output as the delay difference between two inverter chains. This comparison part is all synthesizable from standard cells, so all the circuit can be made by a P&R tool. We designed and made the proposed circuit, and confirmed trackability when the reference or the load current are changed.

#### Time Domain CDR and TDC Designs

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Meikan Chin, Ryuichi Enomoto

While digital circuits directly benefit from advanced process technologies, analog circuits suffer from negative effects such as small voltage headroom. Timedomain circuits, where analog signals are represented by digital signal edge transitions, could be a solution to the problem of analog circuits in a nanometer process.

Time-to-Digital Converter (TDC) is a representative example of time-domain circuits. TDC basically converts a time interval between two rising edges into a digital code by using delay elements. In our research, we focus on a pulse-shrinking TDC, which is one kind of the sub-gate-delay resolution TDCs. In general, TDC has a trade-off between the time resolution and dynamic range, and the trade-off is particularly remarkable in the pulse-shrinking TDC. Last year we designed and measured a TDC that improves the dynamic range while keeping the high resolution by using a hierarchical approach. We found that the TDC has a serious nonlinearity caused by process variation. So, we analyzed the impact of it by Monte Carlo simulation and designed a new TDC resistant to process variation.

TDC can be applied for various applications and Clock and Data Recovery (CDR) based on Cycle Lock Gated Oscillator (CLGO) is one example. Since the CDR consumes no dynamic power in its standby state and resumes from the standby state just after a 4-bit preamble, it can improve the total power efficiency of serial communication systems that work intermittently such as mobile and IoT sensor node applications which require not only low power consumption in operation but also in standby state and quick startup form the standby state. We proposed CDR using Delay Tunable Buffer (DTB) and Vernier TDC for tracking frequency range extension and low power consumption, designed and measured. While DTB and digital control work as designed, we found the deviation of timing in Vernier TDC. So we proposed new Vernier TDC whose reference level is tunable.

### Radiation Detector Utilizing Semiconductor Photodiode

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Yang Xiao

Scintillation detectors and semiconductor detectors

have received wide spread attention since they can specify the nuclide of radiation and estimate the arrival angle. Former research proposed a detector using the cube scintillator, SPAD (Single Photon Avalanche Diode) array image sensors, multi-coated materials, and pinholes and verified the method to detect the position of point light source inside the scintillator. We proposed a new method which calculated the track of photons to precisely estimate the position of light source. This method can cost less time to detect the light source position compared to the former research. The result of the simulation verified that by using this method the position of the light source inside the 1 mm-size scintillator could be detected with a spatial resolution of 10 um-20 um in less than 0.3s.

About the SPAD imager, we have designed several SPADs with different structures in standard CMOS process, and found a suitable structure. Then, a 31 x 31 SPAD imager with event discriminator based on the proposed breakdown pixel extraction architecture has been fabricated, and its functionality of short weak light detection has been demonstrated.

# High-Frequency Circuit Design for Communication through Dielectric Waveguide

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Nguyen Ngoc Mai-Khanh. Yoshitaka Otsuki, Daisuke Yamazaki

High-speed communication with the millimeter-wave band has been actively researched. Wireline communication with a dielectric waveguide such as polymer has been proposed and expanded research. Because it is possible to increase the communication distance at low cost while maintaining the communication speed.

The signal leaks to the outside at the bent portion of the waveguide when the frequency is low in the dielectric waveguide communication. Therefore, a high-frequency oscillator is required. In this research, we studied oscillators that oscillate at 140 GHz and have low phase noise, and also designed transmission lines and pads for measurement.

The dielectric waveguide is superior to the metal waveguide in terms of weight and price, the loss is large, so that a low loss on-chip coupler is required.

In this research, we designed a low loss on-chip coupler for use in dielectric waveguides.

One of the main causes of the electric-electromagnetic wave conversion loss in the on-chip coupler is that part of the electric power is converted into heat due to the eddy current generated in the substrate. For this reason, we propose a method to suppress the eddy current by removing the Si substrate of the chip and reduce the loss during conversion. We verified this low loss implementation method and designed a chip for verification.

## Design and Analysis Method for High-Reliability LSIs

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Nguyen Ngoc Mai-Khanh, Norihiko Nakasato,

Daigo Takahashi, Tamaki Fukudome

The modern VLSI systems that demand high reliability require carefully-designed power/ground network to provide stable power supply. Using the measurement results of magnetic field emission from LSI, the proposed method estimates the actual current flow from the magnetic field measurement results and enables us to find defects or design faults such as VIA/wire disconnections and/or current concentration with low cost. To verify the feasibility of the proposed method with actual measurement results, the test structure is designed and fabricated in 0.18 um 1P5M CMOS process. Current flow of power network in the chip was successfully estimated by actual measurement data.

Information security is very important in the modern society in which the Internet has penetrated. In this research, we propose a method to enhance the reliability of PUF (Physical Unclonable Function) and TRNG (True Random Number Generator) by employing aging phenomenon of scaled MOSFET to control the threshold voltage. Reliability enhancement of both circuits will lead to miniaturization and low-power consumption of security hardware. Currently, we confirmed by measurement that it is possible to improve the reliability of both circuits by inducing proper degradation in the SRAM.

With the improvement of the circuit performance due to the miniaturization of the semiconductor process, the speed of transmission has been improving. The data rate necessary for applications also has been improving because UHD TVs and automobiles with a lot of electrical equipment was developed. It is necessary to speed up transmission from both aspects of technology and demand, crosstalk is one of the factors hindering this. As measures for crosstalk, a circuit for reducing crosstalk at the receiving end was proposed in the previous research. In this research, we proposed a circuit with PD control circuit and time delay element based on the circuit in the previous research. Using simulation, we showed that the circuit can reduce crosstalk more effectively.

#### **High-Precision A-D Converters**

Kunihiro Asada, Toru Nakura, Tetsuya Iizuka, Takaaki Ito, Taiki Sugiyama

Analog-to-Digital Converters (ADC) are widely used as circuits which convert analog signal to digital signal. Low-power and high-precision ADCs are needed for applications such as biomedical sensing and wireless sensor network. In this study, successive approximation register (SAR) ADC which have several advantages for better power efficiency is designed in order to achieve high-precision and low-power ADCs. Though there is a tradeoff between conversion accuracy and power consumption, we optimized power consumption by combining noise tunability implemented to comparator and redundant bit technique. Recently, we designed prototype ADC and evaluated its performance.

ADC based on level-cross detection quantizes time rather than voltage. When the clock frequency is doubled, SNR of ADC improves 3 dB whereas that of level-crossing ADC improves 6 dB. Therefore, level-crossing ADC benefits more from fine time resolution in scaled technologies. A stochastic comparator that drives multiple comparators in parallel is proposed to improve both voltage and time resolutions by utilizing stochastic nature of offset and noise whose impact is increasing through process miniaturization. A stochastic comparator is familiar with the digital design because of the concept based on process variation and it will improve the performance by process miniaturization. We analyze the precision of level-cross-timing estimation method based on a stochastic comparator. We show that the level-cross-timing estimation method exhibits finer resolution compared to that uses the single comparator with the same total area of comparators. We also verify the theory by measurement. Another design approach is stochastic approach in which many comparators are driven in parallel. This emerging approach can be applied to level-crossing ADC and it is called level-crossing stochastic ADC. We analyze input slope dependency of level-crossing stochastic ADC by circuit simulations. And we will measure the input slope dependency using the chip we designed manually.

(http://www.cad.t.u-tokyo.ac.jp/)