東京大学大学院工学系研究科 附属システムデザイン研究センター 先端設計研究部門・先端デバイス研究部門 (旧VDEC)基盤設計研究部門・基盤デバイス研究部門 令和4年度

## 2022

Systems Design Lab, School of Engineering, (VLSI Design and Education Center), The University of Tokyo

# **Annual Report**

man

mmm

## Message from the Director of d.lab

## Tadahiro Kuroda

Director Systems Design Lab (d.lab) School of Engineering, The University of Tokyo

In February of this year, the Ministry of Education, Culture, Sports, Science and Technology (MEXT) issued a call for proposals under their 「次世代X-nics半導体創成拠点形成事業」(Translation: Initiative to Establish Innovation Centers for Next-Generation X-nics Semiconductors). Their ultimate goal is the creation of groundbreaking, neXt-generation, novel semiconductors through multi-disciplinary synergy (multiplication "X"), much like the creation of various functional devices from spintronics and photonics, novel computing technologies from neurophysiology and quantum mechanics, and integrated devices from novel materials based on topotronics.

Regardless of the specific form of the novel semiconductor, a key requirement is the improvement of energy efficiency. In the last decade, while the amount of AI processing skyrocketed by 4 orders of magnitude, the energy efficiency of general-purpose processors increased by only an order of magnitude. This has driven platform providers such as GAFAM to develop their in-house specialized chips to achieve high energy efficiency. However, the development of specialized chips requires increasingly more time and higher cost. Given the rapid advance in AI technology, if it takes a year to develop a specialized chip, it is already obsolete by the time the development is complete. The strategy for growth in the DX age requires rapid iteration (being agile) of the development-improvement cycle. This can be achieved if LSI chips are designed the way software is written and prototyped the way a program is compiled to make them updatable like software.

A related question is how to accelerate technology innovation. The answer can be found in the idea of a collective brain expounded by Joseph Henrich, Professor of Human Evolutionary Biology at Harvard University. The bigger the collective brain is, the easier it is to accelerate technology innovation. For instance, through research conducted on various Pacific islands, the paper "Population Size Predicts Technological Complexity in Oceania" found a correlation between the size of variation in fishing tools and the population of the island. The reason that, even with a smaller brain than Neanderthals, Homo sapiens were able to invent and utilize various tools is also thought to be due to their integration into large groups. The internet has enabled a giant collective brain of 7.7 billion people. A platform that attracts many people will turn into a center for accelerated technology innovation.

We at d.lab proposed an "Agile-X Center for Democratization of Innovative Semiconductor Technology." Our target is a 10-fold increase in the population of chip designers. To that end, we will create an agile development platform to reduce both the time and cost for chip development and prototyping by an order of magnitude. During the application process, we were asked by the X-nics review committee what X stands for. We answered that it is the unknown of "what" innovation will change the world. Nevertheless, we know "where" the innovation will come from. That is the platform where a large population of people congregate. I am pleased to say that our proposal has been accepted. I believe that, in addition to More Moore and More than Moore, More People will accelerate the creation of intellectual value.

黑田,忠九

The University of Tokyo Annual Report

Message from the Director of d.lab .....1

| Chapter1                                                                       | Introduction of d.lab 4                                                                                                                             |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter2                                                                       | Activity Report of d.lab 5                                                                                                                          |

| <ul><li>2-2 Advanced I</li><li>2-3 Platform D</li><li>2-4 Platform D</li></ul> | Design Research Division<br>Device Research Division<br>esign Research Division<br>evice Research Division<br>15<br>T D2T Research Department<br>19 |

| Chapter3                                                                       | Research in d.lab 24                                                                                                                                |

| Appendix                                                                       |                                                                                                                                                     |

| A Former VD                                                                    | EC contents······42                                                                                                                                 |

| A-1 VDEC CA                                                                    | <b>D Tools</b>                                                                                                                                      |

| A-2 Status of<br>A-3 Seminar                                                   | <sup>4</sup> Chip Fabrication Support at Platform Design Research Division······44                                                                  |

| A-4 Venture                                                                    | Companies Related to VDEC······49                                                                                                                   |

The VLSI Design and Education Center (VDEC) was established at the University of Tokyo in 1996. At the time of its founding, Japan's semiconductor industry held a 50% share of the USD 50-billion global market, and engineers who could hit the ground running were in high demand. VDEC has since provided unparalleled, outstanding education to develop many high-caliber engineers for the semiconductor industry.

However, have these graduates of VDEC been able to fully realize their potential? In the last quarter century, even though the global semiconductor market enjoyed a rapid 7% annual growth rate, Japan's share continued to shrink, falling to the current level of about 10% of a market that is now approaching USD 500 billion.

The current semiconductor business is one of mass production of high volume, low margin general purpose chips. General purpose chips have been able to achieve large volumes because of the wide adoption of the von Neumann computer architecture constructed with the combination of memory and processor chips. While Japan led the world in memory device innovation, it lost the business competition on capital investment.

The mass production, mass consumption model has its limits. Because of the excessive burdens it places on the environment, the world is now facing an energy crisis. The recent trend of applying AI to big data analysis is fueling further growth in energy consumption.

In the middle of this development, a game changer has emerged. Recognizing that it is hard to compete by using general purpose chips procured from semiconductor makers, technology giants including GAFA have started to develop their own specialized logic chips in-house.

In response to this paradigm shift, the University of To-

kyo established the Systems Design Lab (d.lab) in October of 2019 and formed a strategic alliance with TSMC a month later. d.lab was formed by establishing the Advanced Design Research Division and the Advanced Device Research Division and adding them to the existing Platform Design Research Division and Platform Device Research Division which had been operating VDEC and the Takeda Clean Room. Subsequently in October of 2020, d.lab started an industrial partnership program which has grown to include more than 40 corporate members.

Furthermore, the Research Association for Advanced Systems (RaaS) was founded in August of 2020 to lay out the framework for the university to collaborate with both the industry and the government. Using d.lab and RaaS to realize a two-pronged strategy of open and closed collaboration respectively, the university is actively promoting cooperation between academia and society as well as collaborative creation with industry. Our research aims to boost the time-performance of semiconductors, with target goals of 10x increase in both energy and development efficiencies.

Japan is aiming to transition from the current industrial/information society to Society 5.0, a human-centric society where knowledge is value. In this knowledge-based society, semiconductors will evolve from being a necessity of industry to the brain cell of society.

What strategy should the semiconductor industry pursue to address this evolution? It is d.lab's mission to find the answer.

## Chapter2 Activity Report of d.lab

## 2.1 Advanced Design Research Division

#### 2.1.1 Division Overview

The Advanced Design Research Division faculty consists of four professors, one associate professor, one lecturer, one project professor, and one senior fellow (joint appointment included). Its goal is to enable the design of integrated circuits with both high energy efficiency and high design efficiency.

In July 2021, NEC Corporation and the University of Tokyo were selected to lead the research and development of a new computing mechanism to accelerate data structure processing, as part of a pilot study to identify R&D challenges for the Project for Innovative AI Chip and Next-Generation Computing Technology Development of the New Energy and Industrial Technology Development Organization (NEDO). The research is scheduled to complete by the end of June 2022.

In addition to its research effort, the Advanced Design Research Division has two organizational responsibilities. First, it operates the d.lab Partnership Program with help from other d.lab divisions. Second, it founded and operates the Research Association for Advanced Systems. The following section is the FY2021 report on these two operations.

#### 2.1.2. d.lab Partnership Program Activities

The d.lab Partnership Program was launched in FY2020 to establish an international center of knowledge-value where system designers and members of the semiconductor industry meet to exchange information and ideas and to engage in open discussion of collaboration between academia and society. The Program aims to create a hub that brings together ideas from system designers in industries including IoT, AI, 5G, automated driving, and healthcare, advanced semiconductor technologies such as advanced CMOS processes and 3D integration technologies, as well as enablers of such technologies including materials and manufacturing equipment. For FY2021, a total of 43 corporations joined the Program. Table 2.1.1 contains the list of FY2021 corporate members. We would like to thank these members again for their participation.

As noted in our last annual report, our original vision was to not only create a platform for the dissemination of the research accomplishment of d.lab, but also to turn our Mejirodai campus into a new venue for interaction and learning. We were planning to host various events to enable program members to interact with renowned professors and students at the University of Tokyo, with universities and research organizations from around the world, and with other industrial executives and leaders, as well as events to share information and knowledge from international conferences and introduce and assess the most advanced technologies from the likes of TSMC. Unfortunately, same as in FY2020, because of COVID-19, we were forced to once again center our activities in FY2021 around seminars held in the form of webinars. Our activities spanned almost the entire year from May 2021 to March 2022. Table 2.1.2 summarizes the seminars we held in FY2021.

We held our program kickoff meeting on May 19, 2021 which also featured a keynote presentation. With 5G service having been rolled out in Japan as well, the focus of R&D in the country has been shifting to Post/Beyond 5G. Professor Akihiro Nakao of the School of Engineering, University of Tokyo, who has led Japan's 5G technology development, discussed what lies ahead beyond 5G and the role semiconductor will play in a talk entitled "The Direction of Beyond 5G/Post 5G R&D and What We Can Expect from Semiconductor Development." He was followed by Professor Tadahiro Kuroda, Director of d.lab, who provided an overview of d.lab and introduced the d.lab Partnership Program activities in FY2021 together with their schedule.

On Jun 29, we held a seminar to report on the 2021 VLSI Technology/Circuit Symposia which took place from Jun 13 to 19 earlier in the year. We reported on the circuit, system, process, and device technologies presented at the Symposia. We also invited the Small and Medium Enterprise Agency to the seminar to introduce the support program aimed at promoting the semiconductor industry.

On Jul 21, we hosted another seminar to report on the

Chapter2 Activity Report of d.lab

2021 IEEE 71st Electronic Components and Technology Conference (ECTC 2021). The conference is organized by the IEEE Electronics Packaging Society to provide a forum for wide ranging discussion of the science and technology of packages, components, and microelectronic systems. It is one of the world's long-established and leading international conferences, held for the 71st time last year. The technology program covered the latest achievement in development across the full spectrum of packaging technology. Its main topics included advanced packaging, modeling and simulation, photonics, interconnection, material and process, reliability, manufacturing technology, components and RF, as well as emerging technologies. In our report, we focused on the latest trends and topics in advanced packaging, which is a mainstream technology for our current activities, and hybrid bonding, which is a next-generation core technology. The seminar was preceded by an announcement of the "VDEC Refresh Seminar for Engineers, Course M" by Associate Professor Yoshio Mita.

On Aug 18, we held our first technology exchange meeting for our corporate partners, where some of our partners presented on their differentiating technologies and expectation for future technology exchange. Presentation was made by six of our partners - Ushio Inc., Analog Devices, Inc., Showa Denko Materials Co., Ltd., KIOXIA Corporation, Semiconductor Energy Laboratory Co., Ltd., and Toppan Inc. The goal of the technology exchange meeting is to promote collaboration between our corporate partners and with d.lab faculty members and students.

On Sep 22, the second installment of the technology exchange meeting was held. The six presenting corporate partners were Dai Nippon Printing Co., Ltd., Alchip Technologies, Limited, Gigaphoton Inc, Nikon Corporation, DISCO Corporation, and Organo Corporation.

On Nov 17, we held a special seminar "Gastronomy, Robotics, and Semiconductor" in conjunction with the third installment of the technology exchange meeting. For the keynote presentation, Mr. Masahiro Fujita of Sony Group Corporation described the future that could be realized with the advance in semiconductor, AI, and robotics. From a novel perspective of gastronomy, he discussed his research on using AI and robots to expand human creativity. The keynote was followed by the presentations of TOKYO OHKA KOGYO CO., LTD. and Renesas Electronics Corporation in the third installment of our technology exchange meeting.

On Dec 17, we organized an imec Day event where we heard directly from executives in charge of R&D at imec, which leads the world in the research and development of ever advancing, ultra-high performance silicon systems. The speakers introduced their efforts in extending CMOS device scaling and development of the most advanced 3D system integration process and device technologies. It was an excellent opportunity for the audience to receive firsthand information on the most advanced silicon system technologies. Dr. Naoto Horiguchi, imec Program Director of Logic CMOS Device, discussed "CMOS device scaling options toward N1 and beyond," while Dr. Eric Beyne, imec Senior Fellow, VP R&D, and Program Director of 3D System Integration, presented on "A 3D Integration Future: enabling continued system-level electronic scaling."

The theme of our seminar on Dec 22 was TSMC Day. TSMC (Taiwan Semiconductor Manufacturing Company, Ltd.), headquartered in Hsinchu City of Taiwan, is the world's largest and most advanced semiconductor foundry. The company established the TSMC Japan 3DIC R&D Center in Japan in 2021. It is without question that, in addition to semiconductor scaling to achieve More Moore technology innovation, 3DIC technology, which realizes More Than Moore technology innovation, is key to the future of the semiconductor industry. Center Director Emoto and Technical Director Ichikawa presented the mission of the R&D center in "Overview and initiatives of TSMC Japan 3DIC R&D Center." They also provided an update on the latest technology development in the company.

At the beginning of the year on Jan 19, 2022, we held a seminar to report on IEDM2021. IEDM (International Electron Devices Meeting) is the world's top international conference on device technology organized by IEEE. The conference was held in a hybrid format – allowing both in-person and on-demand attendance – from Dec 11 to 15. In our meeting, faculty members from d.lab provided a summary of the conference and discussed the latest trends in device technology, focusing on advanced CMOS device technology and material, non-volatile memory technology, computing technology, and 3D integration technology. On Mar 2, we organized a d.lab Day event which provided a forum for the first time in the d.lab Partnership Program for d.lab faculty members to introduce their research activities. The event was held in response to interest expressed by our partners in learning about the research of our faculty members, a year and a half after the program started. It is hoped that the seminar will stimulate new activities such as collaborative research.

As the last event of our FY2021 seminar series, we held a meeting on Mar 23 to report on the 2022 International Solid-State Circuits Conference (ISSCC2021). ISSCC is the top international conference on IC technology held in February. Starting with Professor Makoto Ikeda who has been for years the chair of ISSCC's technology program, faculty members from d.lab discussed the latest trends seen in the conference in the thriving area of machine learning processors, ICs enabling emerging computing technologies exemplified by quantum computing, as well as 5G, AI, and game console ICs which are expected to drive the future of the semiconductor market.

For FY2022, we are considering organizing a mix of remote seminars and in-person events, while carefully monitoring the development of COVID-19. In addition to incorporating first-time events in our plan, we would like to continue to promote intellectual exchange between our partners and the university, and among our partners themselves.

## 2.1.3 Research Association for Advanced Systems Activities

With preparation that started in FY2019, the Research Association for Advanced Systems (RaaS) was established on Aug 17, 2020. The founding members are the University of Tokyo, Toppan Inc., Panasonic Corporation, Hitachi, Ltd., and MIRISE Technologies. The goal of RaaS is to increase 10-fold the development efficiency of specialized chips, which are indispensable in a data-driven society, by constructing a design platform for such chips and by adopting an open architecture for hardware design. In addition, RaaS aims to increase 10-fold energy efficiency by researching and developing 3D integration technology and by stacking multiple chips manufactured in the latest 7nm CMOS technology in a single package.

At RaaS, we believe that the driver of the semiconductor industry is once again swinging back from general purpose to specialized chips, against the backdrop of the unique energy crisis of the data society. The crisis is being spurred by the exponential growth in data and the increasing sophistication of AI processing. On the current trajectory, IT equipment alone is expected to consume close to twice the total available power of today by 2030, and about 200 time the total available power of today by 2050. It will be impossible to realize a sustainable future if digital transformation will consume so much energy as to destroy the earth's environment.

Under such a condition, only those who can improve energy efficiency 10-fold can afford to increase computer performance 10-fold, or extend smartphone use 10-fold. Compared to general purpose chips which are required to handle all tasks, specialized chips achieve orders-of-magnitude improvement in energy efficiency by eliminating unneeded circuits. That is why specialized chips are in demand. In addition, since AI processing utilizes neural networks which process data in parallel, it is difficult for von Neumann architecture which is designed for sequential processing to deliver adequate performance. As a result, specialized chips are being developed around the world to serve as AI accelerators. Furthermore, the slowing of Moore's Law is also providing a tailwind for specialized chips.

Unfortunately, specialized chips development requires special skills and cannot be easily undertaken by everyone. The latest chips integrate more transistors than there are people in the world. Development costs have skyrocketed in recent years to approach \$100 million. It will take even a team of several hundred designers several years to develop a specialized chip, which makes it difficult to keep pace with today's rapid technological advance.

In software development, bugs can be patched after the fact. But hardware cannot be shipped unless it is completely error-free. Compared to software, hardware development is indeed hard and carries more risk.

If technologies similar to compilers used in software development are available to chip development, in other words, if silicon compilers become a reality, we can expect both hardware development cost and risk to drop. In addition, more people can become hardware designer. Eventually, as the open source culture takes root in hardware development and the supporting ecosystem expands and develops into a multi-layer network, mass collaboration will become possible. When that happens, one will be able to develop chips like writing software.

Alan Kay once said that "People who are really serious about software should make their own hardware." Indeed, system development requires both hardware and software development.

Our goal at RaaS is to democratize access to silicon technology. We aim to create a development platform to realize agile authentic prototyping where prototypes can be created rapidly by innovating silicon compiler technology to enable designing chips like writing software.

Our technology goal is a 10-fold increase in both development efficiency and energy efficiency. We plan to improve development efficiency by creating an agile design platform and adopting an open architecture. In addition, we aim to increase energy efficiency through manufacturing chips in the most advanced CMOS process and implementation of 3D integration.

We provide semiconductors as a service, rather than sell them as a product. It is the role of RaaS to develop the necessary technologies to achieve that goal.

RaaS has planned to bring researchers from member companies together at the Mejirodai International Village campus of the University of Tokyo where they can conduct research while providing stimulation to each other. Unfortunately, because of COVID-19, RaaS activities have also been limited to center around remote work.

In FY2021, RaaS applied to and was accepted by the "Project for Research and Development of Enhanced Infrastructures for Post 5G Information and Communications Systems / Development of Advanced Semiconductor Manufacturing Technology (b) Development of Advanced Semiconductor Backend Processing Technology (More than Moore)" of the New Energy and Industrial Technology Development Organization (NEDO). The development theme is "(b2) Implementation Technology for Edge Computing." As a result, we were joined by SCREEN Holdings Co., Ltd., DAIKIN INDUSTRIES, Ltd., FUJIFILM Corporation, and Panasonic Connect Co., Ltd. as new members of RaaS, adding technology R&D to the system R&D which we have been pursuing from the beginning.

In the system R&D, RaaS completed the design of and taped out our first chip in the 7nm process in FY2021. It is our biggest accomplishment of the year where we were able to complete the design and prototyping of a chip using the latest CMOS technology with complicated design rules in less than a year since our inception.

In the technology R&D, based on the NEDO project mentioned above, our efforts have been focused on the establishment and implementation of technology for WoW (wafer-on-wafer) and CoW (chip-on-wafer) integration using Cu-Cu low temperature bonding as part of our direct bonding 3D integration technology development (equipment and process development for WoW and CoW).

## Table 2.1.1List of FY2021 d.lab Partner Mem-<br/>bers (in Japanese phonetic order)

Advantest Corporation Analog Devices, Inc. Alchip Technologies, Limited Ushio Inc. Organo Corporation **KIOXIA** Corporation Gigaphoton Inc Samsung R&D Institute Japan Siemens EDA Japan JSR Corporation Showa Denko Materials Co., Ltd. Shin-Etsu Chemical Co., Ltd. SCREEN Holdings Co., Ltd. Sumitomo Corporation Socionext Inc. Sony Group Corporation DAIKIN INDUSTRIES, Ltd. Dai Nippon Printing Co., Ltd. **TDK** Corporation **DISCO** Corporation Tokyo Electron Limited TOKYO OHKA KOGYO CO., LTD. Toppan Inc. Nikon Corporation IBM Japan, Ltd. Cadence Design Systems, Japan Nihon Synopsys G.K. JEOL Ltd. Panasonic Corporation Panasonic Smart Factory Solutions Co., Ltd. Semiconductor Energy Laboratory Co., Ltd. Hitachi, Ltd. Fujitsu Limited **FUJIFILM** Corporation Micron Memory Japan, K.K. Mitsubishi Chemical Corporation Mitsubishi Electric Corporation **MIRISE** Technologies Miraxia Edge Technology Corporation Murata Manufacturing Co., Ltd. **Renesas Electronics Corporation** ROHM Co., Ltd.

| Date       | Title                                                                     | Presenter(s)                                                                                                                                                                                                                                                                                                                  |

|------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5/19/2021  | FY2021 d.lab Partnership Program Kick-<br>off & Special Keynote           | Prof. Akihiro Nakao, School of<br>Engineering                                                                                                                                                                                                                                                                                 |

| 6/29/2021  | Business Restructuring Grant Program                                      | Prof. Tadahiro Kuroda, d.lab<br>Mr. Kento Tsuda, Deputy<br>Director, Small and Medium<br>Enterprise Agency, METI                                                                                                                                                                                                              |

|            | 2021 VLSI Symposia Report                                                 | Prof. Ken Takeuchi, d.lab<br>Prof. Makoto Ikeda, d.lab<br>Mototsugu Hamada, Project<br>Prof., d.lab<br>Prof. Toshiro Hiramoto, d.lab<br>Prof. Shinichi Takagi, d.lab<br>Masaaki Niwa, Senior Fellow,<br>d.lab                                                                                                                 |

| 7/21/2021  | Seminar Announcement                                                      | Yoshio Mita, Associate Prof.,<br>d.lab                                                                                                                                                                                                                                                                                        |

|            | ECTC 2021 Report                                                          | Toru Ogawa, RaaS Advisor<br>Takeshi Takagi, Principal Re-<br>searcher, d.lab<br>Tadatomo Suga, RaaS Advisor<br>Masaaki Niwa, Senior Fellow,<br>d.lab                                                                                                                                                                          |

| 8/18/2021  | d.lab Partners Technology Exchange (1)                                    | Mr. Takafumi Mizojiri, Ushio<br>Inc.<br>Mr. Shogo Arita, Analog Devic-<br>es, Inc.<br>Mr. Takahiro Tanabe, Showa<br>Denko Materials Co., Ltd.<br>Mr. Takaya Ogawa, KIOXIA<br>Corporation<br>Mr. Haruyuki Baba, Semicon-<br>ductor Energy Laboratory Co.,<br>Ltd.<br>Mr. Tatsuo Noguchi & Mr.<br>Keiichiro Uchida, Toppan Inc. |

| 9/22/2021  | d.lab Partners Technology Exchange (2)                                    | Mr. Koji Ichimura, Dai Nippon<br>Printing Co., Ltd.<br>Mr. Hiroyuki Furuzono & Mr.<br>Eijiro Sasa, Alchip Technolo-<br>gies, Limited<br>Mr. Kenji Oishi, Gigaphoton<br>Inc<br>Mr. Yuta Komatsu, Nikon<br>Corporation<br>Mr. Shunsuke Teranishi, DIS-<br>CO Corporation<br>Mr. Hiroshi Sugawara, Organo<br>Corporation         |

| 11/17/2021 | Special Technology Seminar "Gastrono-<br>my, Robotics, and Semiconductor" | Mr. Masahiro Fujita, Sony<br>Group Corporation                                                                                                                                                                                                                                                                                |

|            | d.lab Partners Technology Exchange (3)                                    | Mr. Satoshi Fujimura, TOKYO<br>OHKA KOGYO CO., LTD.<br>Mr. Hirotaka Hara, Renesas<br>Electronics Corporation                                                                                                                                                                                                                  |

## Table 2.1.2 List of FY2021 d.lab Partnership Program Seminars

| 2-2                                             |     |

|-------------------------------------------------|-----|

| Chapter2                                        |     |

| 2 <sup>2</sup> Chapter2 Activity Report of d.l. |     |

| ort of d.l.                                     | ~~~ |

ab

| 12/17/2021 | imec Day         | Dr. Naoto Horiguchi, imec        |

|------------|------------------|----------------------------------|

| 12/1//2021 | Infec Day        | 0                                |

|            |                  | Dr. Eric Beyne, imec             |

| 12/22/2021 | TSMC Day         | Mr. Yutaka Emoto, TSMC           |

|            |                  | Japan                            |

|            |                  | Mr. Kinya Ichikawa, TSMC         |

|            |                  | Japan                            |

| 1/19/2022  | IEDM2021 Report  | Prof. Toshiro Hiramoto, d.lab    |

|            |                  | Prof. Shinichi Takagi, d.lab     |

|            |                  | Masaharu Kobayashi, Associate    |

|            |                  | Prof., d.lab                     |

|            |                  | Prof. Ken Takeuchi, d.lab        |

|            |                  | Takeshi Takagi, Principal Re-    |

|            |                  | searcher, d.lab                  |

| 3/2/2022   | d.lab Day        | Prof. Shinichi Takagi, d.lab     |

|            | ,                | Prof. Makoto Ikeda, d.lab        |

|            |                  | Prof. Ken Takeuchi, d.lab        |

|            |                  | Yoshio Mita, Associate Prof.,    |

|            |                  | d.lab                            |

|            |                  | Masaharu Kobayashi, Associate    |

|            |                  | Prof., d.lab                     |

| 3/23/2022  | ISSCC2022 Report | Prof. Makoto Ikeda, d.lab        |

|            | 1                | Prof. Ken Takeuchi, d.lab        |

|            |                  | Tetsuya Iizuka, Associate Prof., |

|            |                  | d.lab                            |

|            |                  | Mototsugu Hamada, Project        |

|            |                  | Prof., d.lab                     |

|            |                  | Atsutake Kosuge, Lecturer, d.lab |

|            |                  | moutane mosuge, Lecturer, d.iab  |

## 2.2 Advanced Device Research Division

Advanced Device Research Division is working for the development of three-dimensional (3D) integration technology and advanced device technology aiming at ten times higher energy efficiency of semiconductor systems in the data-driven systems.

In 2021, we launched a new project of the next-generation 3D integration technology.

Recently, the computing technology for processing large amount of data is becoming more important and the energy consumption by frequent data transfer between memories and processors is a severe problem. To solve this problem, the direct bonding 3D stack technology, where the data transfer distance is shortened by direct bonding of chips or wafers, has attracted much attention.

This year, in the NEDO project "Post 5G Informa-

tion and Communication Technology Infrastructure Reinforcement Research and Development Project / Development of Advanced Semiconductor Manufacturing Technology (Subsidy)", the Research Association for Advanced Systems (RaaS) which d.lab is the headquarters of technology research association on 3D integrated technology, proposed "Direct 3D Stacking Technology Development (Development of Equipment and Processes for WoW (Wafer on Wafer) and CoW (Chip on Wafer))", and this proposal was adopted. Currently, we are working with RaaS member companies to develop and implement chokepoint technologies related to WoW and CoW bonding technologies using low-temperature hybrid bonding of Cu-Cu.

## 2.3.1 Overview of Platform Design Research Division

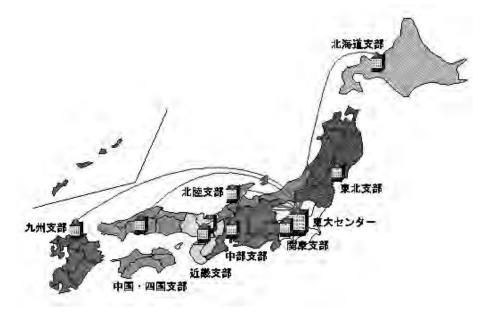

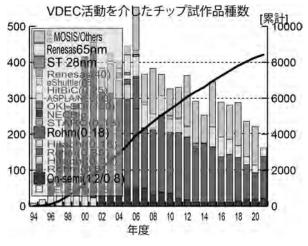

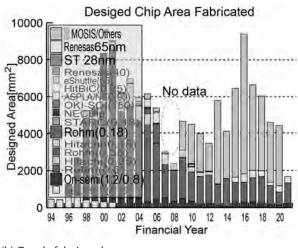

Since its establishment in 1996, the VLSI Design and Education Center (VDEC) at the University of Tokyo has been developing projects that contribute to integrated circuit design education at universities and technical colleges in Japan, based on the three major roles: "spreading the latest information on VLSI design and education," "providing licenses of CAD tools," and "supporting on VLSI chip fabrications for academic use." On October 1, 2019, VDEC has been re-organized into Systems Design Lab (d.lab), Graduate School of Engineering, the University of Tokyo as part of an organizational restructuring aimed at strengthening integrated circuit related activities in the University of Tokyo's semiconductor integrated circuit-related activities. The Platform Design Research Division of d.lab continues to carry out the functions of the VDEC and continues "VDEC activities" seamlessly. Here, the outline of "VDEC activities" of the FY2021 is reported below.

The missions of VDEC are for advancement of researches and education on LSI design in public and private universities and colleges in Japan and send many distinguished VLSI designers into industry. After 25 years of VDEC establishment, educations on CAD software, LSI design and design flow in universities have been well established. On the other hand, advancement on nano-meter CMOS technologies forces design flow and CAD software complicated. We have been continuing CAD tool seminar by the lecturers from EDA vendors for twice a year. We hold the seminar in VDEC and provide distance learning through video streaming. We expect spread of the up-to-date LSI design methodology by using CAD tools.

In order to make it more convenient for the participants, the seminars have been held only in Tokyo since 2009, and at the same time, the seminars have been broadcasted to individual participating lab. The VDEC expects that the latest CAD use-case will be shared among labs through the seminar organized by VDEC, and will be a trigger to spread the technology nationwide. In FY2020, all seminars will be conducted online. Some items were conducted in the form of on-demand plus live Q&A sessions to improve the convenience of participation. In addition, in view of the current situation where the tool-chains of various companies are becoming more complex and it is difficult to fully use the introduced tools, lectures on the tool-chains recommended by each tool vendor were also held in conjunction with the individual tool seminars. From the end of FY2019, we received permission from each EDA vendor to use EDA tools from home, to avoid delay&slowdown in integrated circuit design research and education in Japan.

### 2.3.2 Status of Education at Platform Design Research Division

The LSI Design Flow Seminar is designed to educate the basic concepts of LSI design and to provide handson experience of practical design examples using multiple CAD tools. For this purpose, VDEC has been organizing LSI design education seminars as well as "Refresh Seminar" for re-education programs for engineers. "Analog Design Course", and "RF Design Course," were held from June to September. All of these courses are experiential education courses with exercises, and experienced instructors from major universities are invited as lecturers. In addition, "Transistor Level Design in VDEC Environment (Course VT)" and "Digital Design Methodology in VDEC EDA Environment (Course VD Course VT)" and "VDEC Digital Design Methodology Course (Course VD)" are conducted for designers in universities. The "Refresh Seminar" are all held online in FY2021, and as a result, the number of participants has increased compared to previous years.

In addition to these seminars, VDEC holds the "VDEC Designers' Forum" once a year, mainly for young faculty members and students. This is a workshop-style meeting, where participants bring their design cases and exchange their successes and failures, in addition to invited lectures from companies and universities. In FY2021, the VDEC Designer Forum had been held online. Since FY2011, the "IEEE SSCS Japan Chapter VDEC Design Award" has been presented as an award for VDEC activities. The final judging and awarding of the "IEEE SSCS Japan Chapter VDEC Design Award" has been held at VDEC Designers' Forum since 2011, and in 2021, the IEEE SSCS Japan Chapter VDEC Design Award will be presented to Mr. R. Okada of Nara Institute of Science and Technology. Three VDEC Design Award Excellence Awards, (Mr. R. Okada (Nara Institute of Science and Technology), Mr. A. Matsuoka(The University of Tokyo), and Mr. H. Sakai(Tokyo University of Science)), and three VDEC Design Award Encouragement Prizes (Mr. T. Tsujimura(Nagoya University), Mr. K. Sahara(Tokyo University of Science), and Y. Mori(Nara Institute of Science and Technology)), and three VDEC Design Award Commendation Prizes for Idea Contest (K. Kawahara(Tokyo University of Science), S. Mitsuno(the University of Tokyo), and T. Fukushima(Tokyo Denki University)).

Although the educational system through such seminars and forums has enabled students to learn the basics of LSI design, they still face various difficulties in actual LSI design situations. For beginners, setting up the CAD software is the biggest problem. Even after setting up the software, they are often baffled by the "difficult error messages" issued by the CAD software. VDEC users can register for the "CAD mail group" and the "Prototyping Technology User Group" on the VDEC website, where they can post their questions and ask for help. The registered users of the mail groups are not obligated to respond, but in most cases they can get help from experienced users within a few hours or days. We hope that you will take advantage of this system to help solve your problems.

## 2.3.3 Publications related to Platform Design Research Division

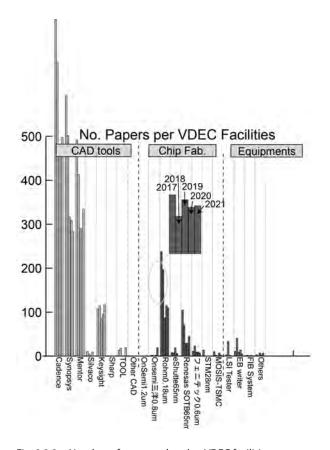

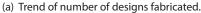

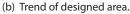

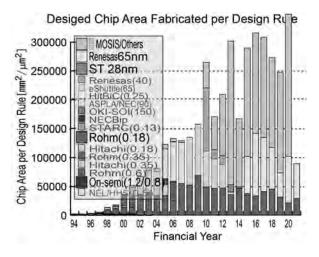

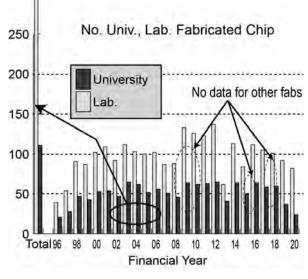

Figure 2.4 shows the use of the VDEC facility in the published literature related to VDEC. It can be confirmed that CAD software is widely used in writing papers. Since CAD software is often used not only in chip design but also in the preparation stage of chip prototyping, its contribution as a tool to demonstrate the basic idea of the research is also significant.

#### 2.3.4 Report on AI Chip Design Center

VDEC and the AIST have been jointly commissioned by NEDO to develop a common platform technology for accelerating AI chip development under the "Innovation Promotion Project for Accelerating AI Chip Development / R&D Item 2: Development of Common Platform Technology for Accelerating AI Chip Development" since 2018. In this project, we have established an EDA utilization and design environment for venture companies and small and medium-sized enterprises(SMEs) in Japan, and are working as an "AI chip design center(AIDC)". In this activity, in addition to the introduction of EDA tool licenses that allow venture companies and small and medium-sized companies to prototype up to engineering samples, we have introduced IP for 40nm and 28nm, and are also providing a large-scale, highspeed design and verification environment using a hardware emulator, which was introduced with a subsidy from the Ministry of Economy, Trade and Industry at the start of this project. In FY2020, we have designed a SoC platform with NoC, PCIe, DDR4, etc., and multiple functional IP cores, and taped out the platform as a SoC with multiple AI IP cores designed by multiple users, and after almost 1-year delay, we have received assembled chip in the beginning of Jan. 2022, and after one week we could evaluate most of SoC functionalities and by the end of March 2022, almost all of Ips got fully verified. In order to further strengthen this activity, we are accelerating our research by establishing the "AIST-The University of Tokyo AI Chip Design Open Innovation Laboratory" (AIDL) in the Takeda Building, Asano Campus, The University of Tokyo on September 1, 2019.

### Table 2.3.1 Chip fabrication schedule

## [CMOS 1.2µm 2P2M] On-Semiconductor(Former Motorola Japan)

|        | Chip application deadline | Design deadline | Chip delivery |

|--------|---------------------------|-----------------|---------------|

| 2022#1 | 2022/7/4                  | 2022/9/26       | 2022/12/19    |

| 2022#2 | 2023/1/10                 | 2023/3/27       | 2023/6/26     |

## [CMOS 0.18µm 1P5M(+MiM)] Rohm

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2022 #1 | 2022/4/4                  | 2022/6/27       | 2022/10/14    |

| 2022 #2 | 2022/6/13                 | 2022/9/5        | 2022/12/23    |

| 2022 #3 | 2022/8/1                  | 2022/10/24      | 2023/2/11     |

| 2022 #4 | 2022/12/5                 | 2023/2/27       | 2023/6/16     |

## [SOTB CMOS 65nm]

|         | Chip application deadline | Design deadline | Chip delivery |

|---------|---------------------------|-----------------|---------------|

| 2022 #1 | 2022/6/13                 | 2022/7/25       | 2023/1/21     |

| 2022 #2 | 2023/1/23                 | 2023/3/6        | 2023/8/26     |

## 2.3.5 Plan for FY 2022 "VDEC Activities" of Platform Design Research Division

In FY2021, we will continue the VDEC Activities for academics as before.

#### [Design related information dispatching/Seminar]

We will continue holding the following seminars: (1) CAD tools seminars which have been continued since 1997, (2) "Refresh seminar" since 1998, (3) "Designer' Forum" since 1997. We will also continue seminars for LSI tester usage at VDEC and sub-centers, workshops on LSI testing technologies initiated by D2T.

#### [CAD tool support]

1500

1200

900

600

300

0

00 02 04 06 08 10 12

We will continue Cadence tools, Synopsys tools and Mentor tools as the main stream design tools. We will continue analog RF design environment, GoldenGate and ADS by Agilent, C-based design environment, BachC by Sharp. In addition, we continue trial of several CAD tools, such as layout platform, Lavis by TOOL. Design debugging platform from SpringSoft has merged into Cadence tools and will be continued.

#### [Chip fabrication services]

We will continue chip fabrication services for  $0.18 \,\mu$  m CMOS by Rohm,  $0.8 \,\mu$  m CMOS by On-semiconductor-Sanyo, SOTB 65nm CMOS by Renesas Electronics, and IHP SiGeBiCMOS 0.18um as the regular services.

In addition to the above. We will continue to develop an "AIDC" activities, in collaboration with AIST. We will introduce a logic emulator for large-scale AI digital chip design verification, and maintain and operate EDA licenses for industrial applications. The main objective of this project is to provide small and medium-sized venture companies with a development environment for AI chip design, evaluation, and verification in order to accelerate the development of AI chips, but we also plan to improve the environment for use by universities in order to promote university-originated companies in the field of AI-related integrated circuits.

Fig. 2.3.1 Trends of number of papers through VDEC activities.

**Financial Year**

16 18 2021

14

No. Papers through VDEC Activities

発表文献数

Fig. 2.3.2 Number of papers related to VDEC facilities.

## 2.4 Platform Device Research Division

#### 2.4.1 Mission

D.lab platform device research division aims at providing every researcher with three essential elements for research on new devices. The division is with around 30 staffs, powered by Dr. Yoshio Mita, the playing division director who himself actively performs experiments in the Cleanroom as a leading researcher, and operated in collaboration with related departments (such as Institute of Engineering Innovation, Electrical Engineering and Information Systems, and Mechanical Engineering) in terms of human and budget resources. Especially in the year 2021, thanks to the invaluable help of Prof. Yuji Suzuki, vice dean for education, we could launch new subcontracting system to the Ph.D student as "excellent Ph.D", in order that they help the team by mentoring all junior members on behalf of experienced senior member in TakedaSCR. Research in emerging fields of semiconductor electronics devices (such as integrated circuits), sensors and microsystems requires three essential elements: (1) fabrication machines with stupendous amount of budget, (2) rich accumulation of fabrication technology knowledges, and (3) research capability to develop new technologies required for new devices. In Japan, these three elements had been prepared and kept in an individual research group until

the end of 20<sup>th</sup> century. However, due to the technology trends towards advanced fabrication over larger-scale wafers, it has become almost impossible for a research group to purchase and maintain the cutting-edge fabrication machine line, in the 21st century. Originally, it was impossible for every research group in universities, companies, research institutes, and NPOs, to exclusively "own" such large-scale facility and necessary budget by themselves; If researchers wish to "cooperate" with the other researchers in a platform, which is equally open to everybody, they can "effectively own" the most advanced "open platform", and thereby the cutting-edge research activities can be held anywhere in Japan. This is the principle of d.lab's open device platform, which is in fact a lateral expansion of "shared economy model in VLSI design and fabrication" to micro-nano fabrication and measurement research field, originally established by VDEC for Japan in 1996.

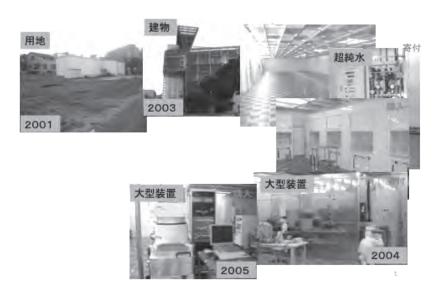

Towards that end, d.lab Platform Device Research Division takes full advantages of spaces (of its own and of open rental) in Takeda Sentanchi Building. The building was inaugurated in December 2003, thanks to the enormous donation in 2001 from Mr. Ikuo Takeda (founder of Advantest) to the faculty of engineering (Dean was Professor

Fig2.4.1 Development of Takeda Sentanchi Supercleanroom

Fig.2.4.2 List of equipment under d.lab Platform Device Research Division

Hiroshi Komiyama) as well as VDEC (director was Professor Kunihiro Asada). In the building, a 600m<sup>2</sup>-square supercleanroom including "official ISO3 (a.k.a. federal class 1. Once measured as ISO1)" area (Fig.1). The cleanroom and affiliated experimental rooms are equipped with cutting-edge nanofabrication and measurement machines, total valued over 3.9 billion yens (33M euros). The users can openly use such nice machines really inexpensively.

Over 70 apparatuses are openly accessible (Fig.2), including, "world's fastest" large-area direct electron beam (EB) writing machine Advantest F5112+VD01, which has been donated according to the wise decision of Mr Ooura, a chairman of Advantest, fine EB writer Advantest F7000S-VD02 and Silicon Deep Reactive Ion Etching machine SPTS MUC-21 ASE-Pegasus, both purchased by Japanese government's supplemental budget (known as Abenomics, the first arrow), and the scanning electron microscope (SEM) Hitachi Regulus SU8230 that provides highest-class resolution among those obtainable by research laboratory. The machines can cover most of the research steps in nanotechnology, which are cleaning, film deposition, lithography, etching, packaging and characterization. Not all apparatuses are yet installed in Takeda Building, however due to nationwide platform network, researchers can access in another equivalent nanofabrication platform center(s).

### 2.4.2 "Takeda Sentanchi Supercleanroom" cooperation platform

The platform is called "Nanotechnology Platform UTokyo Nanofabrication site" according to the MEXT's national project, or simply "Takeda Sentanchi Cleanroom" (in short, Takeda CR). The platform is widely open to those who share the "value of cooperation". The most important understanding for every user is the platform must not be considered as a simple outsourcing agent; being understood the value of "own help, mutual help, and public help", the participant can drastically minimize costs (personnel, budget, and time), which should have otherwise been totally covered by each researcher, and can directly jump into advanced research. Key Performance Indicators of such benefits are as follows: over 7.7 billion yens for installation cost of building and equipment, over 300 million yens for yearly operating cost, and reduction of over 20 years' leading time to acquire know-hows in advanced fabrications. These benefits have attracted many research groups. Since ten years, the number of research groups who sent us the letter of consensus exceeded 456. Over 900 members are yearly subscribed (including renewal and new subscription). In year 2020, over 550 persons have used cleanroom and their total access count exceeds 16,000.

Operation principle is also "own help, public help, and mutual help". Budgetwise, each term of the principle corresponds to: (1) User's payment to participate budget acquisition (charged according to the officially-approved d.lab's internal rule), and (2) national budget allocated to d.lab platform research division, MEXT Nanotechnology Platform project, and (3) major laboratories (who rent space in Takeda Building for their research work) as well as research projects with d.lab operation laboratories (such as Mita Lab). Of course, each budget category is righteously dispensed in perfectly following its own rule defined by corresponding laws and ordinances. The yearly operation cost of 300 million yens are composed of equipment installation, electricity and water fees, maintenance, and personnel. National Universities have acquired budget flexibility since the date of private agency statuses. It helps a lot to ensure staff employment as well as small to middle sized equipment acquisition.

Platform Device Research Division staffs acquire implicit information for future fabrication technologies, due to daily help to massively parallel research projects. The team develops technologies with high demand and universality and make them accessible by publishing papers.

Moreover, taking full advantage that PDRD is a division of d.lab, the team has been developed for over 10 year, a reliable research scheme for integration of LSI and MEMS devices, known as "Integrated MEMS research domain". As summarized in a peer-reviewed journal [1], through VDEC function of d.lab "LSI foundry", a specific LSI circuit silicon wafers are fabricated through company (such as Phenitec Semiconductor). Then the wafer is "post"-processed in an open nanofabrication platform including Takeda Sentanchi Supercleanroom. The critical advantage of such scheme is that researchers can "easily" obtain silicon wafers with transistor circuits, which has been really difficult for university cleanrooms to acquire reliability, and can fabricate by themselves specific MEMS that no foundry company can provide. Namely, researchers can produce "World's first functionality" with "World's highest quality". Such a flexible scheme is unique in the world. Yearly one multi-chip fabrication is performed (pre-fixed participants upon request), including collaborative research works with industries.

[2] Y. Mita et al., Japanese Journal of Applied Physics,56, p. 06GA03, 2017 (2017) DOI: 10.7567/JJAP.56.06GA03

## 2.4.3 Activity Report 2021 of Platform Device Research Division

[Prize] The MEXT Nanotechnology Platform Project gives prizes for good usage of platform. Every year, several projects are selected by specialists' award committee, among solicited candidates selected from over 3000 research project reports. Among the projects that PDRD have solicited, we won again the 1st prize "Best use award" on "Silicon MEMS monolithic SPR spectroscopy sensor by using plasmonic structure" (Fig.3). Note that our division has been awarded consecutively for three years, including two last years as the best use award. The awarded group are UEC Tetsuo Kan's group. It is about MEMS devices that can make selective spectroscopy enhanced by nanostructure.

[No infection case & no decrease in platform uses] In the year 2021, we also continued strict but acceptable anti-pandemic protocol. Due to the influence of Omicron variant, which is less toxic but much more contagious, we identified three positive cases (of maintenance company as well as user), but zero transfection has been obtained.

[Post-Nanotech platform national project] The major part of "public" help for cleanroom has been covered by MEXT Nanotechnology platform. Nanotechnology platform project will end his period at the end of financial year Reiwa 3rd (31/Mar/2022); MEXT has started another national project, by officially stating "use heritage of nanotech platform", for digital transformation (DX) in materials including MEMS devices. The name of the new project is called "Material DX". Structurally speaking, material DX have adopted "research domain hub-andspoke" system, in contrast with Nanoplat's "technology domain system" composed of characterization, nanofabrication, and material syntheses.

d.lab PDRD has been merged with Nano Engineering Center of Institute of Engineering Innovation and Information Technology Center to form a strong hub team, under presidency of Professor Yuichi Ikuhara. The team has been highly appreciated by the evaluation committee and was granted for 10-year project's "hub" site. Following the year 2020, MEXT has granted us a big supplemental budget for our proposal to enhance performance of our cleanroom that will take place at mid-FY2022. Also, d.lab was awarded by MEXT's "Next generation X-nics research site" and also supplemental budget has been granted. In total, we have identified 4500 millions of yens to complete competitive Cleanroom; yielding 300M yens per year if we renew everything at every 15 years.

Fig.2.4.3 Group photo after award ceremony

## 2.5.1 Introduction of ADVANTEST D2T Research Department

## 2.5.1.1 Aim of establishing ADVANTEST D2T Department (former D2T research division)

ADVANTEST D2T research division was established in VDEC in October 2007. As the name suggests, it is financially supported by ADVANTEST Corporation.

The aim of establishing ADVANTEST D2T research division was to promote the research and education environment with regard to VLSI testing in all universities and colleges in Japan. "D2T" signifies that we consider not only design but also testing. Through our activities, we hope to provide expertise in design and testing for the industry. In addition, we are exchanging researchers with those of other universities and research institutes both in Japan and overseas. Moreover, D2T research division is suitable for collaborations with the industry because VLSI testing is one of the most practical research topics in the industry. On the basis of these activities, our final goal is to become a center of excellence of VLSI testing in Japan.

D2T research division has spent a total of 12 years to develop the first (Oct. 2007 – Sep. 2010), second (Oct. 2010 – Sep. 2013), third (Oct. 2013 – Sep. 2016), and fourth (Oct. 2016 – Sep. 2019) phases. D2T activity report of 2021 presents the last financial year, i.e., Oct. 2020 – Sep. 2021, of the fifth phase. Systems Design Center, School of Engineering, the University of Tokyo has been established in Oct. 2019, and Advantest D2T research department is within the center. D2T research department primarily focuses on D2T research activities and education. The fifth project phase (Oct. 2019 onwards) of D2T project was commenced by courtesy of ADVANT-EST Corporation. The details pertaining to the activities of our group are presented in the following sections.

### 2.5.1.2 Members of ADVANTEST D2T Division

| Project Professor            | Masahiro Fujita       |  |

|------------------------------|-----------------------|--|

| Postdoctoral research fellow | Zolboo Byambadorj     |  |

| Project Lecturer             | Akio Higo             |  |

| Researcher                   | Koji Asami (Advantest |  |

|                              | Laboratories Ltd.)    |  |

| Researcher                   | Masahiro Ishida (Ad-  |  |

|                              | vantest Corporation)  |  |

| Researcher                   | Takahiro Yamaguchi    |  |

| Assistant Clerk              | Makiko Okazaki        |  |

#### 2.5.2. Report of the 16th D2T Symposium

The 16th D2T Symposium was held on September 15, 2021, online (a part of the talk is hybrid). This year, we invited the following overseas lecturers to introduce their research on biosystems, BioMEMS, Memory, 3D integration, and Design Optimization, AI chips: President of the University of Tokyo, Professor Teruo Fujii, director of d.lab, Professor Tadahiro Kuroda, Professor Wayne Luk from Imperial College London, Professor Alex Orailoglu from University of California, San Diego, Fellow of the University of Tokyo and Professor Tim Cheng from Hong Kong University of Science and Technology, Professor Mehdi Tahoori from Karlsruhe Institute of Technology, Dr. Shin-ich Ouchi from AIST for their distinguished research topics. Dr. Zolboo presented the recent D2T research activities.

We sincerely appreciate each participant for their contributions to the symposium. We look forward to greater participation again at the next symposium.

| 10:00 | Opening Remarks                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------|

|       | Tadahiro Kuroda (Director, d.lab, School of Engineering, the University of Tokyo)                                  |

|       | Yoshiaki Yoshida (President & CEO, ADVANTEST CORPORATION)                                                          |

| 10:15 | Session 1 (Chairpersons: Yoshio Mita, Masahiro Fujita, d.lab, the University of Tokyo)                             |

|       | Microfluidics for Cellular and Molecular Systems                                                                   |

|       | Teruo Fujii, President (the University of Tokyo)                                                                   |

|       | Meta-programming Strategies for Multi-Target Design Optimisation                                                   |

|       | Wayne Luk, Professor (Imperial College London)                                                                     |

| 12:00 | Lunch                                                                                                              |

| 13:00 | Session 2 (Chairperson: Tetsuya Iizuka, d.lab, the University of Tokyo)                                            |

|       | Time Performance Improvement by Agile Design and 3D Integration                                                    |

|       | Tadahiro Kuroda, Professor (d.lab, the University of Tokyo)                                                        |

|       | Design of Reliable and Efficient Deep Learning Processing Systems                                                  |

|       | Alex Orailoglu, Professor (University of California, San Diego)                                                    |

| 14:45 | Session 3 (Chairperson: Makoto Ikeda, d.lab, The University of Tokyo)                                              |

|       | Ratio based Resistive Memory Cells for Low Error Rate and High Energy Efficiency                                   |

|       | KT. Tim Cheng, Professor (Hong Kong University of Science and Technology and Fellow, the University of Tokyo)      |

|       | AI-Accelerator Proof of Concept by a Multi-IP Chip Project                                                         |

|       | Shin-ichi O'uchi (S. O'uchi)                                                                                       |

|       | Laboratory Team Leader, AIST-UTokyo AI Chip Design Open Innovation Laboratory (AIDL)                               |

|       | National Institute of Advanced Industrial Science and Technology (AIST)                                            |

| 16:30 | Session 4 (Chairperson: Masahiro Fujita, d.lab, The University of Tokyo)                                           |

|       | Recent D2T research department progress                                                                            |

|       | Akio Higo, Lecturer (d.lab, The University of Tokyo)                                                               |

|       | Analysis and Calibration Techniques of Modulated Wideband Converter for High-Precision Sub-Nyquist Sampling System |

|       | Zolboo Byambadorj, Doctoral research fellow (d.lab, The University of Tokyo)                                       |

|       | Computing Paradigms based on Flexible Inorganic Printed Electronics                                                |

|       | Mehdi Tahoori, Professor (Dependable Nano-Computing at Karlsruhe Institute of Technology)                          |

| 18:00 | Closing Remarks                                                                                                    |

|       | Masahiro Fujita (d.lab, School of Engineering, The University of Tokyo)                                            |

## High-Resolution Analog-to-Digital Converter Based on Stochastic Comparators

Takahiro J. Yamaguchi, Akio Higo, Tetsuya lizuka

to explore stochastic This project aims analog-to-digital converter (ADC) architectures. Process variations, together with many factors such as variations in voltage or temperature, lead to mismatched design parameters that produce input-referred offsets and hence cause non-linearity and missing output codes in an ADC. Instead of attempting to suppress such process variations as in conventional ADC, the stochastic ADC approach exploits the stochastic properties of many comparators such as random variation of input-referred offset and Gaussianity of the internal noise to enhance the quantization accuracy. However, the published papers only show that stochastic ADCs are noisier than the conventional flash ADCs [TCAS-I, Vol. 57, no. 11, 2010]. The central limit theorem can be applied to discrete type RVs such as a group of comparators and their sum [A. Papoulis 2000]. It shows that for this discrete RV, many more terms are required in the sum before going convergence to a Gaussian distribution [S. L. Miller 2004]. These results in the adequate number of bits (ENOB) of the stochastic ADC are represented by log44B [TCAS-I, Vol. 57, no. 11, 2010], being smaller than the ENOB of the conventional flash ADC, which is given by log22B. An approach for robustly detecting level-crossing time using stochastic median is investigated to address randomness issues and achieve accuracy.

## High-Performance Analog-to-Digital Conversion Using the Wideband Spread Spectrum and Its Applications

Koji Asami, Zolboo Byambadorj, Akio Higo, Tetsuya Iizuka, Masahiro Fujita

We investigate the compression sampling method to measure low-cost RF devices for IoT and other applications. A 4-channel MWC circuit was fabricated, and we verified our proposed methods to improve the characteristics. We measured and verified characteristics by the Bluetooth and LTE waveforms that used the device under test for RF communication, and this project was closed by the end of March 2021.

### 5G multi-channel/millimeter-wave signal measurement

Koji Asami, Zolboo Byambadorj, Ryogo Koike, Sheng Guo, Nguyen Ngoc Mai-Khanh, Akio Higo, Tetsuya lizuka, Masahiro Fujita

We study and develop fundamental research to measure the millimeter-wave signals in an over-theair environment. In this financial year, we designed and fabricated the planar monopole probe antenna with a high spatial resolution for the near field measurement of the millimeter-wave antenna. We developed algorithms for the near-to-far-field transformation and the identification of probe characteristics. We have established the experimental setup for millimeter-wave measurement and are currently proceeding the verification and the performance improvement by using actual antennas for 5G.

## High-Speed and High-accuracy Multi-Pin Timing CAL for ATE

Masahiro Ishida, Hidaka Otsuka, Tetsuya Iizuka, Toru Nakura, Zule Xe, Akio Higo, Masahiro Fujita

Automatic test equipment (ATE) for Semiconductors has thousands to tens of thousands of signal input and output channels. It requires timing calibration (CAL) to correspond the test signal output's timing to the device under the test (DUT) and the comparison timing of the signals output from the DUT. This research focuses on a high-speed and high-accuracy multi-pin timing CAL method applicable to ATE. In this financial year, we discussed and determined the circuit scheme to realize our research goal that the target accuracy of the timing CAL is at 1 ps. Then, we designed the test element group (TEG) chip for LSI shuttle services in VDEC function at d.lab design platform research division. We discussed the challenges for developing the timing CAL devices, and we decided to fabricate TEG for evaluating the CAL accuracy degradation by the power variation and thermal environment. We designed the TEG layout and LSI circuit using the TSMC 65 nm CMOS process, and we confirmed the target accuracy of 1 ps by simulations. Then, we taped out the design.

function at d.lab design platform research division. We discussed the challenges for developing the timing CAL devices, and we decided to fabricate TEG for evaluating the CAL accuracy degradation by the power variation and thermal environment. We designed the TEG layout and LSI circuit using the TSMC 65 nm CMOS process, and we confirmed the target accuracy of 1 ps by simulations. Then, we taped out the design.

#### 2.5.4 Publication

## Journal

[1] Zolboo Byambadorj, Koji Asami, Takahiro J. Yamaguchi, Akio Higo, Masahiro Fujita and Tetsuya Iizuka, "A Calibration Technique for Simultaneous Estimation of Actual Sensing Matrix Coefficients on Modulated Wideband Converters," IEEE Transactions on Circuits and Systems-I: Regular Papers, vol. 67, no. 12, pp. 5561 - 5573, Dec. 2020.

## Kuroda and Kosuge Laboratory

(http://www.kuroda.t.u-tokyo.ac.jp/index.html)

#### TCI: ThruChip Interface

T. Kuroda, M. Hamada, A. Kosuge, T. Shidei, M. Okada, Wai-Yeung Yip, K. Shiba, T. Omori

TCI is a 3D integration technology that employs inductive coupling between coils created with on chip metal line patterns for data communication across stacked chips. It realizes the same or better performance as TSV (Through Silicon Via) but at a lower cost. This year, we presented research papers on TCI-based 3D SRAM stacking technologies including (a) circuit technology for low-power computation, (b) area efficient coil-design, and (c) computing architecture and AI processing algorithms to use 3D stacked SRAMs efficiently. We presented our achievements at ESSCIRC'21 and EDAPS'21.

#### **TLC: Transmission Line Coupler**

T. Kuroda, M. Hamada, A. Kosuge, Y. Hayashi, Ximing Wang

TLC is a data communication technique between circuit boards by utilizing electromagnetic coupling between transmission lines on them. It solves the issues in conventional connectors such as wearing, reliability against vibration, and impedance mismatch, realizing wireless connectors. This year, through joint research with a company, we conducted research and development of compact and high-density TLC mounting technology for connecting packaged boards and PCBs, and research on fully sealed non-contact connector technology for simultaneous communication of non-contact power supply and TLC in close proximity to each other. GND shielding technology is studied to prevent mutual interference between wireless power transmission and contactless communication.

#### **RFID Tag Chip Design**

T. Kuroda, M. Hamada, A. Kosuge, R. Miura, S. Shibata

We are developing a wireless tag that integrates an antenna and wireless circuits on a tiny chip less than 1 mm square and combine it with an intelligent reader to pursue an extremely low-cost IoE (Internet of Everything) system. This year, we developed a new collision avoidance function that deterministically avoids collisions based on received signals by utilizing adiabatic circuits. We developed a low-power RFID tag circuit using TSMC 0.18m CMOS process by using our proposed the adiabatic logic circuit and presented our experimental results at A-SSCC'21. We have also developed a new bonding-less mounting technology in which the coil mounted on the RFID tag is coupled to the coil on the PCB. A test chip was developed and evaluated using TSMC 0.18um CMOS process, and papers were presented at SSDM'21, ASP-DAC'21, and JJAP'22.

#### Wired-logic AI Processor

T. Kuroda, M. Hamada, A. Kosuge, K. Shiba, Yao-Chung Hsu, R. Sumikawa, F. Hondo

We are studying non-von Neumann AI processors focusing on wired-logic to reduce power consumption. The area efficiency is a bottleneck of the wired-logic processor and it is significantly degraded due to the need to implement a huge number of elements on a chip. Therefore, we have developed two new technologies: (1) a technology to optimize the network by removing unnecessary neurons and synapses, called pruning in the human brain, and (2) a nonlinear neural network technology that incorporates the property of human neurons to use a wide variety of nonlinear functions in the right places to increase the representation capability of the network in order to prune more drastically than before and save the number of elements. In addition, we are developing convolutional wired-logic architecture circuits that reuse circuits in accordance with the processing of convolutional algorithms. Research works regarding MNIST and CIFAR-10 using FPGA were published on IEEE JETCAS and OJCAS respectively.

## mmWave Imaging Radar based Object Recognition

T. Kuroda, M. Hamada, A. Kosuge, Wai-Yeung Yip, S. Suehiro

In harsh environments (bad weather, night, dirt on cameras), conventional human/object detectors utilizing conventional cameras have low accuracy. Since millimeter wave radar technology has high environmental resistance, the radar is promising solution for the harsh environment. However, unlike image recognition, it has a problem in detection algorithm due to low-resolution blur data. In this research, we are developing a new deep learning AI technology that handles millimeter wave images based on a new semi-automatic training data generation technology and develop a highly accurate AI technology for human/object identification. This year, we mainly studied the characteristics of millimeter-wave radar data and the network structure that matches them and developed a camera-radar cooperative semi-automatic learning data generation technique and developed a millimeter-wave radar AI system that can detect the type and location of six types of objects with the same accuracy as image recognition.

## Takeuchi Laboratory (https://co-design.t.u-tokyo.ac.jp/)

#### Computation in memory (CiM)

#### Ken Takeuchi and Chihiro Matsui

We have developed a comprehensive Computation-in-Memory (CiM) simulation platform. The simulation platform has capability to emulate multi-level cell (MLC) and various memory device non-idealities such as uniform/non-uniform conductance variation and shift. The simulation results address that the conductance shift has much more critical impact than conductance variation on inference accuracy in CiM.

### Simulated Annealing

#### Ken Takeuchi, Chihiro Matsui and Naoko Misawa

Memory error tolerant ReRAM-based Computation-in-Memory (CiM) to solve the knapsack problem, one of the combinatorial optimization problems, is proposed. Proposed log-encoding simulated annealing (SA) on ReRAM CiM reduces the array area of ReRAM CiM by 97.6%. To co-design Re-RAM device and SA, error injection is applied. As a result, the asymmetric ReRAM error increases the acceptable bit-error rate (BER) by 10 times and the acceptable bit precision to 5-bit.

#### **In-sensor Computing**

#### Ken Takeuchi and Chihiro Matsui

We have proposes an integration of event-based vision sensor (EVS) and processor (e.g., computation-in-memory, CiM) for low-power processing. By using newly defined characterization method of frame and EVS camera, an event-driven SRAM CiM with partitioned word-line (WL) activation method is proposed for 3D-integration of EVS. The multiple-bit synaptic weights are stored in a set of SRAMs. The proposed CiM for EVS achieves 10-6 times energy efficiency compared with CiM for frame camera.

> Nakamura Laboratory (http://www.hal.ipc.i.u-tokyo.ac.jp/)

#### **IoT Network Security**

#### Hiroshi Nakmaura

Zigbee is a short-range wireless communication protocol and needs low power and low bandwidth at the sacrifice of its short transfer range and slow speed. Due to this nature, it is widely used in small inexpensive sensors and IoTs that run on batteries, As Zigbee adopts indirect communication to achieve low power consumption, it incurs a vulnerability to LDoS attacks. To solve this problem, we proposed a countermeasure method and attacker detection algorithm without consuming large computing resources or power to satisfy the constraints of IoT devices. Through experimental simulation, we confirmed its effectiveness.

#### **Coarse-Grain Reconfigurable Architecture**

#### Takuya Kojima, Hiroshi Nakamura

Coarse-grained reconfigurable architectures (CGRAs) are expected as a promising architecture for wide variety of computing including embedded systems and high-performance computing due to its benefit of high-energy efficiency and programmability. CGRA consists of an array of numerous processing element and its efficiency heavily depends on the quality of compiler which maps applications onto these PEs. So far, we have proposed a novel algorithm called GenMap (A Genetic Algorithmic Approach for Optimizing Spatial Mapping), which is a mappaing framework based on a genetic algorithm. We extend GenMap to handle not only spatial but also temporal reconfiguration and confirmed its effectiveness.

### Lightweight Runtime Environment of ROS2 nodes for Embedded Devices

#### Hideki Takase, Hiroshi Nakamura