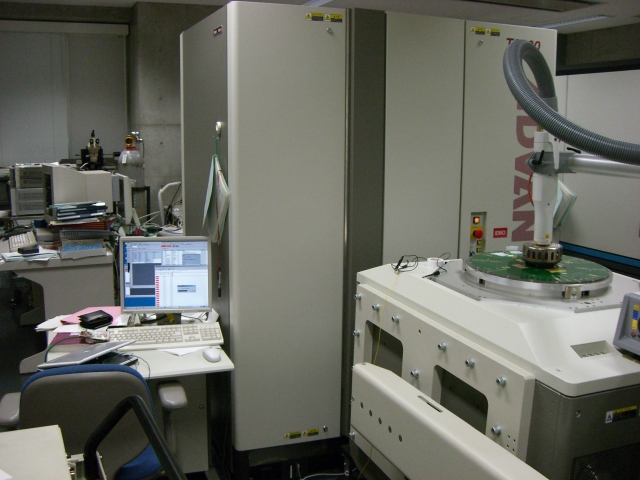

| Digital IO チャネル: | 384 (32ch x 12 Modules) |

| Functional Test Speed: | 250MHz(Normal Rate Mode) |

| 500MHz(Double Rate Mode) | |

| 667Mbps(Double Rate Mode: Driver Only) | |

| Pattern Generators: | 128M word (MAIN)/256M word(SCAN) |

| Multiple Time Domain: | 24 domains (2domains per each Digital Module) |

| Pin Electronics: | -2V to +6V Drive/Compare Range |

| VPP(Hign V Channel): | 13V, ±100mA Maximum Output |

| Other Features: | Scan Test, Mrmory Test, Multiple Time Domain, High Voltage Pin,etc. |

| Device Power Supply: | 24ch (8ch x 3 Modules) |

| Voltage Source: | -2V to +6V at 4A maximum output |

| -2V to +8V at 1A maximum output | |

| Measurement Range: | ±5μA, 50μA, 500μA, 5mA, 50mA, 500mA, 4A |

| Dynamic Load Regulation: | 60mA at Δi = 2A, CL = 2000μF |

| 100mA at Δi = 2A, CL = 200μF | |

| Ganging: | 2 to 64 supplies (256A maximum) |

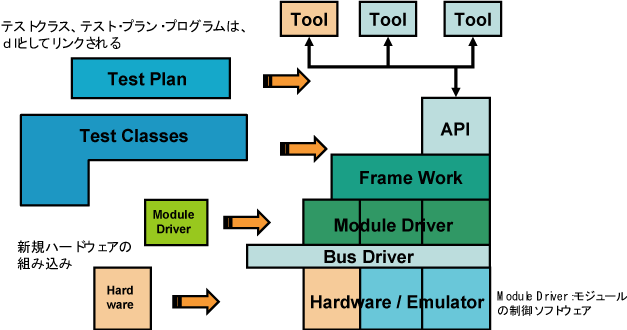

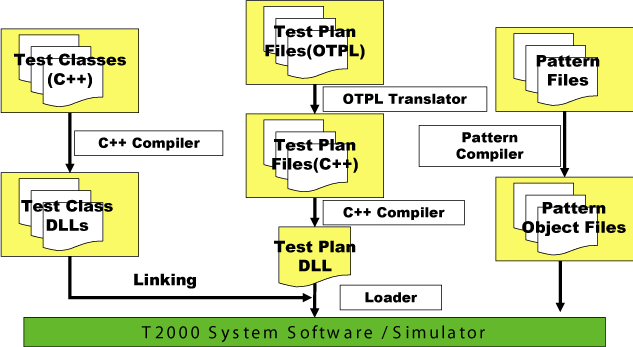

- オープンなSoftware開発環境

- 基本OS: Windows

- 開発環境: MS Visual Studio .NET

- 新規モジュール追加の拡張性

- アルゴリズムの再利用

- テストデータとアルゴリズムの分離

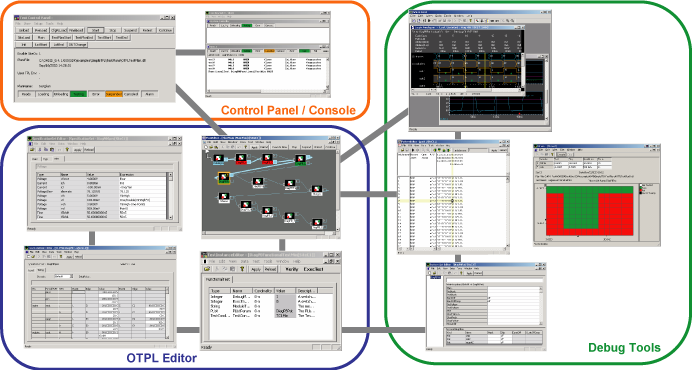

- 充実したツール環境

センター設備リストに戻る

センター設備リストに戻る