平成20年度 東京大学大規模集積システム設計教育研究センター 年 報

VLSI Design and Education Center The University of Tokyo

大規模集積システム設計教育研究センター (VDEC) の2007年度活動報告をお送りします.

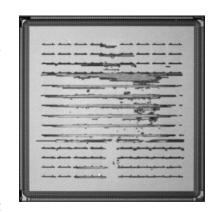

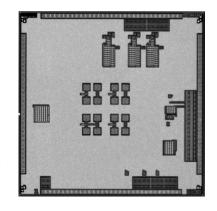

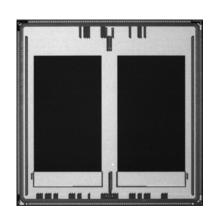

2007年度、VDECのチップ試作事業ではCMOS 90 nmの試作ラン (スターシャトル) を11月にて終了し、新たにCMOS 65 nmの試作ランを開始すべく準備作業をいたしました。結果的に昨年11月の90 nm終了から新たな65 nmの開始までやや期間があき、利用者の方々にはご迷惑をおかけしましたが、本年5月にはSTARC /(株/イーシャトルのご協力によるCMOS 65 nmのテストランを実施することができ、本年8月からは広くご利用いただける予定です。このCMOS 65 nmは従来のものより倍近い配線層を有する先端プロセスであり、これによりわが国の大学から優れた性能のLSIが設計試作されることを期待しています。

VDECの研究組織面では2007年10月に㈱アドバンテストからの寄付研究部門(D2T: Design-to-Test)が設置され、広く設計テスト技術の共同研究が開始されました。この寄付研究部門には海外の著名な研究者を招聘するとともに、アドバンテストからの研究員の方も常駐し、同部門の准教授ポストに着任された小松聡さんとともに研究教育活動を開始しています。これに関連して2008年1月には内外の著名な研究者をお招きした設立記念講演会を開催しました。そのあらましも本年報に掲載しております。

2008年度からは「最後のVDEC流動教官」となった北海道大学の吉澤先生も母校にもどられ、「新VDEC協力教員システム」が正式にスタートしました。これは全国拠点校から選出された協力教員の方々が、VDEC特認准教授の名倉徹さんを軸としVDEC活動を分担支援するシステムであり、各種セミナーやワークショップを企画運営していく予定です。第一歩としてVDECデザイナーズフォーラムも企画を一新し、本年は6月にVDECで開催する予定で準備を進めています。今後、VDECデザイナーズフォーラムは色々な新しい企画を取り込んでゆき「VDEC活動の総会」として位置づけていきたいと考えています。新企画は順次お知らせしていく予定でいますが、皆さんの引き続きのご協力をお願いいたします。

2007年度はチップ試作数の面では、一昨年度終了したCMOS 0.35 umから新規CMOS 0.18 umへの利用者の移行がやや低調に推移し、25%程度減少いたしました。しかし当初手間取った新CMOS 0.18 umの試作組立フローも現在では計画通り順調に進むようになり、今後一層のご利用を期待しています。VDECではできるだけ高性能かつ安価なCMOS試作ランを提供すべく努力してまいりましたが、ご案内のように生活協同組合的試作システムであるため、一定数の利用が安定してあることが必要条件でございます。是非、ご協力のほどお願い申し上げます。

政府も昨年度,産学の人材需給ギャップを心配し「人材育成パートナーシップ」プログラムを開始しました. LSI設計分野は依然として多くの先端産業の要となる分野ですが、この分野の教育・研究を高度化し優れた 人材を多数育成するためも、皆様からの引き続きのご支援ご支持をお願い申し上げる次第です.

2008年6月

(全国共同利用施設)

東京大学大規模集積システム設計教育研究センター

センター長

VLSI Design and Education Center The University of Tokyo

# **2008**

| 「アドバンテス                      | スト D2T 寄附研究部門」設立記念特集 ······2                    |

|------------------------------|-------------------------------------------------|

| 第1章 VDE<br>1.1               | EC 事業の紹介と平成 19 年度事業報告 ······ 15<br>VDEC の活動概況   |

| 1.2<br>1.3<br>1.4<br>1.5     | CAD ソフトウェアの整備<br>平成 19 年度 VDEC 事業報告<br>CAD セミナー |

| 1.7                          | 平成 20 年度の活動計画<br>VDEC 発ベンチャー                    |

| 第 <b>2章 チッ</b><br>2.1        | 試作ラン別一覧                                         |

|                              | チップ種別一覧<br>各チップの詳細                              |

| 第3章 VDE<br>3.1<br>3.2<br>3.3 | 組織概要人事報告                                        |

| 第4章 研究                       |                                                 |

| 4.3 4.4                      | 研究室構成員(平成 19年度)                                 |

| 第5章 付録<br>5.1<br>5.2         | VDEC の利用規定・申し込みガイド                              |

# 「アドバンテスト D2T 寄附研究部門」設立特集

# S. 1 アドバンテスト D2T 寄附研究部門について

# S. 1. 1 アドバンテスト D2T 寄附研究部門 設立趣旨

東京大学大規模集積システム設計教育研究センター (VDEC) は1996年5月に、全国の大学・高専のVLSI設計研究・教育を高度化し、社会に優秀な技術者を数多く輩出することを目的として発足いたしました。VDECではこれらの目的の実現に向け、

- ・VLSIチップ試作支援システム

- ・VLSI用CADソフトウェア環境整備

- ·VLSI教育情報発信

の3つの柱を中心として活動してまいりました.

これまでの11年余の活動を通じ、多くの大学・高専でVLSI設計・試作文化が根付き、活発な設計研究・教育活動が始まっていることが、VDEC利用ユーザ数などの推移から伺い知ることができます。

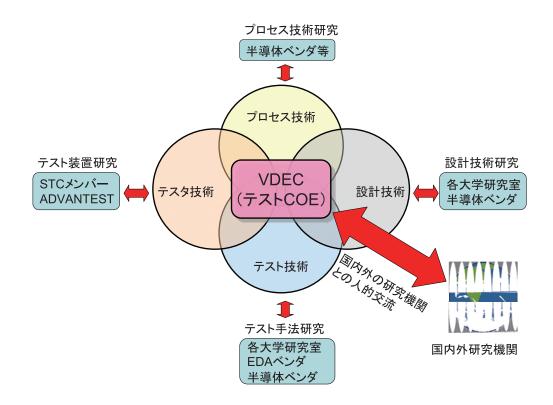

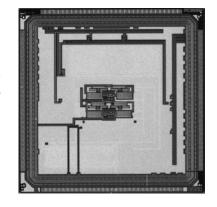

このような状況の中、株式会社アドバンテストからの 寄附金により、「アドバンテストD2T 寄附研究部門」が 2007年10月1日付でVDEC内に設立されました。「アド バンテストD2T 寄附研究部門」は、全国の学生にVLSI の設計からテストまで一貫した研究・教育環境を提供す ることで、テスト設計の専門家となりえる人材を育成す るとともに、SoCの設計に関する研究を支援することを 目的としております.従来、VDECではVLSIの「設計・ 試作」という面からの活動を重点的に行ってまいりま したが、「設計」だけでなく「テスト」の観点からも研 究・教育の中心拠点となるべく"Design to Test (D2T)" の理念のもと、下図に示すような国内の大学・高専にお ける「テスト研究・教育」の拠点として、「テストCOE (Center of Excellence)」を目標として活動を行ってま いります.

# S. 1. 2 アドバンテスト D2T 寄附研究部門 構成員

### スタッフ

特任教授 Kwng-Ting (Tim) Cheng (University of California, Santa Barbara, 2007年10月~2008年6月非常勤, 2008年7月~常勤)

特任准教授 Görschwin Fey (University of Bremen, 2007年12月~2008年6月)

特任准教授 小松 聡

リサーチフェロー Mai Khanh Nguyen Ngoc (2008年 1月~2008年3月)

共同研究員 古川 靖夫 (株式会社アドバンテスト) 事務補佐員 岡崎 真紀子

### 新任の挨拶・抱負

### Kwng-Ting (Tim) Cheng

It is my great pleasure and honor to be a new member in VDEC and to have the opportunity to work with a group of dedicated researchers and educators in Japan's VLSI design, test and verification communities. This unique opportunity creates a foundation for our long-term, close collaboration which I believe will last for many years.

The fast and continuing evolution of design and test technologies and the enormous growth in the complexity and sophistication of VLSI systems has made it such that very few organizations can support the equipment, facilities and R&D required on all fronts of this field. Establishing an international, collaborative research and education program is one solution to addressing such challenges. One of my goals at VDEC is to establish collaborative research projects with University of California Santa Barbara, as well as with other major research centers with which I have been involved, including SRC Focus Center Research Program and NSF International Center on Design for Nanotechnologies. These efforts should be a key step towards the objective of enhancing the education for the next generation of leaders in VLSI design and test, as well as providing the cultural experiences and awareness required of an increasingly globalized workforce.

I am really excited about a productive year at VDEC!!

### Görschwin Fey

Görschwin Fey received his Diploma in Computer Science from the Martin-Luther University, Halle-Wittenberg, Germany in 2001. Since then he has been with the research group of computer architecture at the University of Bremen, Germany, where he received the Dr.-Ing. degree in 2006. He continued his research in Bremen as a post-doctoral researcher. Since December 2007 he is also with the VLSI Design and Education Center at the University of Tokyo where he serves as a visiting professor. His main research interests are in testing, formal verification and debugging of digital circuits and systems.

Working at VDEC is an excellent opportunity to initiate cooperative research. In part, this has already happened: First results of the cooperation between Advantest, Todai and Bremen were accepted for

presentation at the Workshop on Silicon Debug and Diagnosis 2008. Hopefully this is the start of a longer running cooperation.

### 小松 聡

2007年11月より、アドバンテストD2T寄附研究部門の客員准教授(2008年4月より特任准教授)として着任致しました。2001年4月からVDECの助手、助教として主にCAD関連のサポートを中心に活動してまいりましたが、2007年10月のアドバンテストD2T寄附研究部門の設立に伴い、"設計"、"CAD"だけでなく"テスト"についての研究・教育活動を行っていきたいと考えております。

1996年のVDEC設立当初、VDECおよび各サブセンターに試作LSIの評価環境としてLSIテスター、EBプローバー等が配備されましたが、設備の老朽化とともにその稼働状況が芳しくないケースも聞き及んでおります。これらの装置の有効利用のためのサポート、LSIテストの重要性についての啓蒙、などを通じ、国内の大学等でのLSIのテスト環境の向上を進めていきたいと思います。

本寄附研究部門は、国内/海外、大学/産業界の研究者で構成されており、非常に刺激的な研究環境であり、ここで活動できることは非常に光栄に感じております。今後もこれまでに引き続き、国内におけるLSI研究・教育のさらなる向上に貢献できるよう努力してまいりますので、よろしくお願いいたします。

## 古川 靖夫

従来テストは設計と製造の狭間にあり、あまり表舞台に立つことが無い業界でした。しかし、近年のLSIはウイルスの大きさ以下の微細加工が行われるようになり、不良モードやプロセスバラツキが増加しつつあるため、新たな試験手法・装置が必要となっています。また、携帯電話などの機能が一つのチップに入ってしまうというSoC(System On Chip)が現実のものとなり、試験は複雑になる一方です。従って、試験の課題は回路設計、プロセス技術、DFTなどの広範囲に渡る技術の協調がなければ解決することができません。

LSI設計教育の総本山ともいうべき VDEC に D2T という試験研究部門を設けて頂き、微力ながら、そのお手伝いができるということは大変光栄に存じております。 今後、新試験手法の研究にチャレンジするとともに、試験技術者の育成にも貢献していきたいと思います。

# S. 2 「アドバンテスト D2T 寄附研究部門 設立記念シンポジウム」開催報告

アドバンテストD2T寄附研究部門の設立を記念し、2008年1月24日(木)に「アドバンテストD2T寄附研究部門設立記念シンポジウム」を開催致しました。

第1部の東京大学副学長の岡村定矩 教授, 株式会社アドバンテスト表取締役 執行役員社長の丸山利雄氏, 東京大学大規模集積システム設計教育研究センター長の浅田邦博センター長からの挨拶に引き続き, 第2部では国内/海外, 大学/

産業界からの9件の招待講演(うち3件は東京大学VDEC)を行った. いずれも, LSIのテスト, 検証の分野での第一人者であり, 大学・企業から150名を超える方々の参加により, 大変盛況でした.

VDECでは、今後も継続的にLSIのテストに関連したシンポジウム、講演会を予定しておりますので、是非ともご参加ください。

# シンポジウムプログラム / Symposium Program

| 10:00 | 開会の挨拶                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:05 | 副学長挨拶<br>東京大学副学長 岡村 定矩                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10:15 | アドバンテスト社長 挨拶<br>株式会社アドバンテスト代表取締役 執行役員社長 丸山 利雄                                                                                                                                                                                                                                                                                                                                                                                 |

| 10:25 | VDEC センター長 挨拶<br>東京大学大規模集積システム設計教育研究センター長 浅田 邦博                                                                                                                                                                                                                                                                                                                                                                               |

| 10:35 | 招待講演(1)/ Invited Talks(1)                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | "Digitally-Assisted Analog Testing for Mixed-Signal SoC," <i>Professor Kwang-Ting Cheng (University of California, Santa Barbara / University of Tokyo)</i> "A Theoretical Approach to the Research on ATPG and DFT," <i>Professor Hideo Fujiwara (Nara Institute of Science and Technology)</i>                                                                                                                              |

| 11:55 | 昼食 / Lunch                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14:00 | 招待講演(2)/ Invited Talks(2)                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | "Synergy between Manufacturing Test, Silicon Validation / Debug and Fault Tolerance," Mr. Rajesh Galivanche (Intel Corporation)  "Gradual and Steady Change on Logic Testing," Dr. Yasuo Sato (Hitachi, Ltd.)  "Test Pattern Generation using Boolean Proof Engines," Professor Rolf Drechsler (Bremen University)  "Toward Unification of Testing and Verification of VLSI," Professor Masahiro Fujita (University of Tokyo) |

| 16:10 | 休憩 / Coffee Break                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16:40 | 招待講演(3)/ Invited Talks(3)                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | "Automated Debugging from Design to Silicon: Advances, Perspectives and Solutions," <i>Professor Andreas Veneris</i> ( <i>University of Toronto</i> ) "Correctness of Unreliable Systems? A Basis for Formal Robustness Checking," <i>Professor Goerschwin Fey</i> ( <i>University of Tokyo, Bremen University</i> ) "VLSI Design and Test Education in VDEC," <i>Professor Satoshi Komatsu (University of Tokyo)</i>         |

| 18:10 | 閉会の挨拶                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18:15 | 懇親会 / Banquet                                                                                                                                                                                                                                                                                                                                                                                                                 |

# Digitally-Assisted Analog Testing for Mixed-Signal SoC

# K.-T. Tim Cheng

Univ. of California, Santa Barbara

### Abstract:

We present a methodology called digitally-assisted analog testing designed for characterizing, silicon-debugging and testing digitally-enhanced analog circuitry in mixed-signal systems-on-a-chip (SoCs). This methodology can be applied to various devices such as modern A/D converters, adaptive equalizers in high-speed serial links, and RF transceivers that have built-in digital circuitry for improving performance and decreasing power dissipation. By observing the digital data captured, we can thoroughly test the analog circuitry to achieve high fault coverage without directly accessing any analog signal. We demonstrate the effectiveness and the generality of this methodology using several examples including a state-of-the-art pipelined A/D converter, an adaptive equalizer in serial link transceivers, and an image-reject RF receiver.

## Biography:

Tim Cheng received the Ph.D. degree in Electrical Engineering and Computer Science from the University of California, Berkeley in 1988.

He worked at Bell Laboratories in Murray Hill, NJ, from 1988 to 1993 and joined the faculty at the University of California, Santa Barbara in 1993 where he is currently Professor and Chair of the Electrical and Computer Engineering Department. He was the founding director of UCSB's Computer Engineering program. His current research interests include design verification, test, silicon debug, and multimedia computing. He has published over 300 technical papers, co-authored three books and holds ten U.S. Patents in these areas. Cheng serves on the Executive Committee of the MARCO/DARPA Gigascale System Research Center (sponsored by the Semiconductor Industry Association, U.S. semiconductor equipment,

materials, software and services industries, and the U.S. Dept. of Defense) and Co-Director of the International Center of System-on-Chip and International Center on Design for Nanotechnologies (jointly sponsored by National Science Foundation, USA and Chinese National Science Foundation, China) and leading their design, test and verification research efforts.

Cheng, a fellow of IEEE, received Best Paper Awards at the 1994 Design Automation Conference and 1999 Design Automation Conference, 2001 Annual Best Paper Award in Journal of Information Science and Engineering, Best Paper Award in 2003 Conference of Design Automation and Test in Europe (DATE 2003), and the Best Paper award at 1987 AT&T Conference on Electronic Testing. He currently serves as Editor-in-Chief for IEEE Design and Test of Computers, Editor for IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Associate Editor for ACM Transactions on Design Automation of Electronic Systems, Associate Editor for Formal Methods in System Design, Editor for Journal of Electronic Testing: Theory and Applications, and Editor for Foundations and Trends in Electronic Design Automation. He has been General Chairs and Program Chairs for a number of international conferences on design, design automation and test.

# A Theoretical Approach to the Research on ATPG and DFT

# Hideo Fujiwara

Graduate School of Information Science Nara Institute of Science and Technology

### Abstract:

The basis is necessary for development in general. Although the research on testing should be practical, theoretical approach to the research on testing is also important. Theoretical research is dispensable for practical research. The fundamental problems of testing can be categorized into two; practical synthesis problems and theoretical analysis problems. The practical synthesis problems include test generation (ATPG) and design for testability (DFT). The theoretical analysis problems include analysis of test generation complexity and classification of sequential logic circuits. This talk will address the importance of theoretical approach to the research on ATPG and DFT by introducing two cases of theoretical analysis problems; complexity of test generation and classification of sequential circuits.

## Biography:

Prof. Hideo Fujiwara received the B.E., M.E., and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 1969, 1971, and 1974, respectively. He was with Osaka University from 1974 to 1985 and Meiji University from 1985 to 1993, and joined Nara Institute of Science and Technology in 1993. Presently he is a Professor at the Graduate School of Information Science, Nara Institute of Science and Technology, Nara, Japan.

Prof. Fujiwara's research interests include VLSI design and test, VLSI CAD, and fault tolerant computing. He has over 300 publications, and 9 books including the book from the MIT Press entitled "Logic Testing and Design for Testability". He received many awards including Okawa Prize for Publication, IEEE Computer Society Meritorious Service Awards, IEEE Computer Society

Continuing Service Award, and IEEE Computer Society Outstanding Contribution Award.

Dr. Fujiwara is a fellow of the IEEE, a Golden Core member of the IEEE Computer Society, a fellow of the IEICE (the Institute of Electronics, Information and Communication Engineers of Japan) and a fellow of the IPSJ (the Information Processing Society of Japan).

# Mainstream Computing With Mainframe-Class Reliability: Opportunities and Challenges

# Rajesh Galivanche

**Intel Corporation**

### Abstract:

Traditionally, reliability requirements of mission critical applications such as military, space, automotive and mainframe computer systems have driven the design and deployment of fault tolerant solutions. Such systems employed expensive techniques such as duplicate and compare, n-modular redundancy etc., to detect errors and, in some cases, avoid catastrophic system failures. In the future, main stream computing systems employing semiconductor products manufactured in advanced process technologies are likely to face significant reliability challenges with issues related to minimum Vcc, aging, soft errors, process variations etc., and will necessitate the use of fault tolerance features. Some traditional fault tolerant solutions may be unacceptable for mainstream products due to their high cost. This talk will focus on the current industry trend in process technology, reliability challenges facing mainstream products in the future, and the various opportunities to lower the cost of fault tolerant solutions.

## Biography:

Rajesh Galivanche is a Senior Principal Engineer and Manager of Advanced Test Technology development team in the Technology and Manufacturing Group at Intel. His group researches into Advanced Test and CAD methods for manufacturing test, debug and fault diagnosis of semiconductor devices. Rajesh has been with Intel for the last 12 years and before that he worked at Motorola, LSI Logic Corporation, and Sunrise Test Systems.

# **Gradual and Steady Changes on Logic Testing**

## Yasuo Sato

Chief Engineer, Design & Development Operation, Micro Device Division, Hitachi Ltd.

### Abstract:

Current design of SoC includes various cores such as logic, memory, high speed serial interface or analog cores. Test design for those SoCs requires deep understanding of design structure and making test strategy at the early phase of the design. However, the process is not automated well and be done by DFT engineers in an ad-hoc way. Current semiconductor process technologies are suffering from imperfect lithography and increase of variation, which will cause "parametric defects". Conventional deterministic tests based on the stuck-at and the transition delay fault models are not enough to guarantee high quality of the shipped chips any more. Therefore, new parametric and statistical approaches with low test cost are strongly needed. DFT and ATE structures should change to tackle these challenges. The speaker introduces gradual and steady changes of design and process, and addresses the challenges of testing that include the feedback of design structure to test, and the approach of non-deterministic test. He also introduces briefly the current Japanese contribution to the testing world and expects new advances that are based on "Design to Test (D2T)".

## Biography:

Yasuo Sato is a chief engineer of the Micro Device Division, Hitachi Ltd. The Micro Device Division is responsible for developing custom ASICs that target high performance and high reliability for network systems or other high-performance devices. He joined Hitachi in 1978, and began working in computer-aided design that includes logic, layout, mask and test design. He had been the senior manager of Test Methodology Group of Semiconductor Technology Academic Research Center (STARC) from 2003 to 2005. His research includes BIST, delay testing (especially interested in small delay testing) and fault diagnosis. He holds B.S. and M.S. in mathematics from Tokyo University. He received Ph.D. in engineering from Tokyo Metropolitan University in 2005. Yasuo is also a visiting professor of Faculty of Computer Science and Systems Engineering, Kyusyu Institute of Technology, the

co-general chair of Asian Test Symposium 2008 at Sapporo, a member of test working group of Semiconductor Technology Roadmap Committee of Japan (STRJ) and a member of test & ATE working group of International Technology Roadmap for Semiconductors (ITRS).

# Test Pattern Generation using Boolean Proof Engines

## Rolf Drechsler

Institute of Computer Science, University of Bremen

### Abstract:

The postproduction test of integrated circuits is crucial to ensure a high quality of the final product. This test is carried out by checking the correct response of the chip under predefined input stimuli - or test patterns. These patterns are calculated by algorithms for Automatic Test Pattern Generation (ATPG). Due to the rapidly growing size of integrated circuits, there is a need for new algorithms. While classical algorithms reach their limit, there have been recent advances in algorithms to solve Boolean satisfiability (SAT). Because SAT solvers are working on Conjunctive Normal Forms (CNF), the problem has to be transformed.

In this talk, the core techniques of SAT-based ATPG are presented. Methods are shown that apply structural knowledge about the circuit during the transformation. As a result, the size of the problem instances decreases as well as the run time of the ATPG process. The techniques were implemented and experimental results are presented. The approach was combined with the ATPG framework AMSAL of NXP Semiconductors. It is shown that the overall performance of an industrial framework can be significantly improved. The experiments show the benefits regarding efficiency and robustness of the combined approach.

## Biography:

Rolf Drechsler received the Diploma and Dr. Phil. Nat. degrees in computer science from the J.W. Goethe-University, Frankfurt am Main, Germany, in 1992 and 1995, respectively. He was with the Institute of Computer Science at the Albert-Ludwigs-University, Freiburg im Breisgau, Germany, from 1995 to 2000. He joined the Corporate Technology Department of Siemens AG, Munich, in 2000, where he worked as a Senior Engineer in the Formal Verification Group. Since October 2001, he has been with the University of Bremen, Bremen, Germany, where he is now a Full Professor for Computer Architecture. His research interests include verification, testing, logic synthesis, and evolutionary algorithms.

# Toward Unification of Testing and Verification of VLSI

# Masahiro Fujita

VLSI Design and Education Center (VDEC), University of Tokyo

### Abstract:

Functional verification processes and test designs of VLSI have been separated. In other words, test designs start only after logic designs have been finished, i.e., logic circuits have been obtained. Verification and manufacturing test of VLSI are, however, essentially targeting the same goal, the correct behavior of VLSI. In this talk, ways to unify the two are discussed. One way to do so is to introduce testing design processes in very early design stages. Recently system level design methodologies, which deal with both hardware and software aspects of target VLSI, and their associated tools have been researched and developed. Just like the descriptions of test benches for verification purposes, components which perform manufacturing test can be introduced. Those components may be realized as a VLSI tester equipment, a software of the processor in the VLSI, or some external hardware such as FPGA board. On the other hand, when testing manufactured VLSI chips, functional verification processes can also be performed. Such post silicon verification techniques are also discussed.

## Biography:

Masahiro Fujita received his Ph.D. degree in Information Engineering from the University of Tokyo in 1985 and shortly after joined Fujitsu Laboratories Ltd. From 1993 to 2000, he had been assigned to Fujitsu's US research office and directed the CAD research and development group. In March 2000, he joined the department of Electronic Engineering in the University of Tokyo as a professor. He is now a professor at VLSI Design and Education Center (VDEC) in the university. He has co-authored 7 books, and has over 150 publications. He has received several awards from Japanese major scientific societies on his works in formal verification and logic synthesis. His doctor degree thesis was written in early 80's and on model checking. Since then he has been involved in many research projects on various aspects of formal verification. His current research interests include synthesis and verification

in higher level design stages, hardware/software co-designs and also digital/analog co-designs.

# Automating Debugging from Design to Silicon: Needs, Solutions and Perspectives

## **Andreas Veneris**

University of Toronto, Department of Electrical and Computer Engineering

### Abstract:

The design and test of advanced semiconductor chips is an extremely laborious and expensive process. In this cycle, RTL debugging and Silicon debug take as much as 70% of the complete time. Although many steps have been automated, designers, verification and test engineers today must manually debug design errors and functional defects. This is a resource-intensive and time-consuming manual work that may jeopardize the time-to-market and it adds significant non-recurring costs.

In this talk, we review the intricate details of the debugging problem and we emphasize the urgent need for automation during RTL and silicon debug. Next, we present past methodologies for automated debug using simulation and BDD based techniques. The main focus of the talk will be on Boolean satisfiability as we present the first SAT-based algorithm to automate this process. Later, we will generalize the method using Quantified Boolean Formula (QBF) satisfiability to tackle the intractable nature of the problem. We conclude with a set of studies for the above methodologies on a wide variety of benchmark and industrial designs. These results suggest that satisfiability captures significant characteristics of the problem of debugging. They also encourage novel research in satisfiability-based debugging approaches as a complementary process to this of design verification and silicon test.

## Biography:

Andreas Veneris received the Diploma in Computer Engineering and Informatics from the University of Patras in 1991, the M.S. degree in Computer Science from the University of Southern California, Los Angeles in 1992 and the Ph.D. degree in Computer Science from the University of Illinois at Urbana-Champaign in 1998. He currently is an Associate Professor cross-appointed with the Department of Electrical and Computer Engineering and the Department of Computer Science at the University of Toronto. His research interests include algorithms and CAD tools for debug, verification and test of digital systems and circuits. He is co-recipient of a best paper award in ASP-DAC'01, co-author of a book and member of IEEE, ACM, AAAS, Technical Chamber of Greece and The Planetary Society.

# Correctness of Unreliable Systems? A Basis for Formal Robustness Checking

# Görschwin Fey

VDEC & University of Bremen, Bremen, Germany

### Abstract:

The steady increase of the number of components in integrated circuits (ICs) is achieved by continuously shrinking the feature sizes. This trend is believed to continue within the next years. As a result ICs become more sensitive to transient faults or aging effects. During IC design robustness against these types of failures can be implemented e.g. by using redundancy or gate hardening techniques. As a result the design continues to function correctly in the presence of failing components. But this is a manual and therefore error prone task. Formal methods are commonly applied to proof correctness of systems and design transformations. The talk considers the application of formal methods to ensure and quantify the robustness of a design. After a brief motivation, a formal basis to measure robustness of a given circuit is presented. First algorithmic approaches to evaluate the measure are proposed and experimental results are discussed.

### Biography:

Görschwin Fey received his Diploma in Computer Science from the Martin-Luther University, Halle-Wittenberg, Germany in 2001. Since then he has been with the research group of computer architecture at the University of Bremen, where he received the Dr.-Ing. degree in 2006. He continued his research in Bremen on a permanent position as a post-doctoral researcher. Since December 2007 he is also with the VLSI Design and Education Center at the University of Tokyo where serves as a visiting professor. His research interests are in testing and formal verification of circuits and systems.

# VLSI Design and Test Education in VDEC

# Satoshi Komatsu

VLSI Design and Education Center (VDEC), University of Tokyo

### **Abstract:**

As the complexity of hardware functionality continues to increase, a test of VLSI chips becomes much more important. To meet this trend, education on the test of VLSI chip with System-on-Chip (SOC) test system is essential even in EE department. In VLSI Design and Education Center (VDEC), the University of Tokyo, several courses complementally cover whole of VLSI design and fabrication. In particular, education with physical practice is important and emphasized so that the students are educated for skillful engineer with practical experience of VLSI design, fabrication, and measurement. In this talk, a new trial on VLSI test course for graduate / undergraduate students as well as brief introduction of VDEC and D2T Research Division which was established in October 2007 will be presented.

## Biography:

Satoshi Komatsu received the B. S., M.S, and Ph. D. in Electronic Engineering from the University of Tokyo, Tokyo, Japan, in 1996, 1998 and 2001, respectively. He has been a member of VLSI Design and Education Center (VDEC) in University of Tokyo since 2001. He is now a Visiting Associate Professor in VDEC, the University of Tokyo. His current research interests are low-power / high-speed data transmission methods on VLSI and system level VLSI design methodologies. He is a member of Institute of Electrical and Electronics Engineers (IEEE), Institute of Electronics, Information and Communication Engineers, and Information Processing Society of Japan (IPSJ).

15

# 第 1 章 VDEC 事業の紹介と平成 19 年度事業報告

# 1.1 VDEC事業の紹介と平成 19 年度事業報告

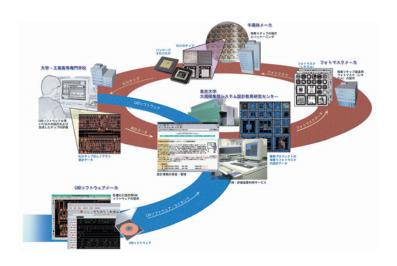

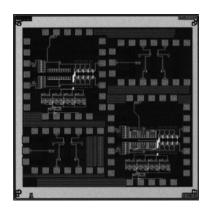

東京大学大規模集積システム設計教育研究センター (VDEC) は発足後11年が過ぎた. 平成19年度も『LSI 教育情報の発信拠点形成』,『VLSI 設計支援教育用 CAD ソフトウェアの整備』,『VLSIチップ試作支援』を3つの柱として,円滑な運営を目指した事業を展開した. 図1.1に示す VDEC の活動内容に基づき,以下に平成19年度の概要を報告する.

VDEC の使命は全国の国公私立大学および高専の LSI 設計研究・教育を高度化し、産業界に対しても優秀な LSI 設計技術者を数多く送り出すことである. しかし, VDEC 発足当初、我が国の大学には CAD ソフトウェア 利用技術教育や実用的 LSI 設計フロー教育のカリキュ ラムはほとんど存在していなかったため VDEC にとっ てはこれらの整備が急務の課題であった. CAD ソフト ウェアの利用技術に関しては CAD ベンダーが独自の設 計技術を有しており、これを導入することとした. 大学 院学生、若手教官を対象として CAD ベンダーから講師 を招き、それぞれの CAD ソフトウェア毎に年2回のセ ミナーを開催することとし、CAD ベンダーと契約を結 んだ. これまで年2回の内1回はVDECで. 残り一回 は地方拠点校で実施している.参加定員は設備の関係で それぞれ 20~50 名程度であり必ずしも十分とはいえな いが、VDEC としては各ユーザ研究室内で"技術伝承" され、VDEC 主催のセミナーがトリガーとなって CAD 利用技術が全国的に広がることを期待している(1.3章 参照).

LSI 設計フローセミナーは LSI 設計の基本概念教育と

複数の CAD ツールを連携する実用的設計例の体験教育である。この目的で VDEC では社会人のリフレッシュ教育プログラムと兼ねて LSI 設計教育セミナーを年1回(12月~1月)開催している。このコースは"ディジタル設計コース","アナログ設計コース","RF設計コース","最先端設計事例コース"の4コースからなっている。前3者は演習を伴う体験教育コースであり,主要大学の経験豊かな教官を講師に招いて実施している。最先端設計事例コースは講義主体のコースであるが,大学および企業から第一線の講師を招き,設計経験をもとにした講演を行っている。

これらセミナーに加えて VDEC では年1回, 若手教官と学生を中心とした VDEC デザイナー・フォーラムを開催している. これはワークショップ形式の会合であり,企業・大学からの招待講演に交えて,参加者が設計事例を持ち寄ってその成功談,失敗談を交換する. これから設計を始めたいと考えている学生・教官もここでさまざまなノウハウを得ることができる.

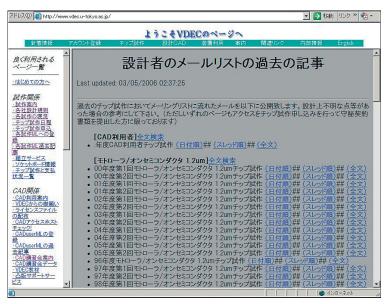

このようなセミナー、フォーラムを通じた教育システムにより LSI 設計の基本的項目を学習できるようになっているが、それでも実際の LSI 設計の場面では、さまざまな困難に直面することが多い、初心者にとっては CAD ソフトウェアのセットアップは最大の問題である、セットアップの後も CAD ソフトウェアが発する "難解なエラーメッセージ"でとまどうことも多い、このような場合に力を発揮するものが VDEC メールグループである、VDEC ユーザは VDEC のホームページから CAD

図 1.1 VDEC の活動内容

メールグループや試作技術対応のユーザグループに登録 することができ、そこに直面する疑問点を投稿し、助け を求めることができる. メールグループの登録ユーザは それに回答する義務を負っているわけではないが、ほと んどの場合. 数時間から数日以内に経験豊かなユーザか らの支援を得ることができる. また、今まで蓄積されて きたメールグループの情報が VDECの WEB 上で認証 された VDEC ユーザへ公開され、教育上の資産として 残していく仕組みになっている. (図1.2).

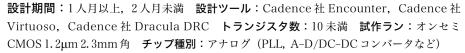

VLSI チップ試作支援に関しては、従来のオンセミ 1.2 μm CMOS, NEC 0.8μm Bipolar, 90nm CMOS 試作 (ASPLA/STARC) およびローム 0.18 μm CMOS 試作 を実施した. さらに、VDECでは現在のサービス項目 に載っていない BiCMOS, SiGe 等について、アメリカの MOSIS との連携で、アカデミック価格で試作を行って

いる.

また、一流のLSI 設計者を目指す学生に対してイン センティブを与える仕組みとして LSI IP アワードを実 施している. 本アワードは半導体各社と日経 BP 社の支 援でスタートした IP 開発支援のしくみである。平成 19 年度は従来に加え、東芝 MeP 賞が新設され、MeP コア を利用した設計事例に対する表彰が予定されている.(図 1. 3).

10月にはアドバンテスト社から寄付部門「Design To Test (D2T)」が設置され、平成 20 年 1 月 24 日にはオー プニング記念式典を開催した. この寄付部門では, LSI のテストに関する教育の充実とともに、 設計とテストの 架け橋を目指した研究が進められることになっている. これまでの活動を振り返ると、VDEC 発足以来 10 年余 の活動の中で LSI 設計文化が根付いた研究室や大学では

図 1.2 VDEC メーリングリスト検索システム

第8回受當論文 第8回表彰式・懇親会 風景

第7回受賞論文 第7回表彰式·懇親会 風景 第6回受賞論文 第6回表彰式·懇親会

風景 第5回受賞論文 第5回表彰式・懇親会 風景

第4回受賞論文 第4回表彰式·懇親会 風景

第3回受賞論文 風景

第2回受賞論文 第1回受賞論文

### 第8回LSI IPデザイン・アワード表彰式 産学連携の応募や魅力的テーマが増加

LSI IPデザイン・アワードの表彰式が、2006年5月18 日(木)品川で「SoC/SiPディベロッパーズ・コンファ レンス2006」(主催日経マイクロデバイス)の併設イ ベントとして盛大に開催された。今回の特徴は、大 学の独立行政法人化に伴い、産学連携の応募が増 えたこと、評価トップの論文に賞推薦が集中したこと である。企業部門のIP優秀賞はベンチャー企業と大 学がデファクト標準を狙って開発した次世代車載 LAN(Flex-Ray)向けOSとミドルウェアで、テーマ、開 発時期、質という点で高い評価を受けた。大学部門 でも企業との連携によって実現した1Tbps/3Wの3次 元積層チップ間無線インタフェースがIP優秀賞を受 賞した。いずれも企業にとって魅力的なIPである。表 彰式には、運営委員長の田中昭二氏(紹雷道工学 研究所所長)をはじめ、多数の方が参加された。

- 2006年第8回IPアワード受賞論文公開中

- 2006年第8回IPアワード表彰式・懇親会風景

### 第10回募集要項&東芝MeP賞募集要項

第3回表彰式・懇親会 第10回LSI IPデザイン・アワード募集 IPアワードについて

この賞は、システムLSIに使う、独創的 1)大学部門 • 第10回LSI IPデザイン・アワード応募要で優れたIP(回路やソフトウェアなどの 項(大学) 設計資産)の開発を支援し、半導体産

図 1.3 LSI IP 賞

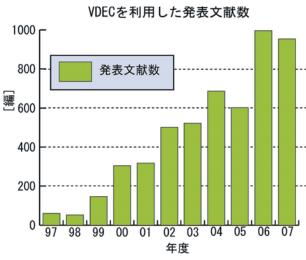

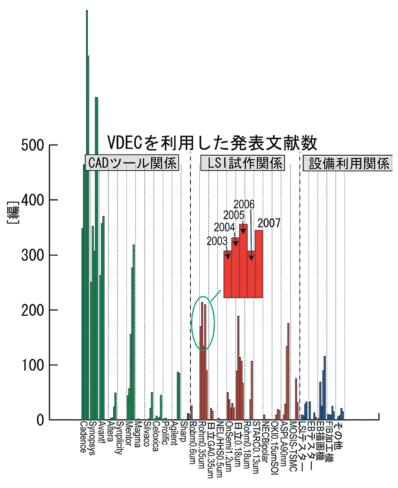

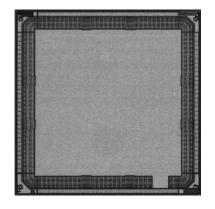

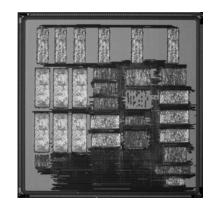

すでに活発な設計研究・教育がスタートしている.図1.4 に VDEC を利用した研究成果の指標として、VDEC に 関係する発表文件数の推移を示す.単純に比較はできないが発表文献の数は増加傾向にあり、VDEC 発足以来、集積回路に関係する研究が活性化されていることが確認できる.

図 1.4 VDEC を利用した発表文献数の推移

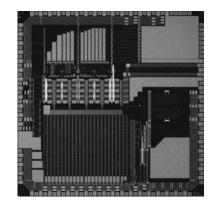

図 1.5に VDEC に関係する発表文献の VDEC ファシリティー利用状況を示す. 論文執筆にあたり CAD ソフトウェアが幅広く利用されていることが確認できる. CAD ソフトウェアはチップ設計だけでなくチップ試作の準備段階で利用される場合が多いため, 研究の基本アイデアを実証するツールとしての貢献度も大きい.また,研究論文には最先端のプロセステクノロジが好んで利用される傾向にあり世界的には 65nm CMOS から 45nm CMOS による設計事例報告が増加しており, VDEC においても最先端プロセステクノロジメニューの充実をはかっていきたい. そのほかのファシリティーとして, LSI テスターや FIB 加工装置, EB 描画装置などが研究目的に幅広く利用されることを期待する.

図 1.5 VDEC ファシリティー利用状況

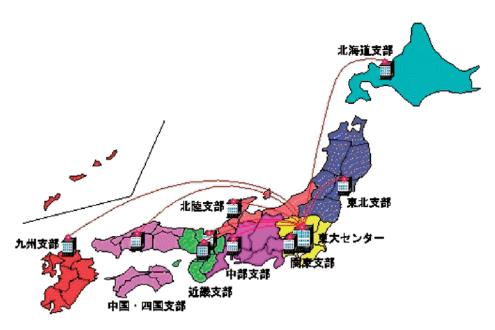

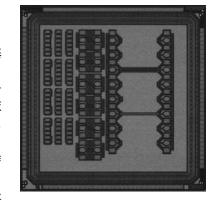

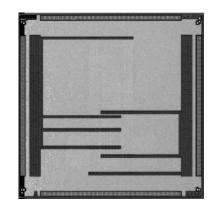

# 1.2 CAD ソフトウェアの整備

平成8年度から整備を行っているCADソフトウエアは、平成19年度は表1.1に示すツール群を全国の大学に提供している。CADソフトウエアの利用は、図1.2に示す全国地域拠点校10箇所にライセンスサーバを設置し、全国各大学の利用者が手許の計算機にインストールしたCADソフトウエアを、最寄のライセンスサーバにおいて認証を行うことで、ネットワークを利用した運用形態となっている。ライセンス数はCADの項目ごとに100から1000程度のフローティングライセンスとなっ

ており、全国の国・公・私立大学・高専において教育・研究目的に限り利用できるようになっている.

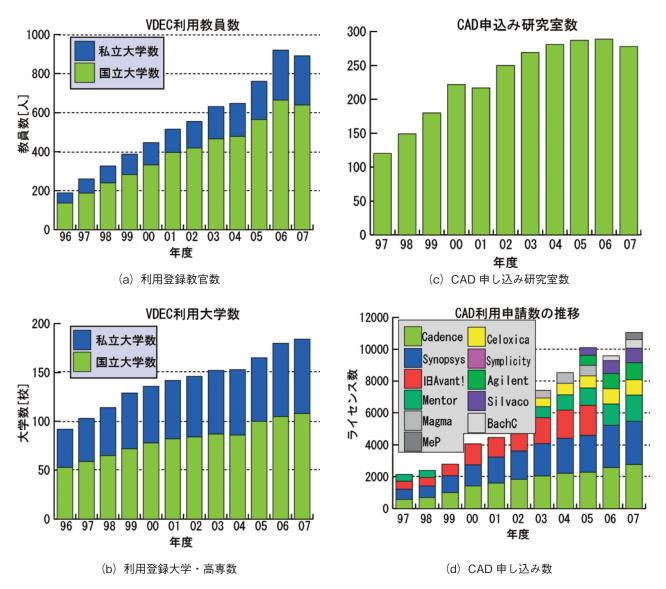

VDEC の CAD の利用、および「1.3 章」のチップ 試作の利用のためには、あらかじめユーザ登録が必要と なっているが、これまで VDEC に利用登録をしている (a) 全国教官数および (b) その所属する大学数および (c) CAD の利用申請があった研究室(教官)数の推移は図 1.7 の通りである.

# 表 1.1 導入された CAD システム

| 名称               | 用途                                                                                                                        | メーカ                          |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| Cadence 社設計システム  | VerilogHDL/VHDL ベースの入力,シミュレーション,論理合成,テスト生成,マクロセルを含むセルベースの配置配線とバックアノテーション,会話型の回路図およびマスクレイアウト入力,アナログ機能・回路シミュレーション,設計検証,回路抽出 | Cadence Design Systems, Inc. |  |

| Synopsys 社設計システム | VerilogHDL/VHDL シミュレーション,論理合成,<br>テスト生成.マクロセルを含むセルベースの配置<br>配線設計とバックアノテーション,回路シミュレー<br>ション,デバイスシミュレーション                   | Synopsys, Inc.               |  |

| レイアウト検証システム      | レイアウトのデザインルールチェック及び検証                                                                                                     | Mentor Graphics Co. Ltd.     |  |

| Silvaco社設計ツール    | 高速回路シミュレーション,                                                                                                             | Silvaco                      |  |

| 高周波回路設計検証システム    | 通信機器や関連デバイスなどの高周波回路/システムの設計,検証                                                                                            | Agilent Technologies         |  |

| C言語ベース設計システム     | Handel-Cでシステム設計,合成,検証                                                                                                     | Celoxica/Agility             |  |

| C言語ベース設計システム     | BachC 設計ツール                                                                                                               | Sharp                        |  |

図 1.6 全国地域拠点校

図 1.7 ユーザ登録数および CAD 申込数の推移

# 1. 3 平成 19 年度 VDEC 事業報告

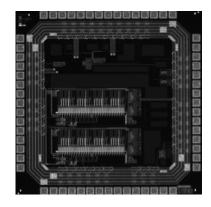

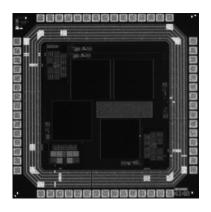

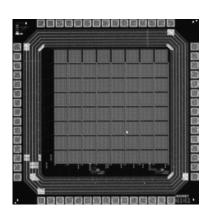

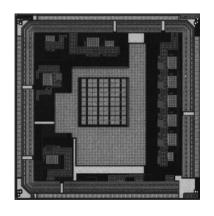

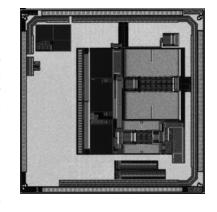

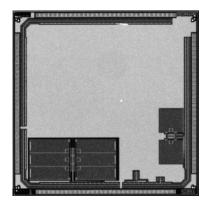

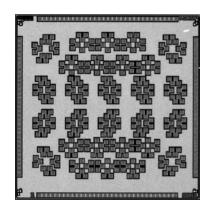

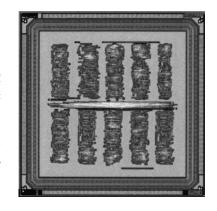

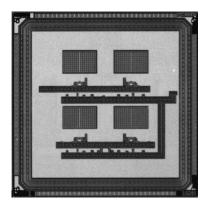

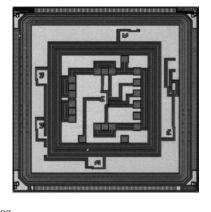

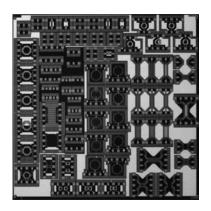

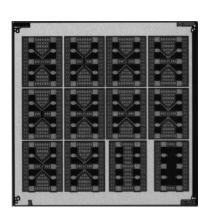

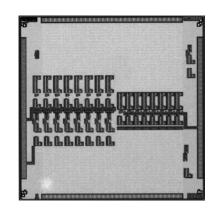

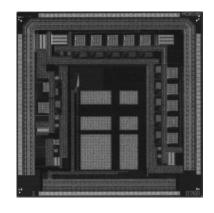

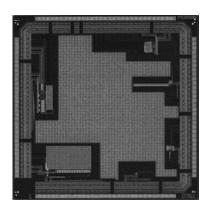

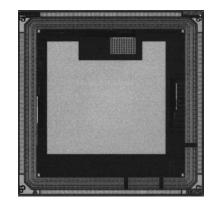

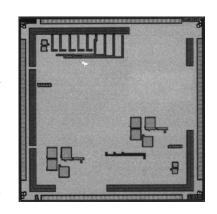

## 1.3.1 VLSIチップ試作

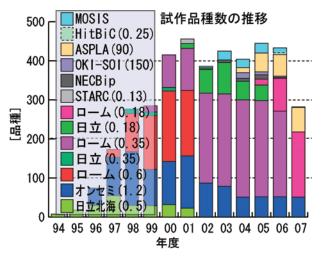

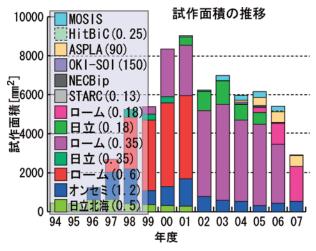

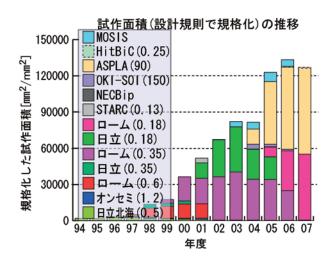

図1.3.1は、VDEC および、それに先行して行われたパイロットプロジェクトでのチップ試作数の推移を示したものである.

VLSIチップ試作は、平成6,7年度(1994,1995年 度)のパイロットプロジェクトでは、ファウンドリは NEL 社の CMOS 0.5 μm (当該プロセスはその後日立北 海セミコンダクタ社に継続) 1社であったが、平成8年 度(1996年度)の VDEC 発足後、日本モトローラ社の CMOS 1.2 μm (平成 11 年度からは、オン・セミコンダ クターにて継続)が協力を開始し、平成9年度からはロー ム社の CMOS 0.6 μm が加わった. さらに平成 10 年度 には日立製作所の CMOS 0.35 μm, 平成 11 年度にはロー ム社  $0.35 \mu \text{m}$  がそれぞれ加わった. また, IP 開発プロジェ クトの一環として STARC 0.13 μm の試作を行った. 平 成13年度から、日立製作所のCMOS 0.18 μm のサービ スを実施している。平成14年度は、広島大学岩田先生 の主導の下に、VDEC と MOSIS の協力による試作サー ビスを試行的に実施した. これは、TSMC、IBM といっ た海外のファブを MOSIS を経由することで格安で提供 するものである. さらに,東京大学柴田先生主導の元に, NEC 化合物デバイス株式会社によるバイポーラ LSI の 試作サービスも行った. 平成16年からテスト試作とし て沖電気 CMOS SOI 0.15 μm プロセスおよび ASPLA 90nm (現在はSTARCにおいて継続) プロセスの試作 を開始し、90nm 試作については平成17年度より通常 の試作として公募の形で運用を行っている. さらに平成 18年度からはローム社 0.18 µm の試作を開始し、日立 製作所 0.25 μm SiGeBiCMOS のテスト試作を実施した.

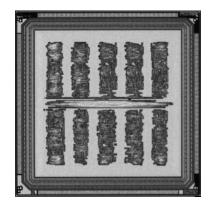

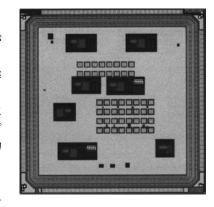

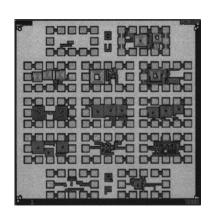

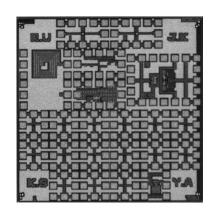

図 1. 3. 1 (a) は設計されたチップ品種数を示す. 図中の棒グラフは, 試作品種数の順調な増加を表しており、 VLSI 試作研究・教育に直接的に係わった学生数を表しているものと考えられることから, 研究・教育効果が劇的に向上していることが想像される. 試作されたチップの品種数は, 02 年度に減少しているが, これは ROHM社の 0.6umプロセスを終了したことによる現象が考えられる. またそれ以降ほぼ 400 品種程度で推移しているが, その中でより微細なプロセスへ試作の中心が推移していることが読み取れる. また昨年度で  $0.35~\mu$  m が修了し,  $0.18~\mu$  m への移行が完全に出来ていないことから, 試作数が 100 品種程度減少する結果となっている.

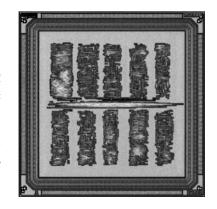

図1.3.1 (b) に設計されたチップ面積を示す. 試作プロセスが微細化すると, 集積度が向上することで, 見かけ上試作面積が減少するように見える場合がある. そ

こで、図1.3.1 (c) に試作面積をそれぞれの試作プロセスにおける特性寸法で規格化した、規格化試作面積の傾向も併せて示す。

(a) 設計チップ品種数

(b) 設計チップ面積

(c) 規格化した設計チップ面積

図1.3.1 チップ試作数・面積推移

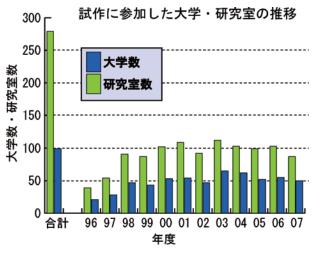

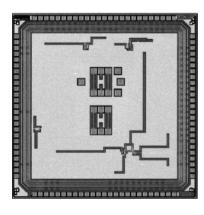

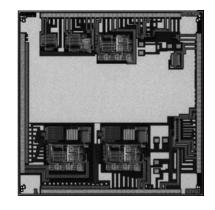

また、図1.3.2にこれまでに試作に参加した教員数、大学数の推移およびその累計を示す。また、チップ試作に必要な設計規則などの、試作会社固有の機密情報にアクセスするための「機密保持契約」締結教員数は、オンセミコンダクタが153名、ロームの0.18umプロセスが132名、ASPLA/STARC 90nmが55名となっている。なお、ローム0.35umプロセスに対する守秘契約締結教員数は207名であった。

## 1.3.2 平成 19 年度チップ試作概況

平成18年度は、表1.3.1に示す日程でチップ試作を行った.チップ試作の参加者・試作の内容は、第2章のチップ試作報告を参照されたい.

図 1.3.2 VDEC チップ試作参加教員数・大学数の推移とその累計

### 表 1.3.1 平成 19 年度チップ試作日程

## ●CMOS 1.2um(オンセミコンダクタ:旧 日本モトローラ)

|             | 試作申込開始     | 試作申込締切     | 設計締切       | 納品・試作完了         |

|-------------|------------|------------|------------|-----------------|

| 平成18年度第2回   | 2006/10/ 2 | 2006/ 1/ 9 | 2007/ 4/ 2 | 2007/ 7/17      |

| 平成19年度第 1 回 | 2007/ 4/ 2 | 2007/ 7/ 2 | 2007/10/ 1 | 2008/ 1/ 8      |

| 平成19年度第2回   | 2007/10/ 1 | 2008/ 1/ 7 | 2008/ 3/31 | 2008/ 7/14 (予定) |

### ● CMOS 0.35um (ローム)

|             | 試作申込開始     | 試作申込締切     | 設計締切       | 納品・試作完了         |

|-------------|------------|------------|------------|-----------------|

| 平成18年度第3回   | 2006/ 8/28 | 2006/11/27 | 2007/ 2/26 | 2007/ 7/17      |

| 平成19年度第 1 回 | 2005/11/ 5 | 2007/ 2/13 | 2007/ 5/14 | 2007/ 9/ 7      |

| 平成19年度第2回   | 2007/ 1/ 9 | 2007/ 5/ 7 | 2007/ 6/18 | 2007/ 9/ 7      |

| 平成19年度第3回   | 2007/ 2/ 5 | 2007/ 6/11 | 2007/ 7/17 | 2007/11/20      |

| 平成19年度第4回   | 2007/ 3/12 | 2007/ 7/10 | 2007/ 8/20 | 2007/12/19      |

| 平成19年度第5回   | 2007/ 4/ 9 | 2007/ 8/13 | 2007/ 9/18 | 2008/ 1/23      |

| 平成19年度第6回   | 2007/ 5/ 7 | 2007/ 9/10 | 2007/10/15 | 2008/ 2/29      |

| 平成19年度第7回   | 2007/ 6/11 | 2007/10/ 9 | 2007/11/19 | 2008/ 2/29      |

| 平成19年度第8回   | 2007/ 7/10 | 2007/11/12 | 2007/12/10 | 2008/4/21(予定)   |

| 平成19年度第9回   | 2007/ 8/13 | 2007/12/ 3 | 2008/ 1/15 | 2008/ 5/26 (予定) |

| 平成19年度第10回  | 2007/ 9/10 | 2008/ 1/ 7 | 2008/ 2/29 | 2008/6/30(予定)   |

### Bipolar (NEC)

|     | 申込開始 | 申込乄切 | 設計乄切       | チップ納品      |

|-----|------|------|------------|------------|

| 第1回 |      |      | 2007/ 9/29 | 2008/ 2/26 |

## ● CMOS 90nm (STARC)

|            | 試作申込開始 | 試作申込締切     | 設計締切       | 納品・試作完了    |

|------------|--------|------------|------------|------------|

| 平成19年度第1回  |        | 2006/12/18 | 2007/ 4/23 | 2007/ 8/16 |

| 平成 19年度第2回 |        | 2007/ 3/19 | 2007/ 7/20 | 2007/10/19 |

| 平成 19年度第3回 |        | 2007/ 7/18 | 2007/10/22 | 2008/ 1/31 |

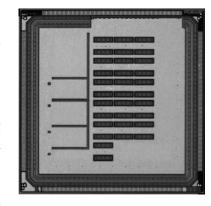

# 1.3.3 ライブラリ整備状況

VDECにおけるチップ試作(主にディジタル LSI 試作) では、設計ライブラリの整備が重要である. VDEC では、 VDEC 提供 CAD ソフトウエア中のライブラリ生成ツー

ルを利用して、平成8年度から順次ライブラリ整備事業 を行ってきている. 現状では、VDEC における各プロ セスの試作において、利用可能なライブラリは表1.3.2 に示すとおりとなっている.

| プロセス                      | 名称             | 作成者                                                             | 内容                                                                                                                     | 状況                             |  |  |

|---------------------------|----------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| HHS (NEL) $0.5 \mu$ m     | P2lib          | 京都大学小野寺研究室                                                      | ・Synopsys 用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・CellEnsamble用配置配線ライブラリ                                            | 試作チップの動<br>作検証完了               |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | ac.jp/DesignLib/P2lib/NEL05/index.html                                                                                 |                                |  |  |

|                           | EXDlib         | 九州大学安浦研究室                                                       | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・VHDL用シミュレーションライブラリ<br>・Apollo用配置配線ライブラリ<br>・CellEnsamble用配置配線ライブラリ | 試作チップの動<br>作検証完了               |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | ac.jp/DesignLib/Kyushu/NEL05/index.html                                                                                |                                |  |  |

| MOT (On Semi) $1.2 \mu$ m | P2lib          | 京都大学 小野寺研究室                                                     | ・Synopsys 用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・CellEnsamble 用配置配線ライブラリ                                           | 試作チップの動作検証完了                   |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | ac.jp/CHIP/DesignRule/MOT15/rule.html                                                                                  |                                |  |  |

|                           | EXDlib         | 東京大学VDEC                                                        | ・Synopsys 用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・Apollo 用配置配線ライブラリ                                                 |                                |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | ac.jp/CHIP/DesignRule/MOT15/rule.html                                                                                  |                                |  |  |

| 日立0.35 μ m                | EXDlib         | 東京大学VDEC                                                        |                                                                                                                        |                                |  |  |

|                           |                | http://www.vdec.u-tokyo.ac.jp/CHIP/DesignRule/HIT035/rule.html  |                                                                                                                        |                                |  |  |

|                           | 日立ゲート<br>アレイ   | 日立提供                                                            |                                                                                                                        | 日立から提供の<br>セルを ApolloGA<br>に移植 |  |  |

|                           |                | http://www.vdec.u-tokyo.ac.jp/CHIP/DesignRule/HIT35/rule.html   |                                                                                                                        |                                |  |  |

| ROHM0.35 μ m              | EXDlib         | 東京大学VDEC                                                        | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・Apollo用配置配線ライブラリ                                                   |                                |  |  |

|                           |                | http://www.vdec.u-tokyo.ac.jp/CHIP/DesignRule/ROHM035/rule.html |                                                                                                                        |                                |  |  |

|                           | 京大lib          | 京都大学 小野寺研究室                                                     |                                                                                                                        |                                |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | ac.jp/CHIP/DesignRule/ROHM035/rule.html                                                                                |                                |  |  |

|                           | パスポート<br>ライブラリ | ローム提供                                                           | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・Apollo用配置配線ライブラリ                                                   |                                |  |  |

|                           |                | CDROMにて配布                                                       |                                                                                                                        |                                |  |  |

| 日立0.18 $\mu$ m            | 京大lib          | 京都大学 小野寺研究室                                                     | ・Synopsys 用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・ApolloII用配置配線ライブラリ                                                |                                |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | http://www.vdec.u-tokyo.ac.jp/CHIP/DesignRule/HIT18/rule.html                                                          |                                |  |  |

|                           | EXDlib         | 東京大学VDEC                                                        | ・Synopsys 用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・Apollo 用配置配線ライブラリ                                                 |                                |  |  |

|                           |                | http://www.vdec.u-tokyo.                                        | ac.jp/CHIP/DesignRule/HIT18/rule.html                                                                                  |                                |  |  |

| ローム0.18 μ m               | ローム提供<br>ライブラリ | ローム提供<br>スタンダードセル, IOセ<br>ル, RAM (セルはすべて<br>ブラックボックス)           | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・配置配線用 LEF/DEF ファイル                                                 |                                |  |  |

|                           |                | CDROMにて配布                                                       |                                                                                                                        |                                |  |  |

# 1. 4 セミナー

LSI 設計技術の向上にはセミナーは欠くことができない存在である。平成19年度には、CAD 利用のための技術セミナー、社会人のためのリフレッシュセミナー、若手教官・学生のためのデザイナーズフォーラム等のセミナー、フォーラムを企画、実施した。

# 【CAD 利用のための技術セミナー】

CAD 利用のための技術セミナーでは、VDEC で使用可能な Cadence、Synopsys、Agilent など CAD ベンダーのそれぞれの CAD ツールの操作方法等を各ツールベンダーから講師を派遣していただき講習を行っている。また、VDEC 環境での設計フローに関する講習も VDEC スタッフで実施している。平成 19 年度は、8

月と9月に初心者を対象とした第1回のCAD 利用のための技術セミナーを東京大学 VDEC で実施した.この技術セミナーでは、Cadence のツールを3種・5日間、Synopsys ツールを3種・3日間、Agilent のツールを1種・2日間、東芝ツールを1種・3日間、ASIP Solutionのツールを1種・2日間に加え、VDEC 環境での設計フローに関する講習会を2日間行った。各コースに40名までの教官・学生の受講があり、各ツールの使用方法やVDEC ライブラリを用いた VLSI 設計フローを修得している。また3月には上級者を対象とした CAD 技術セミナーとして Cadence 3種・6日間、Synopsys 2種・3日間、Agilent 2種・3日間、VDEC 環境での設計フローを2日間行った(表 1.4.1)

表 1. 4. 1 平成 19 年度 CAD 技術セミナー開催状況

| 講習項目                               | 開催地   | 開催時期             | 参加人数 | 講習内容                                                          |

|------------------------------------|-------|------------------|------|---------------------------------------------------------------|

| Synopsys Chip Synthesis<br>講習会     | 東京大学  | 2007年<br>8/8     | 33   | 論理合成ツールによる, 合成条件, 結果の解析, 階層設計を行う場合のストラテジなどを学習                 |

| Synopsys Star-RCXT講習会              | 東京大学  | 2007年<br>8/7     | 34   | 配線 RC 抽出の概念の学習とツールの使用方法を学習                                    |

| Synopsys NanoSim講習会                | 東京大学  | 2007年<br>8/8     | 32   | トランジスタレベルの解析ツールNanoSimの使用方法,パワー解析、タイミング解析等についての学習             |

| Cadence SoC Encounter<br>講習会       | 東京大学  | 2007年<br>8/20-21 | 23   | 自動配置配線ツール SoC Encounteのデザインフローと各フェーズでの機能の習得                   |

| Cadence Artist/Composer<br>講習会     | 東京大学  | 2007年<br>8/22    | 41   | 手書き回路設計および、そのシミュレーション制御<br>方法の習得                              |

| Cadence Virtuoso 講習会               | 東京大学  | 2007年<br>8/23-24 | 45   | Layout Editorの使用方法,Pcell(Parameterized<br>Cell)の概念と作成方法の学習    |

| Agilent RFDE 講習会                   | 名古屋大学 | 2007年<br>9/3-4   | 13   | RF/mixed signal IC 設計プラットフォーム RF<br>Design Environment の操作を学習 |

| VDEC 環境におけるトラン<br>ジスタレベル設計方法講習会    | 東京大学  | 2007年<br>9/5-6   | 46   | VDEC 環境で回路設計を進めるための一連のフローを学習する.                               |

| 東芝MeP 講習会                          | 東京大学  | 2007年<br>8/19-21 | 5    | MeP のプロセッサアーキテクチャ、機能拡張について学習する.                               |

| ASIP Solution, ASIP<br>Meister 講習会 | 東京大学  | 2007年<br>9/25-26 | 7    | 特定用途向き命令セットプロセッサ開発環境 ASIP<br>Meister について学習する.                |

| Synopsys, Astro講習会                 | 東京大学  | 2008年<br>2/25-26 | 18   | 自動配置配線コアツール Astroのデザインフローと<br>各フェーズでの機能の習得                    |

| Cadence SoC Encounter<br>講習会       | 東京大学  | 2008年<br>2/27-28 | 14   | 自動配置配線ツール SoC Encounterのデザインフローと各フェーズでの機能の習得                  |

| Cadence Verilog-A講習会               | 東京大学  | 2008年<br>3/4-5   | 13   | Verilog-A による回路記述方法, Artist, 若しくはコマンドラインからのシミュレーションの実行方法の学習.  |

| Agilent GoldenGate講習会              | 東京大学  | 2008年<br>3/11-12 | 10   | GoldenGate の基本的な使用法と,能動回路の設計<br>に必要な知識の学習.                    |

| Agilent Momentum講習会                | 東京大学  | 2008年<br>3/13    | 9    | Momentumの基本的な使用法と、GoldenGateと統合されたモーメンタムの基本操作の実習              |

| Synopsys HSPICE                    | 東京大学  | 2008年<br>3/14    | 22   | 回路シミュレータの基本である SPICE シミュレーションの基礎を学習する.                        |

| VDEC 環境におけるトラン<br>ジスタレベル設計方法講習会    | 東京大学  | 2008年<br>9/24-25 | 15   | VDEC 環境で回路設計を進めるための一連のフローを学習する.                               |

| Cadence Skill 講習会                  | 東京大学  | 2008年<br>3/26-27 | 11   | Cadence SKILL 記述言語の入門コース                                      |

これら CAD 技術セミナーへの参加要望は非常に大きく、地方からの参加者も多い。これは CAD 技術セミナーに対する需要が依然として大きなことを表しており、VDEC はこの状況に対応し、大規模な CAD 技術セミナー開催の仕組みの整備を行ってきた。また、これまで春には各地方拠点(北大・東北大・金沢大・東工大・名大・京大・阪大・広大・九大)で開催していたが、全国ユーザの満足度の和が最大になるのではないかと、今年は試験的に春のセミナーも東大で実施した。

平成19年度12月~1月には平成18年度に引き続き、集積回路産業に携わる職業人を対象にリフレッシュ教育としてVLSI設計に関する最新かつ高度の知識・技術の習得を目的として、社会人向けの「VLSI設計リフレッシュセミナー」を拠点大学教官および企業の第一線の設計者を講師に招き開催した(表1.4.2).

このセミナーは主に社会人を対象として、演習を伴う 最新の VLSI 設計技術の実践的教育を行うもので、平成 10 年度に文部省専門教育課の支援のもとでスタートし たが、今年度は(財)電気電子情報振興財団の協力(共催) を得、また文部省高等教育局専門教育課、日本電子機械 協会(EIAJ)、システム LSI 開発支援センター(VSAC)、 半導体理工学研究センター(STARC)、日本応用物理学 会、情報処理学会、電気学会、電子情報通信学会の協賛 をあわせて得ることができ、大変効果的で有意義なセミナーとなった。

本年度は VLSI 設計に関する 4つのコース(コース R: CMOS-RF 集積回路設計と演習( $12/5 \sim 12/15$  実施),コース D: HDL によるディジタル集積回路設計と演習( $12/18 \sim 12/21$  実施),コース A: アナログ集積回路設計と演習( $1/7 \sim 1/9$  実施),コース S: 最先端 VLSI設計実例(1/10, 1/11)を開催し,講師として大学・企

### 【社会人のためのリフレッシュセミナー】

図 1.4.2 平成 19 年度リフレッシュ教育ポスター

25

業の集積回路研究・教育に携わる教官や研究者 19 名を招聘し、VLSI 設計に関する講義や最新の CAD ツールを使用した実習をはじめ、最先端の VLSI 設計技術の紹

介を行った. 参加者はコース R, A, D, S はそれぞれ 24 名,37 名,44 名,100 名あり, 延べ 205 名となった.

図 1.4.3 平成 18 年度リフレッシュ教育会場風景 (東大 VDEC セミナー室)

## 表 1.4.2 リフレッシュセミナー開催状況

| 講習項目                                    | 開催日                          | 参加<br>人数 | 講師                                                                                                                                                                                          | 講習概要                                                                                                                                                                                                                      |

|-----------------------------------------|------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| コースR:<br>CMOS-RF集積回<br>路設計と演習           | 平成19年12月5-15日<br>先端知1Fセミナー室  | 24       | 松岡 俊匡 (大阪大学),<br>藤島 実 (東京大学)                                                                                                                                                                | ・基礎,分布定数回路<br>・RF CMOS 回路の基礎<br>・RF オンウェハ測定<br>・RF オンウェハ測定実習                                                                                                                                                              |

| コース D:<br>HDL によるディジ<br>タル集積回路設計<br>と演習 | 平成19年12月18-21日<br>先端知1Fセミナー室 | 37       | 今井 正治(大阪大学),<br>越智 裕之(広島市立大学),小林 和淑(京都大学),池田誠(東京大学)                                                                                                                                         | <ul> <li>・VerilogHDLの文法解説とシミュレーション演習</li> <li>・VerilogHDLによる論理合成/シミュレーションとFPGA実装演習</li> <li>・ハードウェア記述言語(HDL)による、ディジタル集積回路設計</li> <li>・LSI配置配線設計演習</li> </ul>                                                              |

| コース A:<br>アナログ集積回路<br>設計と演習             | 平成20年1月7-9日<br>先端知1Fセミナー室    | 44       | 杉本泰博(中央大学),<br>小野寺 秀俊(京都大学),<br>小谷 光司(東北大学)                                                                                                                                                 | <ul><li>・回路設計,回路シミュレーション</li><li>・アナログ集積回路の特徴と役割</li><li>・レイアウト設計,検証(DRC, LVS)</li></ul>                                                                                                                                  |

| コースS:<br>最先端 VLSI 設計実<br>例              | 平成20年1月10,11日<br>先端知1Fセミナー室  | 100      | 益子耕一郎 (STARC),<br>石原亨 (九大), 井上弘<br>士 (九大), 石原 昇 (群<br>馬大), 松澤 昭 (東京工<br>業大学), 田中 聡 (日立<br>製作所), 笠原 博徳 (早<br>稲田大学), 本田 晋也<br>(名古屋大学), 中村 宏<br>(東京大学), 服部 俊洋<br>(ルネサステクノロジ),<br>佐藤 寿倫 (九州大学), | ・先端アナログ設計 -CMOS RF回路と無線通信用LSIの設計 -CMOSアナログ回路設計の基礎 一だれもが簡単に設計できるようになる一 -PLL設計の基礎 ・先端デジタル設計 -高性能低消費電力マルチコアのための最先端並列化コンパイラ技術 -組込み向けマルチプロセッサOS技術 -アーキテクチャレベルの低消費電力化技術 -組み込み用途マイクロプロセッサSuperHにおける高性能低電力技術 -マイクロプロセッサのディペンダブル技術 |

# 【若手教官・学生のためのデザイナーズフォーラム】

学生および若手教官を対象とした VDEC LSI デザイナーフォーラム(VDEC LSI Designers Forum)を開催している。 VDEC LSI デザイナーフォーラムは、LSI 設計者が、互いの研究成果だけではなく、チップ設計で苦労した点、失敗事例と解決策、CAD 業界の裏話、研究室に於ける設計環境の構築法など、通常の研究会や学会

などでは得ることのできない情報を共有し、大学または研究室の枠を越えて研究者が連携を深めることを目的としている。2007年は、9月17日、18日に北海道新篠津村で開催された。昨年に引き続き、Ph.D. 企画セッションが企画、実行された。また、本フォーラム開催にあたって、会場・宿泊設備その他の準備、スタッフの手配等は、幹事大学のご協力により実現されている。平成19年度は、京都大学の土谷先生に幹事を務めて頂いた。

図 1. 4. 3 平成 18 年度リフレッシュ教育会場風景(東大 VDEC セミナー室)

## 表 1.4.3 平成 18 年度デザイナーズフォーラムプログラム

| 9/17 | 14:00-14:10 | 開会の挨拶                             |                 |

|------|-------------|-----------------------------------|-----------------|

|      | 14:10-14:40 | VDECの活動紹介                         | 池田 誠 (東大)       |

|      | 14:40-15:10 | 益研での高周波CMOS回路設計事例                 | 伊藤 浩之 (東工大)     |

|      | 15:10-15:20 | 休憩 10 分                           |                 |

|      | 15:30-17:00 | Ph.D 企画セッション「世界で活躍できるLSI研究者を目指して」 |                 |

|      | 17:00-18:30 | チェックイン・風呂                         |                 |

|      | 18:30-20:00 | 夕食・懇親会                            |                 |

|      | 20:00-22:00 | ポスターセッション                         |                 |

| 9/18 | 10:00-10:30 | ゼロから始めたLSI設計 ~雨宮研究室の設計事例を通して~     | 上野 憲一(北大 雨宮研)   |

|      | 10:30-11:00 | 埋め込み型検出回路によるプロセッサの電源雑音評価          | 深澤 光弥 (神戸大 永田研) |

|      | 11:00-11:30 | 半導体業界の歩き方                         | 名倉 徹 (東大)       |

|      | 11:30-11:4  | 休憩 (10分)                          |                 |

|      | 11:40-12:00 | 表彰式、閉会の挨拶                         |                 |

27

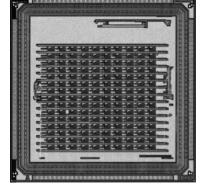

# 1.5 装置の整備・運用・利用公開

VDEC では、発足以来導入されてきた装置を維持管 理するとともに、全国大学教員に対し公開している(一 部装置は、試験公開中). 表 1.5.1 に装置の一覧と利用公 開の状況を示す。装置は、VLSI用大型テスターと、そ の他若干のプロセス装置とに大別できる. VDEC 発足 以来、東京大学工学部各号館へ分散配置されてきたが、 平成16年度末までに「武田先端知ビル」内の1階実験 室ならびに地下スーパークリーンルームに装置の移設が 完了し、これまで以上に有機的な連携をもって利用する ことができるようになった. また、平成16年度に株式 会社アドバンテストより最新鋭のテスター (T2000) と 電子線描画装置 (F5112+VD01) とが寄附された. 電 子線描画装置の19年4月~20年1月の利用実績は、3 大学・研究機構のスタッフと学生により、合計 999 回の 描画(うちマスク613枚,直接描画386回)であった. 昨年度より EB 描画装置は全国公開の準備が整い、同時 に必要経費の一部を競争的資金等から負担いただく仕組 みが整備された. さらに本年度より文部科学省「ナノテ クネットワーク」に参加したことで、より多くのユーザー に対する支援体制を整備しつつある.

平成9年度より各種治具の標準化に取り組んだ結果、 VDECが推奨する標準ピン配置に基づき試作したデジタルLSIは、治具をその都度作製することなく、VDEC

および拠点校の LSI テスターにより評価が行える体制 が整っている. さらに. 今後新たな品種の試作が可能に なった場合においても、品種に応じたドーターボードを 1種類準備することで、全国の各大学における LSI テス ターに対応可能な体制が整っている. 今後、LSI テスト 法およびLSIテスター利用法のセミナーを頻繁に開催す ることで一層の利用の促進を図り、 試作した LSI の特 性・性能評価が容易に行える環境の整備に努めたい. 試 作チップの評価に関しては、発足当初より QFP や BGA パッケージを実装できるソケットの頒布およびソケット のピンを標準 2.54mm ピッチに変換する変換ボードを開 発してきた. WEB 経由の申し込みにより購入すること ができる. 電子線描画装置, 集東イオンビーム加工装置 は、限られたスタッフのなかで、できるだけ多く利用機 会を設けたいという思想から、免許を持っている人間か ら一定期間装置利用法を習得し、試験に合格したのち利 用資格を与える「徒弟免許制度」を考案し、試験運用を 行っている.

公開されている装置に関しては、セミナーの受講者に対して利用者資格を認定し、利用は、利用者資格を有する者もしくはその同伴の場合による利用を原則としている。必要に応じ、VDECの職員などが対応することで、利用を認める場合もあるので、個別に相談いただきたい。

表 1.5.1 装置一覧および利用公開状況

| 項目                     | 装置名                                    | 説明                                                                                                         | 利用公開状況        | 連絡先                              |

|------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|----------------------------------|

| ロジック<br>LSIテスト<br>システム | ミックスシ<br>グナルLSIテ<br>スター:ITS<br>9000Exa | 100MHz/200MHz320ピンのデジタルピンおよび4<br>チャネルのアナログピンを有している. VDECにお<br>いて標準ピン配置で試作したチップを測定するため<br>の治具を揃えている         | 公開中           | ITS9000@vdec.<br>u-tokyo.ac.jp   |

|                        | EBテスター:<br>IDS5000ZX                   | 動作状態におけるチップ表面の電位を観測することで動作・不良解析を行う. 通常LSIテスターと組み合わせて使用するため、上述テスターとのドッキング治具を備える384ピン、1GHzまでのデジタル回路のテストを行える. | 公開中           | IDS5000@vdec.<br>u-tokyo.ac.jp   |

|                        | LSI テスター:<br>HP8300                    | 384ピン, 1GHz までのデジタル回路のテストを行える.                                                                             | 公開中           | HP83000@vdec.<br>u-tokyo.ac.jp   |

|                        | LSIテスター:<br>ADVANTEST<br>T2000         | 256ピン, 512MHzまでのデジタル回路のテストを行える. アナログオプションを整備中.                                                             | 試験公開中         | equipment@vdec.<br>u-tokyo.ac.jp |

|                        | 回路修正用<br>FIB: IDSP2X                   | LSIパターンの設計ミス等による配線ショート, オープンに対して, 配線の切断, 白金膜の生成によるジャンパーの生成が可能                                              | 公開中           | IDSP2X@vdec.<br>u-tokyo.ac.jp    |

|                        | オートプロー<br>バ: PM-90-A                   | ウエハ上でのLSIの動作検証を行うためのオートプローバ.上述のLSIテスターとドッキングして使用することが可能で、VDECにおいて標準ピン配置で試作したチップを測定するためのプローブカードを備えている       | 希望に応じ利<br>用可能 | equipment@vdec.<br>u-tokyo.ac.jp |

| ſ |                       |                                                       |                                                                                                 |                                                 |                                  |

|---|-----------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|

|   | アナログ・<br>RF測定シ<br>ステム | アナログ・RF<br>測定装置一<br>式: HP4156B,<br>HP4284, etc        | DCパラメータ測定,容量測定,ネットワークアナライザ,スペクトラムアナライザ等の測定装置                                                    | 希望に応じ利<br>用可能. 但し<br>VDECの業務<br>による利用を<br>優先とする | equipment@vdec.<br>u-tokyo.ac.jp |

|   |                       | 低雑音マニュ<br>アルプローバ:<br>Cascade社                         | マニュアルにて6インチまでのウエハ上のチップの<br>測定が可能. 測定には, 通常のプローブ針 (6本まで)<br>のほか, 50GHzまでの測定が可能な高周波プローブ<br>を2本備える |                                                 |                                  |

|   |                       | 低雑音・温度<br>制御機構付き<br>セミオートプ<br>ローバ: Süss<br>Microtec 社 | 8インチまでのウエハ上のチップの測定が可能. ウエハ温度を-50℃から200℃まで制御可能. プローブカードによる測定. GPIBを介した制御を行うことで半自動測定も可能           |                                                 |                                  |

|   |                       | 極低温プロー<br>バ:長瀬産業<br>株式会社                              | 5インチウエハを25Kまで冷やした測定が可能                                                                          | 要相談                                             | equipment@vdec.<br>u-tokyo.ac.jp |

|   | 電子線描画 システム            | マスク描画・ウ<br>エハ直描装置:<br>F5112+VD01                      | 半導体製造用 2.3mm 厚 4,5 インチマスクの描画およびエッチング、2-4 インチ並びに不定形ウエハへの直接描画が可能. 性能保障描画寸法 0.1 μ m.               | 公開中                                             | equipment@vdec.<br>u-tokyo.ac.jp |

|   | 汎用 FIB シ<br>ステム       | FIB装置:<br>SMI9800MSP                                  | ガラスマスクの欠陥修正の他, 断面観測のための加<br>工等が可能                                                               | 試験的に公開<br>中                                     | equipment@vdec.<br>u-tokyo.ac.jp |

29

# 1.6 VDEC 利用者に関する発表文献リスト

## 1. 研究論文

- B.B.M.W. Badalawa and M. Fujishima, "60 GHz CMOS pulse generator," Electronics Letters, Vol. 43, No. 2, pp. 100-102, 2007

- [2] M. Motoyoshi and M. Fujishima, "58.8/39.2 GHz dual-modulus CMOS frequency divider with 9.2x5.2 um core size," Electronics Letters, Vol. 43, No. 2, pp. 98-100, 2007

- [3] I.C.H. Lai and M. Fujishima, "Analysis of on-chip asymmetric coaxial waveguide structure for chip area reduction," Japanese Journal of Applied Physics, Vol. 46, No. 4B, pp. 2261-2264, 2007.

- [4] I.C.H. Lai, C. Inui and M. Fujishima, "CMOS on-chip stacked Marchand balun for millimeterwave applications," IEICE Electronics Express, Vol. 4, No. 2, pp. 48-53, 2007

- [5] Y. Goto and M. Fujishima, "Efficient quantum computing emulation system with unitary macro-operations," Japanese Journal of Applied Physics, Vol. 46, No. 4B, pp. 2278-2282, 2007.

- [6] I.C.H. Lai and M. Fujishima, "An integrated low-power CMOS up-conversion mixer using new stacked Marchand baluns," IEICE TRANS. ELECTRON, Vol. E90-C, No. 4, pp. 823-828, 2007

- [7] A. Oncu, B.B.M.W. Badalawa, and M. Fujishima, "22-29 GHz ultra-wideband CMOS pulse generator for short-range radar applications," IEEE Journal of Solid-State Cirsuits, Vol. 42, No. 7, pp. 1464-1471 July 2007

- [8] K. Ishibashi, I.C.H. Lai, K Takano, and M. Fujishima, "A scalable model of shielded capacitors using mirror image effects," IEICE Trans. Electron, Vol. E90-C No. 12 pp. 2237-2244 Dec 2007

- [9] 染谷隆夫, 桜井貴康, 高宮 真, 関谷 毅, "ワイヤ レス電力伝送シート," 応用物理, 第76巻, 第10号, pp. 1159-1163, 2007年10月.

- [10] K. Onizuka, K. Inagaki, H. Kawaguchi, M. Takamiya, and T. Sakurai, "Stacked-Chip Implementation of On-Chip Buck Converter for Distributed Power Supply System in SiPs," IEEE Journal of Solid-State Circuits, Vol. 42, No. 11, pp. 2404 2410, Nov. 2007.

- [11] K. Ishida, A. Tamtrakarn, H. Ishikuro, M. Takamiya, and T. Sakurai, "An Outside-Rail Opamp Design Relaxing Low-Voltage Constraint on Future Scaled Transistors," IEICE Transaction on Electronics, E90-C, No. 4, pp. 786-792, April 2007.

- [12] Y. Masui, T. Yoshida, M. Sasaki, A. Iwata, "0.6V Supply Complementary Metal Oxide Semiconductor Amplifier Using Noise Reduction Technique of Autozeroing and Chopper Stabilization," pp. 2252-2256, Japanese Journal of Applied Physics, Vol. 46, No. 4B, 2007

- [13] T. Yoshida, N. Ishida, M. Sasaki, A. Iwata, "Low-Voltage, Low-Phase-Noise Ring Voltage-Controlled Oscillator Using 1/f-Noise Reduction Techniques," pp. 2257-2260, Japanese Journal of Applied Physics, Vol. 46, No. 4B, 2007.

- [14] A. Iwata, T. Yoshida, M. Sasaki, "Low-Voltage and Low-Noise CMOS Analog Circuits Using Scaled Devices," pp. 1149-1155, IEICE Trans. Electron., Vol. E90-C, No. 6, 2007.

- [15] T.Choi, T.Sakamoto and Y.Sugimoto, "A Study to Realize a 1-V Operational Passibve  $\Sigma$   $\Delta$  Modulator by Using a 90nm CMOS Process," IEICE Trans. Electron., Vol. E90-C, No. 6, pp. 1304-1306, June 2007.

- [16] T. Iizuka, M. Ikeda, and K. Asada, "Timing-Aware Cell Layout De-Compaction for Yield Optimization by Critical Area Minimization," Very Large Scale Integration (VLSI) Systems, IEEE Transactions, Vol. 15, Issue 6, pp. 716-720, Jun. 2007.

- [17] 谷内出悠介,池田 誠,浅田邦博,"時分割投射光 による実時間高速高精度3次元モデル取得のた めの複数視点システム,"映像情報メディア学会, Vol. 62, No. 3, pp. 392-397, 2008年3月.

- [18] Atsushi Iwashita, Takashi Komuro, Masatoshi Ishikawa, "An Image-Moment Sensor with Variable-Length Pipeline Structure," IEICE Transactions on Electronics, Vol. E90-C, No. 10, pp. 1876-1883 (2007)

- [19] T. Ohzone, T. Sadamoto, T. Morishita, K. Komoku, T. Matsuda and H. Iwata, "A CMOS Temperature Sensor Circuit," IEICE Trans. Electron., Vol. E90-C, No. 4, pp. 895-902, April

### 2007.

- [20] M. Miyata, Y. Shibata, K. Oguri, "An optimization method focusing on fixed-point arithmetic in applications for dynamically reconfigurable processor," Systems and Computers in Japan 38 (14), pp. 20-28, (2007).

- [21] N. Kanda, K. Konishi, and M. Kuwata-Gonokami, "Terahertz wave polarization rotation with double layered metal grating of complimentary chiral patterns," Optics Express 15, 11117 (2007)

- [22] Myoren H., Kishita N., Taino T., Takada S., "Minimization of Parasitic Inductances in SFQ Circuits Using Over- and Under-Ground Planes," IEEE Trans. Appl. Supercond., Vol. 17, pp. 462-465 (2007).

- [23] Taino T., Ishii H., Yoshimura S., Otani C., Ariyoshi S., Myoren H., Kawase K., Shibuya T., Sato H., Shimizu M. H., Takada S., "Terahertz Electromagnetic-waves Detector Using Nb-based Superconducting Tunnel Junction on LiNbO3 Substrate Absorber," Physica C, 463-465, pp. 1119-1122 (2007).

- [24] Kenji Ide, Ryusuke Kawahara, Satoshi Shimizu, Takayuki Hamamoto, "Wide View Imaging System Using Eight Random Access Image Sensors," IEICE trans. on Electron, Vol. E90-C, No. 10, pp. 1884-1891 (2007).

- [25] 樽木久征,大野英,小野文枝,浜本隆之,佐々木朋詩,白井稔人,坂井正善,"環境光の影響を抑制した物体検出用イメージセンサ,"映像情報メディア学会誌, Vol. 61, No. 12, pp. 1810-1817 (2007).

- [26] 池岡宏,柏山英輝,浜本隆之,児玉和也,"多重フォーカス画像を用いたスマートイメージセンサによる距離計測,"映像情報メディア学会誌, Vol. 62, No. 3, pp. 384-391 (2008).

- [27] M.A. Abedin, Y. Tanaka, A. Ahmadi, T. Koide, and H.J. Mattausch, "Mixed Digital-Analog AssociativeMemory Enabling Fully-Parallel Nearest Euclidean Distance Search," Japanese Journal of Applied Physics (JJAP), Vol. 46, No. 4B, pp. 2231-2237, (2007)

- [28] M.A. Abedin, Y. Tanaka, A. Ahmadi, S. Sakakibara, T. Koide, and H.J. Mattausch, "Realization of K-Nearest-Matches Search Capability in Fully-Parallel Associative Memories," IEICE Trans. on Fundamentals, Vol. E90-A, pp. 1240-1243, (2007.5)

- [29] T. Kumaki, M. Ishizaki, T. Koide, H.J.

- Mattausch, Y. Kuroda, H. Noda, K. Dosaka, K. Arimoto, and K.Saito, "Acceleration of DCT Processing with Massive-Parallel Memory-Embedded SIMD Matrix Processor," IEICETrans. on Information & Systems, Vol. E90-D, No. 8, pp. 1312-1315 (2007.8)

- [30] K. Johguchi, H. J. Mattausch, T. Koide and T. Hironaka, "4-port unifieddata/instruction cache design with distributed crossbar and interleaved cache-linewords," IEICE Transactions on Electronics, Vol. E90-C, No. 11, pp. 2157-2160 (2007.11)

- [31] 大窪啓太, 神戸尚志, "特定用途向け低ビット複合 演算回路の一設計法," 情報処理学会論文誌第48 巻, 第5号, pp1918-1925, 2007年5月.

- [32] 中川, 上津, 神戸, "2次元ジグザグ走査による相関 値計算回路の設計とその評価," 第21巻, 第1号, pp18-27, システム制御情報学会論文誌, 2008

- [33] J.Akita, H.Takagi, K.Doumae, A.Kitagawa, M.Toda, T.Nagasaki, T.Kawashima, "Column-Parallel Vision Chip Architecture for High-Resolution Line-of-Sight Detection Including Saccade," IEICE Trans. on Electronics, Vol. E90-C, No. 10, pp. 1869-1875, 2007.10.

- [34] N. Ishihara, "Vdd Gate Biasing RF CMOS Amplifier Design Technique Based on the Effect of Carrier Velocity Saturation," IEICE Trans. Electron., Vol. E90-C, No. 9, pp. 1702-1707, 2007.

- [35] Hashimoto, Yamaguchi, Onodera, "Timing Analysis Considering Spatial Power/Ground Level Variation," pp. 2661-2668, Vol. E90-A, No. 12, IEICE Trans. on Electronics (2007)

- [36] Muta, Onodera, "Manufacturability-Aware Design of Standard Cells," pp. 2682-2960, Vol. E90-A, No. 12, IEICE Trans. on Electronics (2007)

- [37] Kobayashi, Katsuki, Kotani, Sugihara, Kume, Onodera, "A 90nm 48 × 48 LUT-Based FPGA Enhancing Speed and Yield Utilizing Within-Die Delay Variations," pp. 1919-1926, Vol. E90-C, No. 10, IEICE Trans. on Electronics (2007)

- [38] Kuboki, Tsuchiya, Onodera, "Low-Power Design of CML Driver for On-Chip Transmission-Lines using Impedance-Unmatched Driver," pp. 1274-1281, Vol. E90-C, No. 6, IEICE Trans. on Electronics (2007)

- [39] Tsuchiya, Hashimoto, Onodera, "Optimal

- Termination of On-Chip Transmission-Lines for High-Speed Signaling," pp. 1267-1273, Vol. E90-C, No. 6, IEICE Trans. on Electronics (2007)

- [40] Katsuki, Kotani, Kobayashi, Onodera, "A 90 nm LUT Array for Speed and Yield Enhancement by Utilizing Within-Die Delay Variations," pp. 699-707, Vol. E90-C, No. 4, IEICE Trans. on Electronics (2007)

- [41] N.Okada, M.Kameyama, "Low-Power Multiple-Valued Reconfigurable VLSI Using Series-Gating Differential-Pair Circuits," Journal of Multiple-Valued Logic & Soft Computing, Vol. 13, pp. 619-631 (2007)

- [42] Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, and M. Yoshimoto, "Area Comparison between 6T and 8T SRAM cells in Dual-Vdd Scheme and DVS scheme," IEICE Trans. Fundamentals, Vol. E90-A, No. 12, pp. 2695-2702, Dec. 2007.

- [43] Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, and M. Yoshimoto, "Area Optimization in 6T and 8T SRAM Cells Considering Vth Variation in Future Processes," IEICE Trans. Electron., Vol. E90-C, No. 10, pp. 1949-1956, Oct. 2007.

- [44] Masayuki Hiromoto, Shin'ichi Kouyama, Hiroyuki Ochi, and Yukihiro Nakamura, "A Retargetable Compiler for Cell-Array-Based Self-Reconfigurable Architecture," International Journal of Computer Science and Network Security, Vol. 7, No. 4, pp. 131-139, Apr. 2007.

- [45] Shin'ichi Kouyama, Tomonori Izumi, Hiroyuki Ochi, and Yukihiro Nakamura, "A Simulation Platform for Designing Cell-Array-Based Self-Reconfigurable Architecture," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, Vol. E90-A, No. 4, pp. 784-791, Apr. 2007.

- [46] 宮本 龍介, 劉 載勲, 筒井 弘, 中村 行宏, "可変ウィンドウ手法に基づく高精度ステレオマッチングプロセッサ," 画像電子学会誌, Vol. 36, No. 3, pp. 210-218, 2007年5月.

- [47] J. Wang, T. Matsuoka, and K. Taniguchi, "A Switched-Capacitor Programmable Gain Amplifier Using Dynamic Element Matching," IEEJ Transactions on Electrical and Electronic Engineering, Vol. 2, No. 6, pp. 600-607, Nov. 2007.

- [48] 井田,田中,松岡,谷口,"生体センシング用途向け

- 超低消費電力  $\Delta$   $\Sigma$  モジュレータ," 電子情報通信 学会論文誌 C, Vol. J90-C, No. 10, pp. 662-670, Oct. 2007

- [49] Y. Namatame, M. Maezawa, M. Moriya, K. Usami, T. Kobayashi, and Y. Mizugaki, "Voltage Doubler Cell for Rapid Single Flux Quantum Digital-to-Analog Converter," Japanese Jounral of Applied Physics, part 2, Vol. 46, No. 18, pp. L430-L432, April, 2007.

- [50] Y. Mizugaki, R. Kashiwa, M. Moriya, K. Usami, and T. Kobayashi, "Grounding positions of superconducting layer for effective magnetic isolation in Josephson integrated circuits," Journal of Applied Physics, Vol. 101, No. 11, pp. 114509-1-114509-4, June, 2007.

- [51] Y. Mizugaki, Y. Namatame, and M. Maezawa, "Design and operation of series array of voltage doubler cells for rapid-single-flux-quantum digital-to-analog converters," Superconductor Science and Technology, Vol. 20, No. 11, pp. S315-S317, October, 2007.

- [52] Y. Ogasahara, M. Hashimoto, and T. Onoye, "Measurement and Analysis of Inductive Coupling Noise in 90nm Global Interconnects," Vol. 43, No. 3, pp. 718-728, IEEE Journal of Solid-State Circuits (2008).

- [53] M. Hashimoto, J. Yamaguchi, T. Sato, and H. Onodera, "Timing Analysis Considering Temporal Supply Voltage Fluctuation," Vol. E91-D, No. 3, pp. 655-660, IEICE Trans. on Information and Systems (2008).

- [54] M. Hashimoto, J. Yamaguchi, and H. Onodera, "Timing Analysis Considering Spatial Power/ Ground Level Variation," Vol. E90-A, No. 12, pp. 2661-2668, IEICE Trans. on Fundamentals (2007).

- [55] M. Hashimoto, T. Ijichi, S. Takahashi, S. Tsukiyama, and I. Shirakawa, "Transistor Sizing of LCD Driver Circuit for Technology Migration," Vol. E90-A, No. 12, pp. 2712-2717, IEICE Trans. on Fundamentals (2007).

- [56] Y. Ogasahara, T. Enami, M. Hashimoto, T. Sato, and T. Onoye, "Validation of a Full-Chip Simulation Model for Supply Noise and Delay Dependence on Average Voltage Drop with On-Chip Delay Measurement," Vol. 54, No. 10, pp. 868-872, IEEE Trans. on CAS-II (2007).

- [57] Y. Ogasahara, M. Hashimoto, and T. Onoye,

- "Quantitative Prediction of On-Chip Capacitive and Inductive Crosstalk Noise and Tradeoff between Wire Cross-Sectional Area and Inductive Crosstalk Effect," Vol. E90-A, No. 4, pp. 724-731, IEICE Trans. on Fundamentals (2007).

- [58] K. Ohhata, K. Yayama, Y. Shimizu, and K. Yamashita, "A 1-GHz, 56.3-dB SFDR CMOS track-and-hold circuit with body-bias control circuit," IEICE Electronics Express, Vol. 4, No. 22, pp. 701-706.

- [59] K. Nakayama, M. Takata, T. Kasai, A. Kitagawa, J. Akita, "Pulse number control of electrical resistance for multi-level storage based on phase change," J. Physics D, Vol. 40, pp5061-5065 (2007).

- [60] Yoshio Mita, Kenichiro Hirose, Masanori Kubota, and Tadashi Shibata, "Deep-Trench Vertical Si Photodiodes for Improved Efficiency and Crosstalk," IEEE Journal of Selected Topics on Quantum Electronics, Vol. 13, No. 2, March/April (2007.3).

- [61] Wada, Y.; Tsutsui, K.; Nakata, M.; Morita, M.; Tokuda, M.; Nagatsuma, K.; Onozato, H.; Kaneko, T.; Edura, T.; Mita, Y.; Koinuma, H., "Novel fabrication technologies of planar nanogap electrodes for single molecule evaluation," Current Applied Physics, v 7, n 4, May 2007, p 329-333 (2007.05)

- [62] Kenichiro Hirose, Fumitaka Shiraishi, and Yoshio Mita, "Simultaneous vertical and horizontal as-deposition self-patterning method on deep three-dimensional micro structures applied to vertically buried inductors," Journal of Micromechanics and Microengineering, Vol. 17, No. 7, pp. S68-S76 (2007.07) doi:10.1088/0960-131 7/17/7/S02.

- [63] Y.-A. Chapuis, Lingfei Zhou, Yamato Fukuta, Yoshio Mita, and Hiroyuki Fujita, "FPGA-based decentralized control of arrayed MEMS for microrobotic application," IEEE Transactions on Industrial Electronics, Vol. 54, No. 4, Aug. 2007, p 1926-36 (2007.08)