平成21年度 東京大学大規模集積システム設計教育研究センター **年 報**

### VLSI Design and Education Center The University of Tokyo

大規模集積システム設計教育研究センター (VDEC) の2008年度活動報告をお送りします.

2008年度、VDECのチップ試作事業では新たにCMOS 65nmの試作を、STARC/㈱イーシャトルの協力を得て開始いたしました。7月の先行ランに引き続き、10月と11月には経済産業省からの技術開発委託を受けたSTARCにVDECが協力する形で、多数の大学の設計者の方々に65nm試作の機会を提供することができました。経済産業省、STARC並びに㈱イーシャトルのご関係の方々に深く感謝いたします。これらの試作評価で得られた多くの貴重な研究成果は、STARCを通じて経済産業省にフィードバックされ、広く半導体産業技術の高度化に寄与することと期待しています。CMOS 65nm技術による先端チップ試作活動は2009年度も引き続き進める予定でおり、わが国の大学のLSI設計試作研究および教育がさらに進展することを期待しています。

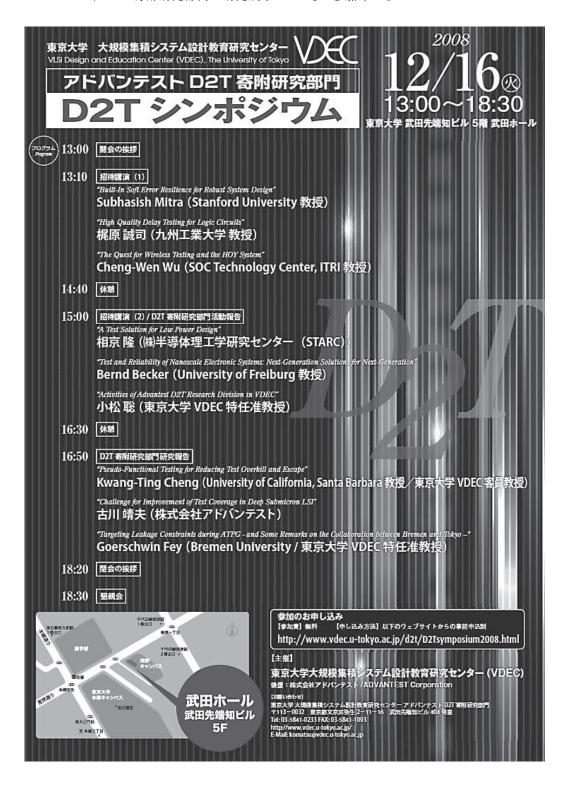

(株アドバンテストからの寄付研究部門(D2T:Design-to-Test)は2年目を迎え, ブレーメン大学およびカリフォルニア大学サンタバーバラ校より設計検証, テスト技術の著名な研究者を客員教授として招聘することができました. これらの研究者とアドバンテストからの研究員, 同部門の小松聡准教授らによる研究教育活動の成果が着々と出てきています. さらに2008年12月には内外の著名な研究者をお招きした, 第二回D2T講演会を開催し多くの参加をいただきました.

2008年度からはVDECデザイナーズフォーラムも企画を一新し、6月にVDECにて開催いたしました。従来の企画に加えて先端半導体技術や産業界のリーダの方々による特別講演会を開催し、多数の方々の参加を得、ご好評をいただきました。今後も順次新企画を立てていく予定です。

65 nm 以外のチップ試作では、一旦減少した CMOS 0.18 um の利用が持ち直しつつあると考えています。 今後、アナログ用の設計技術データを充実するとともに、設計規則のコンパティビリティを維持しつつ高耐圧 トランジスタオプション等を追加し、より広い応用分野で利用できるようにする計画です。是非、ご利用のほどお願い申し上げます。

歴史始まって以来の世界的金融・経済危機、半導体業界のダイナミックな再編成等の中で、ともすれば学生の分野志向は半導体、あるいはエレクトロニクスから離れていくことが心配されています。しかしどのような状況においてもLSI設計技術は情報通信技術等、先端技術の中核であり続けるとの強い信念のもと、優れた人材を多数育成するための活動を続ける所存です。皆様からの引き続きのご支援ご支持をお願い申し上げる次第です。

2009年6月

(全国共同利用施設)

東京大学大規模集積システム設計教育研究センター

ヤンター長

VLSI Design and Education Center The University of Tokyo

# **2009**

| 第1章 |                   | C 事業の紹介と平成 20 年度事業報告 ·······                                  | 2   |

|-----|-------------------|---------------------------------------------------------------|-----|

|     | 1.1<br>1.2<br>1.3 | VDEC の活動概況 — 2<br>CAD ソフトウェアの整備 — 5<br>平成 20 年度 VDEC 事業報告 — 7 |     |

|     | 1.4               | CAD セミナー — 10                                                 |     |

|     | 1.6               | 装置の整備・運用・利用公開 — 14<br>VDEC 利用者に関する発表文献リスト — 16                |     |

|     | 1.8               | 平成 21 年度の活動計画 — 79<br>VDEC 発ベンチャー — 80                        |     |

|     | 1.9               |                                                               |     |

| 第2章 | 「アド               | バンテスト D2T 寄付研究部門」活動報告 ·······                                 | 82  |

|     |                   |                                                               |     |

| 第3章 |                   | <b>プ試作報告 ····································</b>             | 93  |

|     | 3.2               | チップ種別一覧 — 103                                                 |     |

|     |                   | 各チップの詳細 — 110                                                 |     |

| 第4章 |                   | <b>C 概要</b>                                                   | 189 |

|     | 4.2               | 人事報告 — 190                                                    |     |

|     |                   | 決算報告 — 192                                                    |     |

| 第5章 |                   | <b>服告 ····································</b>                | 193 |

|     | 5.2               | 研究室構成員(平成 20 年度)—194                                          |     |

|     |                   | 研究概要 — 196<br>研究発表 — 218                                      |     |

|     |                   | 特許・受賞等 — 224                                                  |     |

| 第6章 |                   |                                                               | 226 |

|     | 6.1               | VDEC の利用規定・申し込みガイド — 226<br>IP データベースの整備 — 230                |     |

# 第 1 章 VDEC 事業の紹介と平成 20 年度事業報告

# 1.1 VDEC 事業の紹介と平成 20 年度事業報告

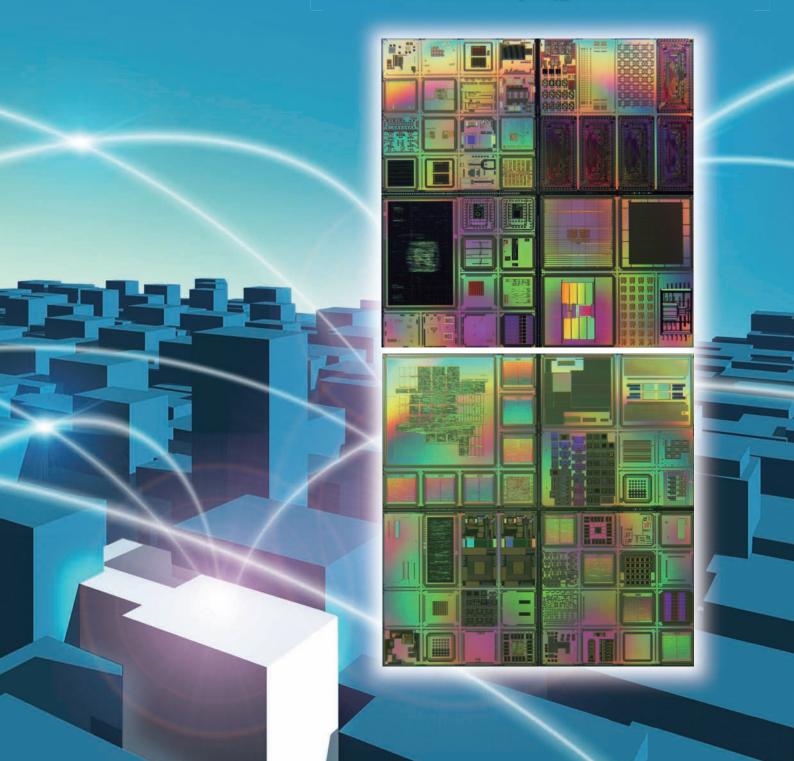

東京大学大規模集積システム設計教育研究センター (VDEC) は発足後12年が過ぎた. 平成20年度も『LSI教育情報の発信拠点形成』,『VLSI設計支援教育用CADソフトウェアの整備』,『VLSIチップ試作支援』を3つの柱として,円滑な運営を目指した事業を展開した. 図1.1に示すVDECの活動内容に基づき,以下に平成20年度の概要を報告する.

VDEC の使命は全国の国公私立大学および高専の LSI 設計研究・教育を高度化し、産業界に対しても優秀な LSI 設計技術者を数多く送り出すことである. しかし, VDEC 発足当初、我が国の大学には CAD ソフトウェア 利用技術教育や実用的 LSI 設計フロー教育のカリキュ ラムはほとんど存在していなかったため VDEC にとっ てはこれらの整備が急務の課題であった. CADソフト ウェアの利用技術に関しては CAD ベンダーが独自の設 計技術を有しており、これを導入することとした。大学 院学生、若手教官を対象として CAD ベンダーから講師 を招き、それぞれの CAD ソフトウェア毎に年 2 回のセ ミナーを開催することとし、CAD ベンダーと契約を結 んだ. これまで年2回の内1回はVDECで. 残り一回 は地方拠点校で実施している.参加定員は設備の関係で それぞれ20~50名程度であり必ずしも十分とはいえな いが、VDEC としては各ユーザ研究室内で"技術伝承" され、VDEC 主催のセミナーがトリガーとなって CAD 利用技術が全国的に広がることを期待している(1.3章 参照).

LSI 設計フローセミナーは LSI 設計の基本概念教育と

複数の CAD ツールを連携する実用的設計例の体験教育である。この目的で VDEC では社会人のリフレッシュ教育プログラムと兼ねて LSI 設計教育セミナーを年1回(12月~1月)開催している。このコースは"ディジタル設計コース","アナログ設計コース","RF設計コース","最先端設計事例コース"の4コースからなっている。前3者は演習を伴う体験教育コースであり,主要大学の経験豊かな教官を講師に招いて実施している。最先端設計事例コースは講義主体のコースであるが,大学および企業から第一線の講師を招き,設計経験をもとにした講演を行っている。

これらセミナーに加えて VDEC では年1回, 若手教官と学生を中心とした VDEC デザイナー・フォーラムを開催している。これはワークショップ形式の会合であり,企業・大学からの招待講演に交えて,参加者が設計事例を持ち寄ってその成功談,失敗談を交換する。これから設計を始めたいと考えている学生・教官もここでさまざまなノウハウを得ることができる。

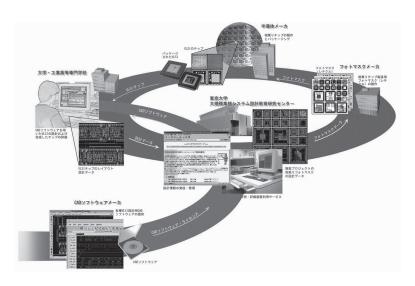

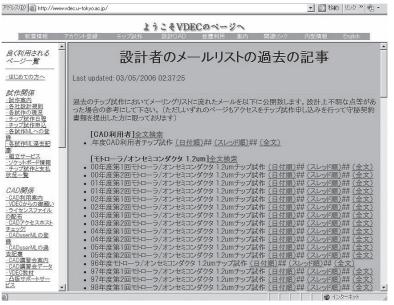

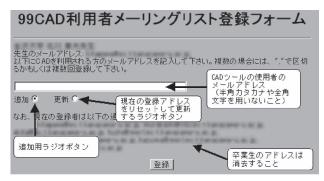

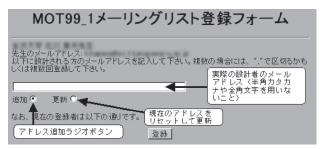

このようなセミナー、フォーラムを通じた教育システムにより LSI 設計の基本的項目を学習できるようになっているが、それでも実際の LSI 設計の場面では、さまざまな困難に直面することが多い。初心者にとってはCAD ソフトウェアのセットアップは最大の問題である。セットアップの後も CAD ソフトウェアが発する "難解なエラーメッセージ"でとまどうことも多い。このような場合に力を発揮するものが VDEC メールグループである。VDEC ユーザは VDEC のホームページから CAD

図 1.1 VDEC の活動内容

3

メールグループや試作技術対応のユーザグループに登録することができ、そこに直面する疑問点を投稿し、助けを求めることができる。メールグループの登録ユーザはそれに回答する義務を負っているわけではないが、ほとんどの場合、数時間から数日以内に経験豊かなユーザからの支援を得ることができる。また、今まで蓄積されてきたメールグループの情報が VDEC の WEB 上で認証された VDEC ユーザへ公開され、教育上の資産として残していく仕組みになっている。(図 1.2).

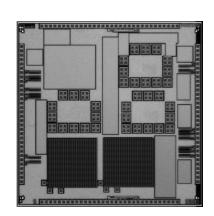

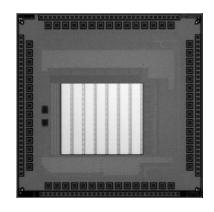

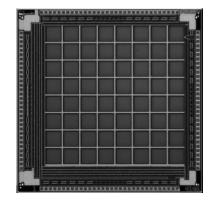

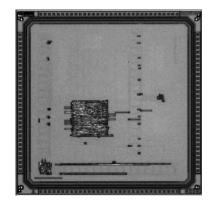

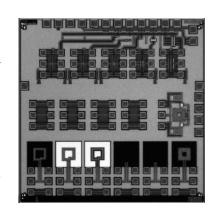

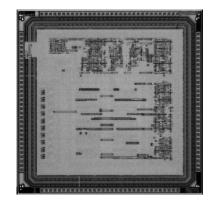

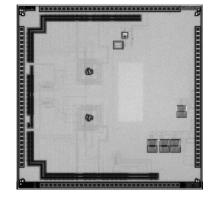

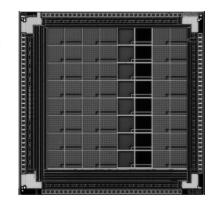

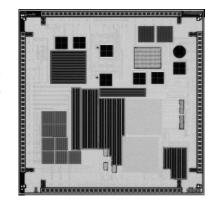

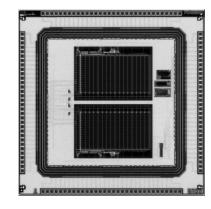

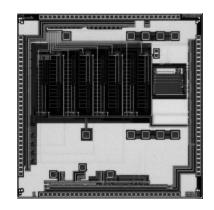

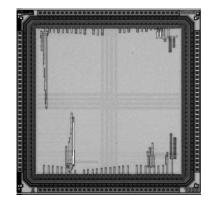

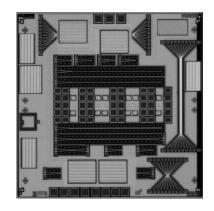

VLSI チップ試作支援に関しては、従来のオンセミ 1.2  $\mu$ m CMOS およびローム  $0.18\,\mu$ m CMOS 試作に加え、eShuttle  $65\,\mathrm{nm}$  CMOS、日立 SiGe  $0.25\,\mu$ m BiCMOS を実施した。さらに、VDEC では現在のサービス項目に載っていない BiCMOS、SiGe 等について、アメリカの MOSIS との連携で、アカデミック価格で試作を行って

いる.

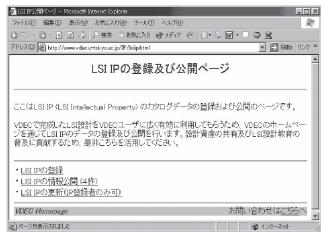

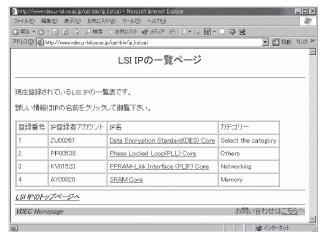

また、一流のLSI 設計者を目指す学生に対してインセンティブを与える仕組みとしてLSI IP アワードを実施している。本アワードは半導体各社と日経 BP 社の支援でスタートした IP 開発支援のしくみである。平成 19年度に新設された東芝 MeP 賞の第一回表彰式が第 10回 LSI IP デザイン・アワード表彰式の場で行われ 2 件が表彰された。(図 1.3).

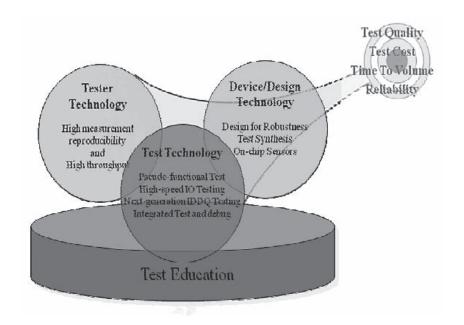

平成19年10月に設置されたアドバンテスト社から寄付部門「Design To Test (D2T)」では、LSIのテストに関する教育の充実とともに、設計とテストの架け橋を目指した研究が進められ、平成20年度には、Gorschwin Fey 先生、Tim Cheng 先生を客員准教授、客員教授招聘した。これまでの活動を振り返ると、VDEC 発足以来10年余の活動の中でLSI設計文化が根

図 1.2 VDEC メーリングリスト検索システム

図 1.3 LSI IP 賞

付いた研究室や大学ではすでに活発な設計研究・教育がスタートしている。図1.4に VDEC を利用した研究成果の指標として、VDEC に関係する発表文件数の推移を示す。単純に比較はできないが発表文献の数は増加傾向にあり、VDEC 発足以来、集積回路に関係する研究が活性化されていることが確認できる。

図 1.-5 に VDEC に関係する発表文献の VDEC ファシリティー利用状況を示す. 論文執筆にあたり CAD ソフトウェアが幅広く利用されていることが確認できる.

CADソフトウェアはチップ設計だけでなくチップ試作の準備段階で利用される場合が多いため、研究の基本アイデアを実証するツールとしての貢献度も大きい.また、研究論文には最先端のプロセステクノロジが好んで利用される傾向にあり世界的には65 nm CMOS から45 nm CMOS による設計事例報告が増加しており、VDEC においても最先端プロセステクノロジメニューの充実をはかっていきたい。そのほかのファシリティーとして、LSIテスターやFIB 加工装置、EB 描画装置などが研究目的に幅広く利用されることを期待する.

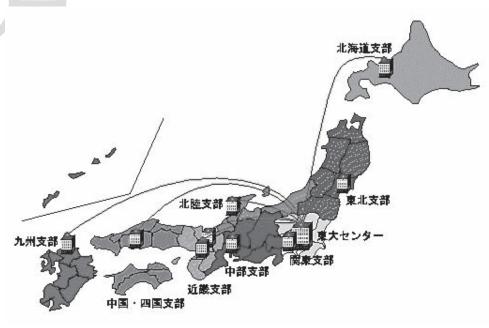

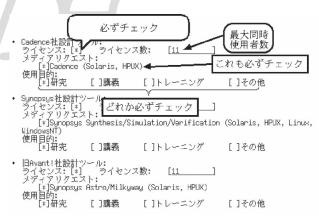

# 1.2 CAD ソフトウェアの整備

平成8年度から整備を行っているCADソフトウエアは、平成20年度は表1.1に示すツール群を全国の大学に提供している。CADソフトウエアの利用は、図1.2に示す全国地域拠点校10箇所にライセンスサーバを設置し、全国各大学の利用者が手許の計算機にインストールしたCADソフトウエアを、最寄のライセンスサーバにおいて認証を行うことで、ネットワークを利用した運用形態となっている。ライセンス数はCADの項目ごとに100から1000程度のフローティングライセンスとなっ

ており、全国の国・公・私立大学・高専において教育・研究目的に限り利用できるようになっている.

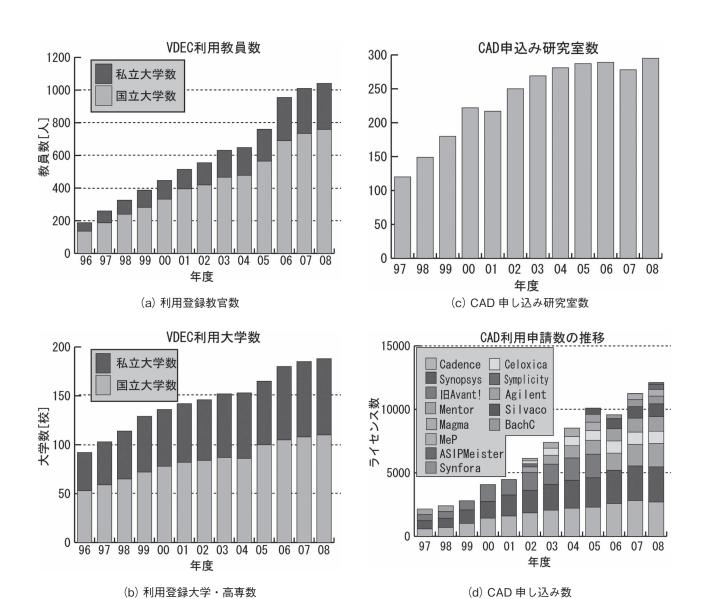

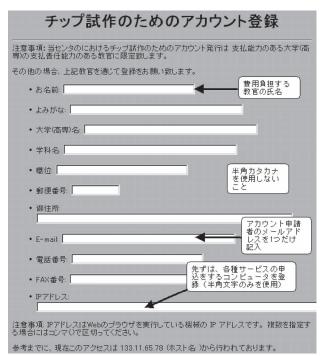

VDECのCADの利用、および「1.3章」のチップ試作の利用のためには、あらかじめユーザ登録が必要となっているが、これまで VDEC に利用登録をしている (a) 全国教官数および (b) その所属する大学数および (c) CADの利用申請があった研究室(教官)数の推移は図1.7の通りである.

表 1.1 導入された CAD システム

| 名称                  | 用途                                                                                                                       | メーカ                          |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Cadence 社設計システム     | VerilogHDL/VHDLベースの入力、シミュレーション、論理合成、テスト生成、マクロセルを含むセルベースの配置配線とバックアノテーション、会話型の回路図およびマスクレイアウト入力、アナログ機能・回路シミュレーション、設計検証、回路抽出 | Cadence Design Systems, Inc. |

| Synopsys社設計システム     | VerilogHDL/VHDLシミュレーション、論理合成、<br>テスト生成、マクロセルを含むセルベースの配置<br>配線設計とバックアノテーション、回路シミュレー<br>ション、デバイスシミュレーション                   | Synopsys, Inc.               |

| レイアウト検証システム         | レイアウトのデザインルールチェック及び検証                                                                                                    | Mentor Graphics Co. Ltd.     |

| Silvaco社設計ツール       | 高速回路シミュレーション,                                                                                                            | Silvaco                      |

| 高周波回路設計検証システム       | 通信機器や関連デバイスなどの高周波回路/システムの設計,検証                                                                                           | Agilent Technologies         |

| C言語ベース設計システム        | Handel-C でシステム設計,合成,検証                                                                                                   | Celoxica/Agility             |

| C言語ベース設計システム        | BachC 設計ツール                                                                                                              | Sharp                        |

| 高位合成ツール             | PICO Express                                                                                                             | Synfora                      |

| レイアウト表示<br>プラットフォーム | LAVIS                                                                                                                    | TOOL                         |

図 1.6 全国地域拠点校

図 1.7 ユーザ登録数および CAD 申込数の推移

# 1.3 平成 20 年度 VDEC 事業報告

#### 1.3.1 VLSIチップ試作

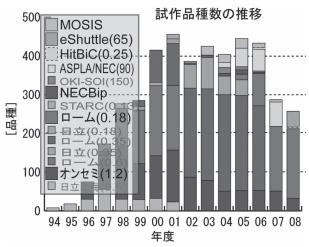

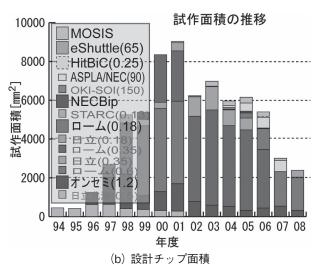

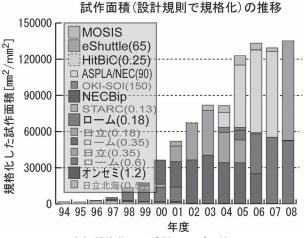

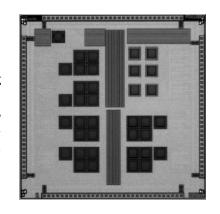

図 1.3.1 は、VDEC および、それに先行して行われたパイロットプロジェクトでのチップ試作数の推移を示したものである.

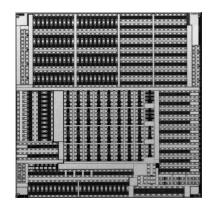

VLSI チップ試作は、平成 6,7年度(1994,1995年 度) のパイロットプロジェクトでは、ファウンドリは NEL 社の CMOS 0.5 μm (当該プロセスはその後日立北 海セミコンダクタ社に継続) 1社であったが、平成8年 度(1996年度)の VDEC 発足後、日本モトローラ社の CMOS 1.2 µm (平成 11 年度からは、オン・セミコンダ クターにて継続)が協力を開始し、平成9年度からはロー ム社の CMOS 0.6 μm が加わった. さらに平成 10 年度 には日立製作所の CMOS 0.35 μm, 平成 11 年度にはロー ム社 0.35 μm がそれぞれ加わった. また, IP 開発プロジェ クトの一環として STARC 0.13 μm の試作を行った. 平 成13年度から、日立製作所のCMOS 0.18 μm のサービ スを実施している。平成14年度は、広島大学岩田先生 の主導の下に、VDEC と MOSIS の協力による試作サー ビスを試行的に実施した. これは、TSMC、IBM といっ た海外のファブを MOSIS を経由することで格安で提供 するものである. さらに,東京大学柴田先生主導の元に, NEC 化合物デバイス株式会社によるバイポーラ LSI の 試作サービスも行った. 平成16年からテスト試作とし て沖電気 CMOSSOI 0.15 µm プロセスおよび ASPLA 90 nm(現在はSTARCにおいて継続)プロセスの試作 を開始し、90 nm 試作については平成17年度より通常 の試作として公募の形で運用を行っている. さらに平成 18年度からはローム社 0.18 µm の試作を開始し、日立 製作所 0.25 μ mSiGeBiCMOS のテスト試作を実施した. 平成 19 年度で終了した 90 nmCMOS の後継の先端プロ セスの検討を平成19年度から開始し、平成20年度に eShuttle 社の 65 nmCMOS による試作を開始した.

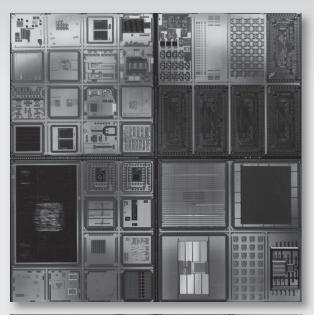

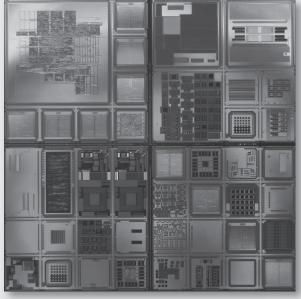

図 1.3.1 (a) は設計されたチップ品種数を示す. 図中の棒グラフは、試作品種数の順調な増加を表しており、VLSI 試作研究・教育に直接的に係わった学生数を表しているものと考えられることから、研究・教育効果が劇的に向上していることが想像される. 試作されたチップの品種数は、02 年度に減少しているが、これは ROHM社の 0.6 umプロセスを終了したことによる現象が考えられる. またそれ以降ほぼ 400 品種程度で推移しているが、その中でより微細なプロセスへ試作の中心が推移していることが読み取れる. また昨年度で  $0.35~\mu$ m が修了し、 $0.18~\mu$ m への移行したため、試作数が 100 品種程度減少する結果となっている.

図 1.3.1 (b) に設計されたチップ面積を示す。試作プロセスが微細化すると、集積度が向上することで、見かけ上試作面積が減少するように見える場合がある。そこで、図 1.3.1 (c) に試作面積をそれぞれの試作プロセスにおける特性寸法で規格化した、規格化試作面積の傾向

(a) 設計チップ品種数

(c) 規格化した設計チップ面積

図 1.3.1 チップ試作数・面積推移

8

#### も併せて示す.

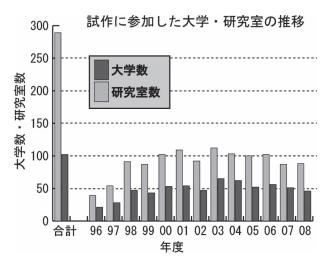

また、図1.3.2 にこれまでに試作に参加した教員数、大学数の推移およびその累計を示す。また、チップ試作に必要な設計規則などの、試作会社固有の機密情報にアクセスするための「機密保持契約」締結教員数は、オンセミコンダクタが159名、ロームの0.18 um プロセスが160名、eShuttle 65 nm が28名となっている。なお、ローム 0.35 um プロセス、ASPLA/STARC 90 nm プロセスに対する守秘契約締結教員数はそれぞれ207名、55名であった。

#### 1.3.2 平成 20 年度チップ試作概況

平成20年度は、表1.3.1に示す日程でチップ試作を 行った.チップ試作の参加者・試作の内容は、第2章の チップ試作報告を参照されたい.

図 1.3.2 VDEC チップ試作参加教員数・大学数の推移と その累計

#### 表 1.3.1 平成 20 年度チップ試作日程

●CMOS 1.2 um (オンセミコンダクタ:旧日本モトローラ)

|           | 試作申込開始    | 試作申込締切   | 設計締切       | 納品・試作完了        |

|-----------|-----------|----------|------------|----------------|

| 平成19年度第2回 | 2007/10/1 | 2007/1/7 | 2008/ 3/31 | 2008/6/30      |

| 平成20年度第1回 | 2008/ 4/2 | 2008/7/2 | 2008/10/ 6 | 2009/1/30      |

| 平成20年度第2回 | 2008/10/1 | 2009/1/7 | 2009/ 4/ 6 | 2009/7/13 (予定) |

#### ● CMOS 0.18 um (ローム)

|             | 試作申込開始     | 試作申込締切     | 設計締切       | 納品・試作完了         |

|-------------|------------|------------|------------|-----------------|

| 平成19年度第8回   | 2007/ 7/10 | 2007/11/12 | 2007/12/10 | 2008/ 4/ 2      |

| 平成19年度第9回   | 2007/ 8/13 | 2007/12/ 3 | 2008/ 1/15 | 2008/4/2        |

| 平成19年度第10回  | 2007/ 9/10 | 2008/ 1/ 7 | 2008/ 2/18 | 2008/ 5/28      |

| 平成20年度第 1 回 | 2007/11/ 5 | 2008/ 4/ 7 | 2008/ 5/12 | 2008/ 9/17      |

| 平成20年度第 2 回 | 2008/ 1/ 7 | 2008/ 5/ 6 | 2008/ 6/16 | 2008/ 9/17      |

| 平成20年度第3回   | 2008/ 2/ 4 | 2008/ 6/ 9 | 2008/ 7/14 | 2008/11/13      |

| 平成20年度第 4 回 | 2008/ 3/10 | 2008/ 7/ 7 | 2008/ 8/18 | 2008/11/13      |

| 平成20年度第 5 回 | 2008/ 4/ 7 | 2008/ 8/11 | 2008/ 9/16 | 2008/12/ 3      |

| 平成20年度第 6 回 | 2008/ 5/ 6 | 2008/ 9/ 8 | 2008/10/14 | 2009/ 2/24      |

| 平成20年度第7回   | 2008/ 6/ 9 | 2008/10/ 6 | 2008/11/17 | 2009/ 2/24      |

| 平成20年度第8回   | 2008/ 7/ 7 | 2008/11/10 | 2008/12/ 8 | 2009/ 5/25 (予定) |

| 平成20年度第 9 回 | 2008/ 8/11 | 2008/12/ 1 | 2009/ 1/13 | 2009/ 5/25 (予定) |

| 平成20年度第10回  | 2008/ 9/ 8 | 2009/ 1/ 7 | 2009/ 2/16 | 2009/ 5/25 (予定) |

● Bipolar (NEC) 試作申込がなく、試作を実施せず

#### CMOS 65 nm (eShuttle/STARC)

|           | 試作申込開始 | 試作申込締切 | 設計締切       | 納品・試作完了         |

|-----------|--------|--------|------------|-----------------|

| 平成19年度    |        |        | 2008/ 7/ 2 | 2008/10/ 3      |

| 平成20年度第1回 |        |        | 2008/10/ 2 | 2008/12/ 8      |

| 平成20年度第2回 |        |        | 2008/11/20 | 2009/ 3/27      |

| 平成20年度第3回 |        |        | 2009/ 2/19 | 2009/ 5/12 (予定) |

#### ● SiGeBiCMOS 0.25 um (日立)

| 試作申込開始 | 試作申込締切 | 設計締切       | 納品・試作完了        |

|--------|--------|------------|----------------|

|        |        | 2008/12/25 | 2009/4/30 (予定) |

#### 1.3.3 ライブラリ整備状況

VDEC におけるチップ試作(主にディジタル LSI 試作) セスの試作において、利用では、設計ライブラリの整備が重要である。VDEC では、 に示すとおりとなっている。 VDEC 提供 CAD ソフトウエア中のライブラリ生成ツー

ルを利用して、平成8年度から順次ライブラリ整備事業を行ってきている。現状では、VDECにおける各プロセスの試作において、利用可能なライブラリは表1.3.2に示すとおりとなっている。

#### 表 1.3.2 VDEC で利用可能なライブラリ

| プロセス         | 名称                | 作成者                                                         | 内容                            | 状況 |

|--------------|-------------------|-------------------------------------------------------------|-------------------------------|----|

| MOT (OnSemi) | P2lib 京都大学小野寺研究室  |                                                             | ・Synopsys用論理合成ライブラリ           |    |

| 1.2μm        |                   |                                                             | ・VerilogXL用シミュレーションライブラリ      |    |

|              |                   |                                                             | ・Astro用配置配線ライブラリ              |    |

|              | EXDlib            | 東京大学VDEC                                                    | ・Synopsys用論理合成ライブラリ           |    |

|              |                   |                                                             | ・VerilogXL用シミュレーションライブラリ      |    |

|              |                   |                                                             | ・Astro用配置配線ライブラリ              |    |

| ローム0.18µm    | ローム提供 ローム提供       |                                                             | ・Synopsys用論理合成ライブラリ           |    |

|              | ライブラリ             | スタンダードセル, IO<br>セル, RAM (セルはす<br>ベてブラックボックス)<br>(CDROMにて配布) | ・VerilogXL用シミュレーションライブラリ      |    |

|              |                   |                                                             | ・配置配線用LEF/DEFファイル             |    |

|              | 京大ライブ             | 京都大学小野寺研究室                                                  | ・Synopsys用論理合成ライブラリ           |    |

|              | ラリ                |                                                             | ・VerilogXL用シミュレーションライブラリ      |    |

|              |                   |                                                             | ・Astro用配置配線ライブラリ              |    |

|              | 東大ライブ ライブラリ情報は京都大 |                                                             | ・CadenceRTLCompiler用論理合成ライブラリ |    |

|              | ラリ                | 学小野寺研究室,東大<br>VDECにてフロー構築                                   | ・VerilogXL用シミュレーションライブラリ      |    |

|              |                   |                                                             | ・CadenceEncounter用配置配線ライブラリ   |    |

# 1. 4 セミナー

LSI 設計技術の向上にはセミナーは欠くことができな い存在である. 平成20年度にも, CAD利用のための技 術セミナー、社会人のためのリフレッシュセミナー、若 手教官・学生のためのデザイナーズフォーラム等のセミ ナー,フォーラムを企画,実施した.

#### 【CAD 利用のための技術セミナー】

CAD 利用のための技術セミナーでは、VDEC で使用 可能な Cadence, Synopsys, Agilent など CAD ベン ダーのそれぞれの CAD ツールの操作方法等を各ツー ルベンダーから講師を派遣していただき講習を行って いる. また、VDEC環境での設計フローに関する講習 も VDEC スタッフで実施している. 平成 20 年度は, 8 月と9月に初心者を対象とした第1回のCAD利用の ための技術セミナーを東京大学 VDEC で実施した. こ の技術セミナーでは、Cadence のツールを 4 種・6 日 間, Synopsys ツールを 3 種・4 日間, Agilent のツール を1種・2日間、東芝ツールを1種・2日間、Xilinxの ツールを 1種・1日間に加え、VDECEDA 環境におけ るトランジスタレベル設計手法講習会・VDECEDA 環 境におけるデジタル設計手法講習会を VDEC 教員が講 師となりそれぞれ2日間ずつ行った. 各コースに40名 までの教官・学生の受講があり、各ツールの使用方法や VDEC ライブラリを用いた VLSI 設計フローを修得して いる. また3月には上級者を対象としたCAD技術セミ ナーとして Cadence 3種・6日間, Synopsys 4種・5日 間, ASIPMeister 1 種・2 日間行った (表 1.4.1). これ ら CAD 技術セミナーへの参加要望は非常に大きく、地

| 講習項目                             | 開催地   | 開催時期    | 参加人数 | 講習内容                                                       |

|----------------------------------|-------|---------|------|------------------------------------------------------------|

| Xilinx講習会                        | 東京大学  | 8/5     | 16   | 論理合成ツールによる, 合成条件, 結果の解析, 階層設計を行う場合のストラテジなどを学習              |

| VDEC環境におけるデジタル回路<br>設計方法講習会      | 東京大学  | 8/21-22 | 33   | VDEC環境で回路設計を進めるための一連のフローを学習する.                             |

| VDEC環境におけるトランジスタ<br>レベル設計方法講習会   | 東京大学  | 8/25-26 | 30   | VDEC環境で回路設計を進めるための一連のフローを学習する.                             |

| CadenceArtist/Composerr          | 東京大学  | 8/27    | 24   | 手書き回路設計および、そのシミュレーション制<br>御方法の習得                           |

| CadenceVirtuoso 講習会              | 東京大学  | 8/28-29 | 39   | LayoutEditorの使用方法,Pcell<br>(ParameterizedCell) の概念と作成方法の学習 |

| SynopsysHSIM講習会                  | 東京大学  | 9/1     | 9    | 高速SPICEシミュレータの使用方法の習得                                      |

| SynopsysChipSynthesis講習会         | 東京大学  | 9/3     | 17   | 論理合成ツールによる, 合成条件, 結果の解析, 階層設計を行う場合のストラテジなどを学習              |

| Synopsys,ICCompiler 講習会          | 東京大学  | 9/4-5   | 22   | 自動配置配線コアツールICCompilerのデザイン<br>フローと各フェーズでの機能の習得             |

| CadenceRTLCompiler講習会            | 東京大学  | 9/8     | 5    | 論理合成ツールによる, 合成条件, 結果の解析, 階層設計を行う場合のストラテジなどを学習              |

| CadenceSoCEncounter講習会           | 東京大学  | 9/9-10  | 9    | 自動配置配線ツールSoCEncounterのデザインフローと各フェーズでの機能の習得                 |

| AgilentGoldenGate 講習会            | 東京大学  | 9/11-12 | 10   | GoldenGateの基本的な使用法と、能動回路の設計<br>に必要な知識の学習.                  |

| CadenceSoCEncounter講習会           | 名古屋大学 | 3/2-3   | 4    | 自動配置配線ツール SoCEncounter のデザインフローと各フェーズでの機能の習得               |

| CadenceNC-Sim 講習会                | 東京大学  | 3/4-5   | 7    | コンパイル型 Verilog シミュレータの使用方法の習得                              |

| SynopsysVCS/SystemVerilog<br>講習会 | オンライン | 3/6     | 33   | SystemVerilogの使用方法の習得.                                     |

| SynopsysChipSynthesis講習会         | 東京大学  | 3/10    | 20   | 論理合成ツールによる, 合成条件, 結果の解析, 階層設計を行う場合のストラテジなどを学習              |

| CadenceAssura講習会                 | 広島大学  | 3/12-13 | 24   | 配線RC抽出ツールの使い方を学習する.                                        |

| ASIPSolution,ASIPMeister 講習会     | 大阪大学  | 3/16-17 | 15   | 特定用途向き命令セットプロセッサ開発環境<br>ASIPMeister について学習する.              |

| SynopsysStar-RCXT講習会             | 東京大学  | 3/24    | 10   | 配線RC抽出の概念の学習とツールの使用方法を<br>学習                               |

| Synopsys,ICCompiler 講習会          | 東京大学  | 3/25-26 | 17   | 自動配置配線コアツールICCompilerのデザイン<br>フローと各フェーズでの機能の習得             |

方からの参加者も多い. これは CAD 技術セミナーに対する需要が依然として大きなことを表しており、 VDEC はこの状況に対応し、大規模な CAD 技術セミナー開催の仕組みの整備を行ってきた. また、昨年は夏・春ともに東大での集中開催としてが、従来型に戻して夏は東大、春は東大と地方拠点での開催とした.

さらに、この3月の講習会からオンライン講習の導入 や、Webストリーミングによる遠隔受講の実験なども 行っている。

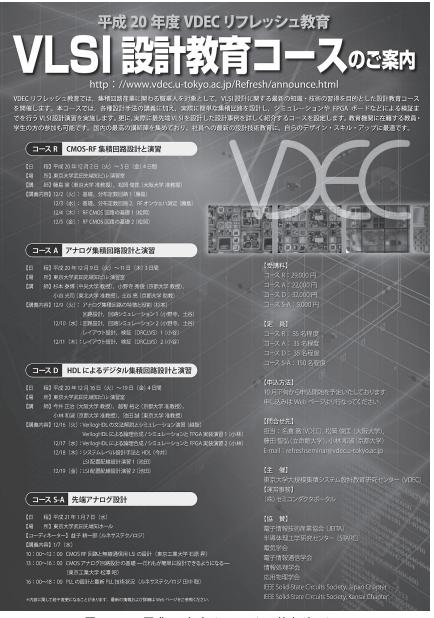

平成20年度12月~1月には平成18年度に引き続き,集積回路産業に携わる職業人を対象にリフレッシュ教育としてVLSI設計に関する最新かつ高度の知識・技術の習得を目的として、社会人向けの「VLSI設計リフレッシュセミナー」を拠点大学教官および企業の第一線の設計者を講師に招き開催した(表1.4.2).

このセミナーは主に社会人を対象として、演習を伴う 最新の VLSI 設計技術の実践的教育を行うもので、平成 10 年度に文部省専門教育課の支援のもとでスタートし たが、今年度は(財)電気電子情報振興財団の協力(共催) を得、また文部省高等教育局専門教育課、日本電子機械 協会(EIAJ)、システム LSI 開発支援センター(VSAC)、 半導体理工学研究センター(STARC)、日本応用物理学 会、情報処理学会、電気学会、電子情報通信学会の協賛 をあわせて得ることができ、大変効果的で有意義なセミナーとなった。

本年度は VLSI 設計に関する 4 つのコース (コース R: CMOS-RF 集積回路設計と演習 ( $12/2 \sim 12/5$  実施), コース A: アナログ集積回路設計と演習 ( $12/9 \sim 12/11$  実施) コース D: HDL によるディジタル集積回路設計と演習 ( $12/16 \sim 12/19$  実施), コース S: 最先端 VLSI 設計実

【社会人のためのリフレッシュセミナー】

図 1.4.2 平成 20 年度リフレッシュ教育ポスター

例 (1/7) を開催し、講師として大学・企業の集積回路研究・教育に携わる教官や研究者 19 名を招聘し、VLSI設計に関する講義や最新の CAD ツールを使用した実習

をはじめ、最先端の VLSI 設計技術の紹介を行った. 参加者はコース R,A,D,S はそれぞれ 20 名, 37 名, 20 名, 31 名あり、延べ 108 名となった.

図 1.4.3 平成 20 年度リフレッシュ教育会場風景(東大 VDEC セミナー室)

#### 表 1.4.2 リフレッシュセミナー開催状況

| 講習項目                                  | 開催日                          | 参加人数 | 講師                                                           | 講習概要                                                                                                                         |

|---------------------------------------|------------------------------|------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| コースR:<br>CMOS-RF集積回<br>路設計と演習         | 平成20年12月2-5日<br>先端知1Fセミナー室   | 20   | 松岡俊匡(大阪大学),<br>藤島実(東京大学)                                     | <ul><li>●基礎,分布定数回路</li><li>● RFCMOS回路の基礎</li><li>● RFオンウェハ測定</li><li>● RFオンウェハ測定実習</li></ul>                                 |

| コースD:<br>HDLによるディジ<br>タル集積回路設計<br>と演習 | 平成20年12月16-19日<br>先端知1Fセミナー室 | 20   | 今井正治 (大阪大学),<br>越智裕之 (広島市立大学),<br>小林和淑 (京都大学),<br>池田誠 (東京大学) | ● VerilogHDLの文法解説とシミュレーション演習<br>● VerilogHDLによる論理合成/シミュレーションと FPGA 実装演習<br>● ハードウェア記述言語(HDL)による、ディジタル集積回路設計<br>● LSI配置配線設計演習 |

| コースA:<br>アナログ集積回路<br>設計と演習            | 平成20年12月9-11日<br>先端知1Fセミナー室  | 37   | 杉本泰博 (中央大学),<br>小野寺秀俊 (京都大学),<br>小谷光司 (東北大学)                 | <ul><li>●回路設計,回路シミュレーション</li><li>●アナログ集積回路の特徴と役割</li><li>●レイアウト設計,検証(DRC,LVS)</li></ul>                                      |

| コースS:<br>最先端 VLSI 設計<br>実例            | 平成21年1月7日<br>先端知1Fセミナー室      | 31   | 益子耕一郎(STARC),<br>石原昇(東京工業大),<br>松澤昭(東京工業大学),<br>田中聡(日立製作所)   | ●先端アナログ設計 - CMOSRF回路と無線通信用LSIの設計 - CMOSアナログ回路設計の基礎―だれもが簡単に設計できるようになる― - PLL設計の基礎                                             |

13

#### 【若手教官・学生のためのデザイナーズフォーラム】

学生および若手教官を対象とした VDECLSI デザイナーフォーラム(VDECLSIDesignersForum)を開催している。 VDECLSI デザイナーフォーラムは、LSI 設計者が、互いの研究成果だけではなく、チップ設計で苦労した点、失敗事例と解決策、CAD 業界の裏話、研究

室に於ける設計環境の構築法など,通常の研究会や学会などでは得ることのできない情報を共有し,大学または研究室の枠を越えて研究者が連携を深めることを目的としている。今年からはよりアカデミック色を強めた形で6/6,7,8日にかけて東大武田ホールで開催された.107人の参加者が集まる盛況であった.

#### 表 1.4.3 平成 20 年度デザイナーズフォーラムプログラム

| 6/6 | 13:00-13:10 | 開会の挨拶                                                         | 浅田邦博 先生<br>(東京大学 VDEC) |

|-----|-------------|---------------------------------------------------------------|------------------------|

|     | 13:00-18:30 | VDECデザイナーズフォーラム特別講演                                           | 名倉 徹(東京大学 准教授)         |

|     | 13:10-14:50 | 大学の研究・企業の研究                                                   | 福間雅夫(NEC執行役員)          |

|     | 15:00-16:40 | チャネルエンジニアリングによる高性能CMOSデバイス技術                                  | 高木信一(東京大学 教授)          |

|     | 16:50-18:30 | 微細トランジスタの特性ばらつき : 原因究明と対策                                     | 平本俊郎(東京大学 教授)          |

|     | 19:00-22:00 | 懇親会&ポスターセッション                                                 |                        |

|     | 22:00-22:30 | 会場移動                                                          |                        |

|     | 22:30-23:00 | LSIのテストとVDECのテスト環境                                            | 小松 聡(東京大学 准教授)         |

|     | 23:30       | フリーディスカッション                                                   |                        |

| 6/7 | 10:00-12:00 | Ph.D企画セッション<br>「LSI分野における人に薦めたくなる博士課程」                        |                        |

|     | 13:00-13:30 | 3次元システム集積のための<br>低消費電力チップ間インターフェースの開発<br>~ ASSCC2007発表報告を交えて~ | 新津葵一 (慶応大)             |

|     | 13:30–14:00 | 技術の誕生から実用化まで携われた幸運<br>~須川研究室におけるイメージセンサ研究の事例を通じて~             | 赤羽奈々(東北大)              |

|     | 14:00-16:00 | ショート講演「私はこれで失敗した」10分×10人                                      |                        |

|     | 16:00-16:30 | VDECの活動紹介                                                     | 池田 誠(東京大学 准教授)         |

|     | 16:30-17:00 | 表彰式・閉会の挨拶                                                     |                        |

| 6/8 | 9:00-12:00  | VDECEDA 環境におけるデジタル回路設計手法                                      | 小林和淑(京都大学 准教授)         |

|     | 13:00-17:00 | VDECEDA 環境におけるトランジスタレベル回路設計手法                                 | 名倉 徹 (東京大学 准教授)        |

# 1.5 装置の整備・運用・利用公開

VDEC では、発足以来導入されてきた装置を維持管 理するとともに、全国大学教員に対し公開している(一 部装置は、試験公開中). 表 1.5.1 に装置の一覧と利用 公開の状況を示す. 装置は、VLSI 用大型テスターと、 その他若干のプロセス装置とに大別できる. VDEC 発 足以来,東京大学工学部各号館へ分散配置されてきたが, 平成16年度末までに「武田先端知ビル」内の1階実験 室ならびに地下スーパークリーンルームに装置の移設が 完了し、これまで以上に有機的な連携をもって利用する ことができるようになった。また、平成16年度に株式 会社アドバンテストより最新鋭のテスター (T2000) と 電子線描画装置 (F5112+VD01) とが寄附された. 電 子線描画装置の20年4月~21年1月の利用実績は、合 計 1333 回の描画(うちマスク 467 枚, 直接描画 866 回) であり、前年度より33%描画回数が増加.一昨年度よ り EB 描画装置は全国公開の準備が整い、同時に必要経 費の一部を競争的資金等から負担いただく仕組みが整備 された. さらに昨年度より文部科学省「ナノテクネット ワーク」に参加したことで、より多くのユーザーに対す る支援体制を整備しつつある.

平成9年度より各種治具の標準化に取り組んだ結果、 VDEC が推奨する標準ピン配置に基づき試作したデジ タル LSI は、治具をその都度作製することなく、VDEC および拠点校の LSI テスターにより評価が行える体制 が整っている. さらに. 今後新たな品種の試作が可能に なった場合においても、品種に応じたドーターボードを 1種類準備することで、全国の各大学における LSI テス ターに対応可能な体制が整っている. 今後、LSI テスト 法およびLSIテスター利用法のセミナーを頻繁に開催す ることで一層の利用の促進を図り、試作した LSI の特 性・性能評価が容易に行える環境の整備に努めたい. 試 作チップの評価に関しては、発足当初より QFP や BGA パッケージを実装できるソケットの頒布およびソケット のピンを標準 2.54 mm ピッチに変換する変換ボードを 開発してきた. WEB 経由の申し込みにより購入するこ とができる. 電子線描画装置, 集東イオンビーム加工装 置は、限られたスタッフのなかで、できるだけ多く利用 機会を設けたいという思想から、免許を持っている人間 から一定期間装置利用法を習得し、試験に合格したのち 利用資格を与える「徒弟免許制度」を考案し、試験運用 を行っている.

公開されている装置に関しては、セミナーの受講者に対して利用者資格を認定し、利用は、利用者資格を有する者もしくはその同伴の場合による利用を原則としている。必要に応じ、VDECの職員などが対応することで、利用を認める場合もあるので、個別に相談いただきたい。

表 1.5.1 装置一覧および利用公開状況

| 項目                     | 装置名                                     | 説明                                                                                                          | 利用公開状況        | 連絡先                              |

|------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------|----------------------------------|

| ロジック<br>LSIテスト<br>システム | ミックスシグ<br>ナルLSIテス<br>ター:<br>ITS 9000Exa | 100 MHz/200 MHz 320ピンのデジタルピンおよび4チャネルのアナログピンを有している. VDEC において標準ピン配置で試作したチップを測定するための治具を揃えている                  | 公開中           | ITS9000@<br>vdec.u-tokyo.ac.jp   |

|                        | EBテスター:<br>IDS5000ZX                    | 動作状態におけるチップ表面の電位を観測することで動作・不良解析を行う.通常LSIテスターと組み合わせて使用するため、上述テスターとのドッキング治具を備える384ピン、1 GHz までのデジタル回路のテストを行える. | 公開中           | IDS5000@<br>vdec.u-tokyo.ac.jp   |

|                        | LSIテスター:<br>HP8300                      | 384ピン, 1 GHz までのデジタル回路のテストを行える.                                                                             | 公開中           | HP83000@<br>vdec.u-tokyo.ac.jp   |

|                        | LSIテスター:<br>ADVANTEST<br>T2000          | 256ピン,512 MHzまでのデジタル回路のテストを行える。アナログオプションを整備中.                                                               | 試験公開中         | equipment@<br>vdec.u-tokyo.ac.jp |

|                        | 回路修正用<br>FIB:IDSP2X                     | LSIパターンの設計ミス等による配線ショート, オープンに対して, 配線の切断, 白金膜の生成によるジャンパーの生成が可能                                               | 公開中           | IDSP2X@<br>vdec.u-tokyo.ac.jp    |

|                        | オートプロー<br>バ : PM-90-A                   | ウエハ上でのLSIの動作検証を行うためのオートプローバ、上述のLSIテスターとドッキングして使用することが可能で、VDECにおいて標準ピン配置で試作したチップを測定するためのプローブカードを備えている        | 希望に応じ利<br>用可能 | equipment@<br>vdec.u-tokyo.ac.jp |

| アナログ・<br>RF測定<br>システム | アナログ・RF<br>測定装置一式:<br>HP4156B,<br>HP4284, etc       | DCパラメータ測定, 容量測定, ネットワークアナライザ, スペクトラムアナライザ等の測定装置                                           | 希望に応じ利<br>用可能. 但し<br>VDECの業務<br>による利用を | equipment@<br>vdec.u-tokyo.ac.jp |

|-----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|

|                       | 低雑音マニュ<br>アルプローバ:<br>Cascade 社                      | マニュアルにて6インチまでのウエハ上のチップの測定が可能. 測定には、通常のプローブ針(6本まで)のほか、50GHzまでの測定が可能な高周波プローブを2本備える          | 優先とする                                  |                                  |

|                       | 低雑音・温度<br>制御機構付き<br>セミオートプ<br>ローバ:Süss<br>Microtec社 | 8インチまでのウエハ上のチップの測定が可能. ウエハ温度を - 50℃から200℃まで制御可能. プローブカードによる測定. GPIBを介した制御を行うことで半自動測定も可能   |                                        |                                  |

|                       | 極低温プロー<br>バ:長瀬産業<br>株式会社                            | 5インチウエハを25 Kまで冷やした測定が可能                                                                   | 要相談                                    | equipment@<br>vdec.u-tokyo.ac.jp |

| 電子線描画システム             | マスク描画・ウ<br>エハ直描装置:<br>F5112+VD01                    | 半導体製造用 2.3 mm 厚 4.5 インチマスクの描画および<br>エッチング、2-4 インチ並びに不定形ウエハへの直接描<br>画が可能. 性能保障描画寸法 0.1 μm. | 公開中                                    | equipment@<br>vdec.u-tokyo.ac.jp |

| 汎用 FIB<br>システム        | FIB装置:<br>SMI9800MSP                                | ガラスマスクの欠陥修正の他, 断面観測のための加工<br>等が可能                                                         | 試験的に<br>公開中                            | equipment@<br>vdec.u-tokyo.ac.jp |

# 1.6 VDEC 利用者に関する発表文献リスト

#### 1. 研究論文

- [1] M. Sasaki, M. Ikeda and K. Asada, "A Temperature Sensor With an Inaccuracy of -1/+0.8°C Using 90-nm 1-V CMOS for Online Thermal Monitoring of VLSI Circuits," Semiconductor Manufacturing, IEEE Transactions, Vol. 21, Issue 2, pp. 201-208, May 2008.

- [2] R. K. Pokharel, H. Kanaya and K. Yoshida, "Design of 5 GHz-Band Power Amplifier with On-Chip Matching Circuits Using CPW Impedance (K) Inverters," IEICE Trans. On Electron., Vol. E91-C, No. 11, pp. 1824-1827, Nov. 2008.

- [3] 伊藤, 世渡, "Reducing Power Dissipation of Data Communications on LSI with Scheduling Exploration," IPSJ Trans. SLDM, Vol. 2, pp. 53-63, 2009.

- [4] Ueno K., Hirose T., Asai T., and Amemiya Y., "A 300-nW, 7-ppm/°C, 20-ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs," IEEE Journal of Solid-State Circuits, Vol. 44, (2009), in press.

- [5] H. Myoren, Y. Mada, Y. Matsui, T. Taino, and S. Takada, "Superconducting NbN Nanowire Photo Switches for Generating Single Flux Quantum Pulses," J. Phys. Conf. Ser., Vol. 97, 012329, pp. 1-6, 2008.

- [6] 加賀美智子, 鈴木史継, 浜本隆之, "被写体の明るさ分布に基づくダイナミックレンジ拡大と階調圧縮における重み付け処理の導入", 電子情報通信学会論文誌, A, Vol. J91-A, No. 6, pp. 651-653 (2008).

- [7] 原彰宏, 浜本隆之, "時間重心を合わせた適応蓄積時間イメージセンサ", 電子情報通信学会論文誌, D, Vol. J91-D, No. 8, pp. 2017-2019 (2008).

- [8] 土井俊輔, 浜本隆之, "広ダイナミックレンジ 撮像と動き検出を実現するスマートイメージセ ンサ", 電子情報通信学会論文誌, D, Vol. J91-D, No. 8, pp. 2020-2023 (2008).

- [9] Satoko Kagami, Fumitsugu Suzuki, Takayuki Hamamoto, "Wide Dynamic Range Image Sensor with Polygonal-line I/O Characteristic Adapted to Brightness Distribution of Objects", IEICE trans. on Electron, Vol. E91-C, No. 9, pp. 1402-1408 (2008).

- [10] Kawori TAKAKUBO, Hajime TAKAKUBO,

"Wide Range CMOS Voltage Detector with Low

Current Consumption and Low Temperature

Variation", pp. 443-450, IEICE TRANSACTIONS

on Fundamentals of Electronics, Communications

and Computer Sciences Vol. E92-A, No. 2.

- [11] Kawori TAKAKUBO, Toru ETO, Hajime TAKAKUBO, "Analysis and Modeling of Leakage Current for Four-Terminal MOSFET in Off-State and Low Leakage Switches", pp. 421-429, IEICE TRANSACTIONS on Fundamentals of Electronics, Communications and Computer Sciences Vol. E92-A No. 2.

- [12] Kazuteru Namba and Hideo Ito, "Test Compression for Robust Testable Path Delay Fault Testing Using Interleaving and Statistical Coding," IEICE Trans. Inf. & Syst., Vol. E92-D, No. 2, pp. 269-282, Feb., 2009.

- [13] Kentaroh Katoh, Kazuteru Namba and Hideo Ito, "Design for Delay Fault Testability of Dual Circuits Using Master and Slave Scan Paths," IEICE Trans. Inf. & Syst. Vol. E92-D, No. 3, Mar., 2009.

- [14] Kentaroh Katoh, Kazuteru Namba and Hideo Ito, "Design for Delay Fault Testability of 2-Rail Logic Circuits," IEICE Trans. Inf. & Syst., Vol. E92-D, No. 2, pp. 336-341, Feb., 2009.

- [15] Kentaroh Katoh, Kazuteru Namba and Hideo Ito, "Two-Stage Stuck-at Fault Test Data Compression Using Scan Flip-Flops with Delay Fault Testability," IPSJ Trans. Syst. LSI Des. Method, Vol. 1, pp. 91-103, Aug., 2008.

- [16] Yoichi Sasaki, Kazuteru Namba and Hideo Ito, "Circuit and Latch Capable of Masking Soft Errors with Schmitt Trigger," J. Electronic Testing! Theory & Appl. Vol. 24, No. 1-3, pp. 11-19, June, 2008.

- [17] T. Kumaki, M. Ishizaki, T. Koide, H. J. Mattausch, Y. Kuroda and T. Gyohten, H. Noda, K. Dosaka, K. Arimoto, and K. Saito, "Integration architecture of content addressable memory and massive-parallel memory-embedded SIMD matrix for versatile multimedia processor," IEICE Transactions on Electronics, Vol. E91-C, No. 9, pp. 1409-1418, (2008.9).

- [18] Farhad Mehdipour, Hamid Noori, Hiroaki Honda,

- Koji Inoue, and Kazuaki Murakami, "A gravity-directed temporal partitioning approach", IEICE Electronics Express, Vol. 5, No. 10, pp. 366-373, May 2008.

- [19] Hamid Noori, Farhad Mehdipour, Kazuaki Murakami, Koji Inoue, and Morteza Saheb Zamani, "An architecture framework for an adaptive extensible processor", The Journal of Supercomputing, Vol. 45, No. 3, pp. 313-340, Sep. 2008.

- [20] Hamid Noori, Farhad Mehdipour, Koji Inoue, and Kazuaki Murakami, "A Reconfigurable Functional Unit with Conditional Execution for Multi-Exit Custom Instructions", IEICE TRANSACTIONS on Electronics, Vol. 91-C, No. 4, pp. 497-508, Apr. 2008.

- [21] J.Akita, CMOS image sensor with pseudorandom pixel placement, IEICE Electronics Express, Vol. 5, No. 10, pp. 388-393, 2008.

- [22] Tsuchiya, Onodera, "Patterned Floating Dummy Fill for On-Chip Spiral Inductor Considering the Effect of Dummy Fill", pp. 3217-3222, IEEE Transactions on Microwave Theory and Techniques, vol 56, no 12 (2009).

- [23] Terada, Fukuoka, Tsuchiya, Onodera, "Accurate Estimation of the Worst-case Delay in Statistical Static Timing Analysis", pp. 116-125, IPSJ Transactions on System LSI Design Methodology, vol 1 (2008).

- [24] K. Nikawa, S. Inoue, T. Nagaishi, T. Matsumoto, K. Miura and K. Nakamae, "New approach of laser-SQUID microscopy to LSI failure analysis," IEICE Trans. Electronics, Vol. E85-C, No. 3, pp. 327-333, 2009.

- [25] M. Deura, T. Hoshii, T. Yamamoto, Y. Ikuhara, M. Takenaka, S. Takagi, Y. Nakano, and M. Sugiyama, "Dislocation-free InGaAs on Si (111) using microchannel selective-area metalorganic vapor phase epitaxy," Appl. Phys. Express., Vol. 2, 011101, 2009.

- [26] M. Deura, T. Hoshii, M. Takenaka, S. Takagi, Y. Nakano, and M. Sugiyama, "Effect of Ga content on crystal shape in micro-channel selective-area MOVPE of InGaAs on Si," J. Crystal Growths., Vol. 310, pp. 4768-4771, 2008.

- [27] K. Takeda, Y. Kanema, M. Takenaka, T. Tanemura, and Y. Nakano, "Polarization-insensitive all-optical flip-flop using tensile-strained multiple quantum

- wells," IEEE Photonics Technology Letters, Vol. 20, No. 22, pp. 1851-1853, 2008.

- [28] T. Hoshii, M. Deura, M. Sugiyama, R. Nakane, S. Sugahara, M. Takenaka, Y. Nakano, and S. Takagi, "Epitaxial lateral overgrowth of InGaAs on SiO<sub>2</sub> from (111) Si micro channel areas," Phys. Stat. Sol., Vol. C-5, No. 9, pp. 2733-2735, 2008.

- [29] T. Tanemura, M. Takenaka, A. Al Amin, K. Takeda, T. Shioda, M. Sugiyama, and Y. Nakano, "InP/InGaAsP integrated 1x5 optical switch using arrayed phase shifters," IEEE Photonics Technology Letters, Vol. 20, No. 12, pp. 1063-1065, 2008.

- [30] S. Dissanayake, Y. Shuto, S. Sugahara, M. Takenaka and S. Takagi, "(110) Ultra-thin GOI Layers Fabricated by Ge Condensation Method", Thin Solid Films, Vol. 517, No. 1, pp. 178-180, 2008.

- [31] Masanori HARIYAMA, Naoto YOKOYAMA, Michitaka KAMEYAMA, "Design of a Trinocular-Stereo-Vision VLSI Processor Based on Optimal Scheduling", IEICE Trans. Electron., Vol. E91-C, No. 4, pp. 479-486 (2008).

- [32] Hasitha Muthumala Waidyasooriya, Chong Wei Sheng, Masanori Hariyama, Michitaka Kameyama, "Multi-Context FPGA Using Fine-Grained Interconnection Blocks and Its CAD Environment", IEICE Trans. Electron., Vol. E91-C, No. 4, pp. 517-525 (2008).

- [33] Masanori Hariyama, Shota Ishihara, Michitaka Kameyama, "Evaluation of a Field-Programmable VLSI Based on an Asynchronous Bit-Serial Architecture", IEICE Trans. Electron., Vol. E91-C, No. 9, pp. 1419-1426 (2008).

- [34] Hasitha Muthumala WAIDYASOORIYA, Masanori HARIYAMA, Michitaka KAMEYAMA, "Evaluation of Interconnect-Complexity-Aware Low-Power VLSI Design Using Multiple Supply and Threshold Voltages", IEICE Trans. Fundamentals, Vol. E91-A, No12, pp. 3596-3606 (2008).

- [35] Nobuaki Okada, Michitaka Kameyama, "Fine-Grain Multiple-Valued Reconfigurable VLSI Using Series-Gating Differential-Pair Circuits and Its Evaluation". IEICE Trans. Electron., Vol. E91-C, No. 9, pp. 1437-1443 (2008).

- [36] Keishi Komoriyama, Makoto Yashiki,Eiichi Yoshida, Hiroshi Tanimoto; A VeryWideband Active RC Polyphase Filter with Minimum Element Value Spread Using Fully Balanced

- OTA Based on CMOS Inverters, IEICE Trans. Electronics, Vol. E91-C, No. 6, pp. 879-886, Jun. 2008.

- [37] T. Takeuchi, Y. Otake, M. Ichien, A. Gion, H. Kawaguchi, C. Ohta, and M. Yoshimoto, "Cross-Layer Design for Low-Power Wireless Sensor Node Using Wave Clock," IEICE Transactions on Communications, Vol. E91-B, No. 11, pp. 3480-3488, Nov. 2008.

- [38] Y. Murachi, J. Miyakoshi, M. Hamamoto, T. Iinuma, T. Ishihara, F. Yin, J. Lee, H. Kawaguchi, and M. Yoshimoto, "A sub 100 mW H.264 MP@ L4.1 Integer-pel Motion Estimation Processor Core for MBAFF Encoding with Reconfigurable Ring-connected Systolic Array and Segmentation-free, Rectangle-access Search-window Buffer," IEICE Trans. Electron., April 2008.

- [39] Y. Murachi, Y. Fukuyama, R. Yamamoto, J. Miyakoshi, H. Kawaguchi, H. Ishihara, M. Miyama, Y. Matsuda and M. Yoshimoto, "A VGA 30-fps Realtime Optical-Flow Processor Core for Moving Picture Recognition," IEICE Trans. Electron., April 2008.

- [40] H. Noguchi, Y. Iguchi, H. Fujiwara, S. Okumura, Y. Morita, K. Nii, H. Kawaguchi, and M. Yoshimoto, "A 10T Non-Precharge Two-Port SRAM Reducing Readout Power for Video Processing," IEICE Trans. Electron., Vol. E91-C, No. 4, pp. 543-552, April 2008.

- [41] H. Fujiwara, K. Nii, H. Noguchi, J. Miyakoshi, Y. Murachi, Y. Morita, H. Kawaguchi, and Masahiko Yoshimoto, "Novel Video Memory Reduces 45% of Bitline Power using Majority Logic and Data-Bit Reordering," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 16, No. 6, pp. 620-627, June 2008.

- [42] J. Wang, T. Ido, T. Matsuoka, and K. Taniguchi, "A novel approach to implement summing function for feedforward Δ - Σ AD modulator," IEICE Electronics Express, Vol. 5, No. 12, pp. 457-463, Jun. 2008.

- [43] J. Wang, T.-Y. Lee, D.-G. Kim, T. Matsuoka, and K. Taniguchi, "Design of A 0.5V Op-Amp Based on CMOS Inverter Using Floating Voltage Sources," IEICE Trans. Electron, Vol. E91-C, No. 8, pp. 1375-1378, Aug. 2008.

- [44] Y. Mizugaki and R. Kashiwa, "Magnetic Shielding Effect of Grounded Superconducting Niobium

- Layers," Journal of Physics! Conference Series, Vol. 97, 012056-1-5 (2008).

- [45] K. Ohhata, Y. Shimizu, and K. Yamashita, "Feedthrough Reduction Technique for Trackand-Hold Circuit with Body-Bias Control Circuit," IEICE Electron. Express, Vol. 5, No. 13, pp. 478-482.

- [46] 李,山下,大畠,"変調電流・バイアス電流同時 制御方式を適用したGbit/s帯光配線用VCSEL駆 動回路LSI",電子情報通信学会論文誌Vol. J91-C, No. 8, pp. 428-435, 2008/8.

- [47] Farhad Mehdipour, Hamid Noori, Hiroaki Honda, Koji Inoue, and Kazuaki Murakami, "A gravitydirected temporal partitioning approach", IEICE Electronics Express, Vol. 5, No. 10, pp. 366-373, May 2008.

- [48] Hamid Noori, Farhad Mehdipour, Kazuaki Murakami, Koji Inoue, and Morteza Saheb Zamani, "An architecture framework for an adaptive extensible processor". The Journal of Supercomputing, Vol. 45, No. 3, pp. 313-340, Sep. 2008.

- [49] Hamid Noori, Farhad Mehdipour, Koji Inoue, and Kazuaki Murakami, "A Reconfigurable Functional Unit with Conditional Execution for Multi-Exit Custom Instructions", IEICE TRANSACTIONS on Electronics, Vol. 91-C, No. 4, pp. 497-508, Apr. 2008.

- [50] 小林伸彰, 榎本忠義,「探索点を削減したA2BCS動きベクトル検出アルゴリズムとこれを適用したDVFS制御動きベクトル検出プロセッサの開発」, 信学総合大会講演論文集, 電子情報通信学会D-11-5, 2008年3月17日.

- [51] 榎本忠儀, 岩成武司, 小林伸彰, 「書き込みマージンを拡大した90-nm CMOS SRAMの開発, 信学ソ大会講演論文集, 電子情報通信学会 C-12-10, 2008年9月.

- [52] 小林伸彰, 石川雄悟, 榎本忠儀,「DVFS制御向 け動きベクトル検出アルゴリズムとこれを適用 した動きベクトル検出プロセッサの開発」, 信学 技報, IE2008-79, pp. 47-52, 2008年10月17日.

- [53] Tsuyoshi Sadakata and Yusuke Matsunaga, "A Behavioral Synthesis Method with Special Functional Units", IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, Vol. E91-A, No. 4, pp. 1084-1091, Apr. 2008.

- [54] M. Fukase, T. Sato, "Compact FPU Design

- and Embedding in a Ubiquitous Processor for Multimedia Performance Enhancement," ECTI Transaction on Electrical Engineering, Electronics and Communications, Vol. 6, No. 2, pp. 79-85, (2008).

- [55] Katsuki Kobayashi, Naofumi Takagi, "A Combined Circuit for Multiplication and Inversion in GF (2<sup>m</sup>)", pp. 1144-1148, IEEE Trans. on Circuits and Systems II, Vol. 55, No. 11, 2008.

- [56] Y. Murachi, Y. Fukuyama, R. Yamamoto, J. Miyakoshi, H. Kawaguchi, H. Ishihara, M. Miyama, Y. Matsuda, and M. Yoshimoto A VGA 30-fps Real time Optical-Flow Processor Core for Moving Picture Recognition, IEICE TRANS. ELECTRON., Vol. E91-C No. 4, pp. 457-464, (2008. 4).

- [57] M. Miyama, Y. Inoie, T. Kasuga, R. Inada, M. Nakao, and Y. Matsuda, A 158 MS/s JPEG 2000 Codec with a Bit-plane and Pass Parallel Embedded Block Coder for Low Delay Image Transmission, IEICE TRANSACTIONS on Fundamentals of Electronics, Communications and Computer Sciences Vol. E91-A No. 8 pp. 2025-2034, (2008.8).

- [58] K. Ichikawa, Y. Takahashi, Y. Sakurai, T. Tsuda, I. Iwase, M. Nagata, "Measurement-Based Analysis of Electromagnetic Immunity in LSI Circuit Operation," IEICE Transactions on Electronics, Vol. E91-C, No. 6, pp. 936-944, June 2008.

- [59] T. Yoshikawa, T. Ogino, M. Nagata, "Current-Mode Transceiver with Nonfeedback Clock Recovery Capability for Mobile Applications," IEICE Transactions on Electronics, Vol. E91-C, No. 9, pp. 1453-1462, Sept. 2008.

- [60] C. Zang, S. Imai, S. Frank and S. Kimura, "Issue Mechanism for Embedded Simultaneous Multithreading Processor," IEICE Trans. Fundamentals, Vol. E91-A, No. 4, pp. 1092-1100, April 2008.

- [61] 佐藤 寿倫, 国武 勇次, "ばらつき耐性を持つカナリアFFを利用したデザインマージン削減による省電力化", 情報処理学会論文誌, Vol. 49, No. 6, pp. 2029-2042, Jun. 2008.

- [62] 渡辺 慎吾, 橋本 昌宜, 佐藤 寿倫, "タイミング 歩留まり改善を目的とする演算カスケーディン グ", 情報処理学会論文誌 コンピューティングシ ステム(ACS), Vol. 1, No. 2, pp. 12-21, Aug. 2008.

- [63] Maziar Goudarzi, Tadayuki Matsumura, and

- Tohru Ishihara, "Way-Scaling to Reduce Power of Cache with Delay Variation", IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, Vol. E91-A, No. 12, pp. 3576-3584, Dec. 2008.

- [64] Yuriko Ishitobi, Tohru Ishihara, and Hiroto Yasuura, "Code and Data Placement for Embedded Processors with Scratchpad and Cache Memories", Journal of Signal Processing Systems, Nov. 2008.

- [65] A. Nakamura, M. Kawaharazaki, M. Yoshikawa, T. Fujino, "Regular Fabric of Via Programmable Logic Device using EXclusive-or Array (VPEX) for EB Direct Writing", pp. 509-516, IEICE TRANS. on Electronics Vol. E91-C, No. 4 (2008).

- [66] Ogawa T., Hirose T., Asai T., and Amemiya Y., "Threshold logic systems consisting of subthreshold CMOS circuits," IEICE Transactions on Fundamentals of Electronics and Computer, Vol. E92-A, No. 2, pp. 436-442 (2009).

- [67] Hirose T., Hagiwara A., Asai T., and Amemiya Y., "A highly sensitive thermosensing CMOS circuit based on self-biasing circuit technique," IEEJ Transactions on Electrical and Electronic Engineering, Vol. 4, No. 2, pp. 278-286 (2009).

- [68] Utagawa A., Asai T., Hirose T., and Amemiya Y., "Noise-induced synchronization among sub-RF CMOS analog oscillators for skew-free clock distribution," IEICE Transactions on Fundamentals of Electronics, Communications and Computer, Vol. E91-A, No. 9, pp. 2475-2481 (2008).

- [69] Hirose T., Asai T., and Amemiya Y., "Temperature-compensated CMOS current reference circuit for ultralow-power subthreshold LSIs," IEICE Electronics Express, Vol. 5, No. 6, pp. 204-210 (2008).

- [70] Yamada K., Asai T., Hirose T., and Amemiya Y., "On digital LSI circuits exploiting collisionbased fusion gates," International Journal of Unconventional Computing, Vol. 4, No. 1, pp. 45-59 (2008).

- [71] S. Kubota, M. Watanabe, "Programmable Optically Reconfigurable Gate Array Architecture and its writer," Applied Optics, Vol. 48, Iss.2, pp. 30208, 2009.

- [72] M. Watanabe, M. Nakajima, S. Kato, "An inversion/non-inversion dynamic optically reconfigurable gate array VLSI," World Scientific and

- Engineering Academy and Society Transactions on Circuits and Systems, Issue 1, Vol. 8, pp. 11-20, Jan., 2009.

- [73] N. Yamaguchi, M. Watanabe, "Liquid crystal holographic configurations for ORGAs," Applied Optics, Vol. 47, No. 28, pp. 4692-4700, Oct., 2008.

- [74] M. Watanabe, T. Shiki, F. Kobayashi, "Scaling prospect of optically differential reconfigurable gate array VLSIs," Analog Integrated Circuits and Signal Processing, Sep., 2008.

- [75] D. Seto, M. Watanabe, "A dynamic optically reconfigurable gate array perfect emulation," IEEE Journal of Quantum Electronics, Vol. 44, Issue 5, pp. 493-500, May, 2008.

- [76] Hideki Tamura, David C. Ng, Takashi Tokuda, Honda Naoki, Takuma Nakagawa, Taro Mizuno, Yumiko Hatanaka, Yasuyuki Ishikawa, Jun Ohta, Sadao Shiosaka, "One-chip sensing device (biomedical photonic LSI) enabled to assess hippocampal steep and gradual up-regulated proteolytic activities", Journal of Neuroscience Methods, 173, pp. 114-120 (2008).

- [77] T. Tokuda, R. Asano, S. Sugitani, M. Taniyama, Y. Terasawa, M. Nunoshita, K. Nakauchi, T. Fujikado, Y. Tano, J. Ohta, "Retinal stimulation on rabbit using CMOS-based multi-chip flexible stimulator toward retinal prosthesis", Jpn. J. Appl. Phys, 47 (2008) (accepted).

- [78] J. Ota, W. Narita, I. Ohta, T. Matsushita, and T. Kondo! "Fabrication of Periodically-Inverted AlGaAs Waveguides for Quasi-Phase-Matched Wavelength Conversion at 1.55 um," Jpn. J. Appl. Phys., 48 (4) (2009).

- [79] T. Matsushita, I. Ohta, and T. Kondo! "Quasi-Phase-Matched Parametric Fluorescence in a Periodically Inverted GaP Waveguide," Appl. Phys. Express, in press.

- [80] Shiho Hagiwara, Takumi Uezono, Takashi Sato, and Kazuya Masu, "Application of Correlationbased Regression Analysis for Improvement of Power Distribution Network", IEICE Transactions of fundamentals on Electronics, Communications and Computer Sciences, Vol. E91-A, No. 4, pp. 951-956, April, 2008.

- [81] Masanori Imai, Takashi Sato, Noriaki Nakayama, and Kazuya Masu, "An evaluation method of the number of Monte Carlo STA trials for statistical path delay analysis", IEICE Transactions on

- Fundamentals of Electronics, Communications and Computer Sciences, Vol. E91-A, No. 4, pp. 957-964, April, 2008.

- [82] Hiroyuki Ito, Makoto Kimura, Kazuya Miyashita, Takahiro Ishii, Kenichi Okada, Kazuya Masu, "A Bidirectional- and Multi-Drop-Transmission-Line Interconnect for Multipoint-to-Multipoint On-Chip Communications," IEEE Journal of Solid-State Circuits, Vol. 43, No. 4, pp. 1020-1029, April 2008.

- [83] N.Kamegai, S.Kishimoto, K.Maezawa, T.Mizutani, H.Andoh, K.Akamatsu, and H.Nakata, "Ultrashort Pulse Generators Using Resonant Tunneling Diodes and Their Integration with Antennas on Ceramic Substrates", Japanese Journal of Applied Physics, Vol. 47, No. 4, pp. 2833-2837 (2008).

- [84] K.Maezawa, I.Soga, S.Kishimoto, T.Mizutani and K.Akamatsu, "A GaAs SOI HEMT Fabricated by Fluidic Self-Assembly and Its Application to an RF-Switch", IEICE Trans. Electronics, Vol. E91-C pp. 1025-1030 (2008).

- [85] 鈴木,藤田,前中,"輸送環境モニタリングシステムとそのセンシング要素に関する研究",2008年度修士論文.

- [86] H.Yamauchi, "A 0.6 V Dual-Rail Compiler SRAM Design on 45 nm CMOS Technology With Adaptive SRAM Power for Lower VDD\_min VLSIs", IEEE Journal of Solid-State Circuits, Vol. 44, No. 4, April, 2009.

- [87] A. Ohchi, S. Kohara N. Togawa, M. Yanagisawa, and T. Ohtsuki, "Floorplan-Driven High-Level Synthesis for Distributed/Shared-Register Architectures," IPSJ Tras. on SLDM, Vol. 1, pp. 78-90, 2008.

- [88] Shingo Yoshizawa, Yoshikazu Miyanaga, "Use of a Variable Wordlength Technique in an OFDM Receiver to Reduce Energy Dissipation," IEEE Transactions on Circuit and Systems-I!Regular Paper, Vol. 55, No. 9, pp. 2848-2859, Oct. 2008.

- [89] Shingo Yoshizawa, Yasushi Yamauchi, Yoshikazu Miyanaga, "VLSI Implementation of a Complete Pipeline MMSE Detector for a 4x4 MIMO-OFDM Receiver," IEICE Transactions on Fundamentals, Vol. E91-A, No. 7, pp. 1757-1762, July 2008.

- [90] Masatomo Miura and Takahiro Hanyu, "Highly Reliable Multiple-Valued Current-Mode Comparator Based on Active-Load Dual-Rail Operation," IEICE Trans. Electron., Vol. E91-C, No. 4, pp. 589-594, April 2008.

- [91] Kazuyasu Mizusawa, Naoya Onizawa, and Takahiro Hanyu, "Power-Aware Asynchronous Peer-to-Peer Duplex Communication System Based on Multiple-Valued One-Phase Signaling," IEICE Trans. Electron., Vol. E91-C, No. 4, pp. 581-588, April 2008.

- [92] Shoun Matsunaga, Jun Hayakawa, Shoji Ikeda, Katsuya Miural, Haruhiro Hasegawa, Tetsuo Endoh, Hideo Ohno, and Takahiro Hanyu, "Fabrication of a Nonvolatile Full Adder Based on Logic-in-Memory Architecture Using Magnetic Tunnel Junctions," Applied Physics Express (APEX), pp. 091301-1 ~ 091301-3, Aug. 22, 2008.

- [93] Shoun Matsunaga, Kimiyuki Hiyama, Atsushi Matsumoto, Shoji Ikeda, Haruhiro Hasegawa, Katsuya Miura, Jun Hayakawa, Tetsuo Endoh, Hideo Ohno, and Takahiro Hanyu, "Standby-Power-Free Compact Ternary Content-Addressable Memory Cell Chip Using Magnetic Tunnel Junction Devices," Applied Physics Express (APEX), Vol. 2, No. 2, pp. 023004-1 ~ 023004-3, 2009.

- [94] 香川景一郎, 能勢悠吾, 安達雄大, 谷邦之, 和田淳, 谷田純, 布下正宏, 太田淳, "アクティブ・パッシブ方式画素読出しの併用によるCMOSイメージセンサのダイナミックレンジ拡大手法の提案と原理実証, "映像情報メディア学会誌, April 2009.

- [95] 吉川, "単一磁束量子回路を用いた超高速マイクロプロセッサの開発とその展望, "電子情報通信学会論文誌 C, Vol. J91-C, 2008, pp. 183-193.

- [96] K. Nakamiya, N. Yoshikawa, A. Fujimaki, H. Terai, Y. Hashimoto, "Direct measurements of propagation delay of single-flux-quantum circuits by timeto-digital converters", IEICE Electronics Express, Vol. 5 (2008), No. 9, pp. 332-337.

- [97] H. Park, Y. Yamanashi, K. Taketomi, N. Yoshikawa, A. Fujimaki, N. Takagi, "Novel serial-parallel converter using SFQ logic circuits" Physica C, Vol. 468, September 2008, pp. 1977-1982.

- [98] T. Kumaki, M. Ishizaki, T. Koide, H. J. Mattausch, Y. Kuroda and T. Gyohten, H. Noda, K. Dosaka, K. Arimoto, and K. Saito, "Integration architecture of content addressable memory and massive-parallel memory-embedded SIMD matrix for versatile multimedia processor," IEICE Transactions on Electronics, Vol. E91-C, No. 9, pp. 1409-1418,

- (2008.9).

- [99] Yosuke Takahashi, Yukihide Kohira, Atsushi Takahashi. A Fast Clock Scheduling for Peak Power Reduction in LSI. IEICE Trans. Fundamentals, Vol. E91-A, No. 12, pp. 3803-3811, 2008.

- [100] 山崎, 小原, 戸川, 柳澤, 大附, "SIMD型プロセッサコアの面積/遅延見積り", pp. 3462-3481, 情報処理学会論文誌 (2008).

- [101] D. Levacq, M. Takamiya, and T. Sakurai, "Backgate Bias Accelerator for sub-100 ns Sleep-to-Active Modes Transition Time," IEEE Journal of Solid-State Circuits, Vol. 43, No. 11, pp. 2390-2395, Nov. 2008.

- [102] Motoki Amagasaki, Ryoichi Yamaguchi, Masahiro Koga, Masahiro Iida and Toshinori Sueyoshi, "An Embedded Reconfigurable IP-Core with Variable Grain Logic Cell Architecture," International Journal of Reconfigurable Computing, Vol. 2008, Article ID 180216, 14 pages, doi!10.1155/2008/180216, Sep. 2008.

- [103] Y. Yoshida, N. Miura, and T. Kuroda, "A 2 Gb/s Bi-Directional Inter-Chip Data Transceiver With Differential Inductors for High Density Inductive Channel Array," IEEE Journal of Solid-State Circuit (JSSC), Vol. 43, No. 11, pp. 2363-2369, Nov. 2008.

- [104] Yusuke Niki, Yasuo Manzawa, Satoshi Kametani, and Tadashi Shibata, "Moving-Object-Localization Hardware Algorithm Employing OR-Amplification of Pixel Activities," Japanese Journal of Applied Physics. Vol. 47, No. 4, pp. 2767-2773, 2008.

- [105] Liem T. Nguyen, Kiyoto Ito, and Tadashi Shibata, "Compact and Power-Efficient Implementation of Rank-Order Filters Using Time-Domain Digital Computation Technique," Japanese Journal of Applied Physics. Vol. 47, No. 4, pp. 2807-2811, 2008.

- [106] Trong Tu Bui and Tadashi Shibata, "Compact Bell-Shaped Analog Matching-Cell Module for Digital-Memory-Based Associative Processors," Japanese Journal of Applied Physics. Vol. 47, No. 4, pp. 2788-2796, 2008.

- [107] Kenichiro Hirose, Yoshio Mita, Yoshiaki Imai, Frederic Marty, Tarik Bourouina, Kunihiro Asada, Shuichi Sakai, Tadashi Kawazoe and Motoichi Ohtsu, "Polarization transmissive photovoltaic film device consisting of Si photodiode wire-grid", J.

- Opt. A! Pure Appl. Opt. 10 044014 (2008.04).

- [108] Ryoichi Ohigashi, Katsunori Tsuchiya, Yoshio Mita, and Hiroyuki Fujita, "Electric Ejection of Viscous Inks From MEMS Capillary Array Head for Direct Drawing of Fine Patterns", Journal of Microelectromechanical Systems, Vol. 17, No. 2, pp. 272-277 (2008.04).

- [109] Yifan Li, Yoshio Mita, Leslie I. Haworth, William Parkes, Masanori Kubota, Anthony J. Walton, "Test Structure for Characterizing Low Voltage Coplanar EWOD System", IEEE Transactions on Semiconductor Manufacturing, IEEE Transactions, Vol. 22, No. 1, pp. 88-95 (2009.02).

- [110] Hongbo Zhu and Tadashi Shibata, "A Digital-Pixel-Sensor-Based Global Feature Extraction VLSI for Real-Time Object Recognition," Japanese Journal of Applied Physics. (Accepted for publication).

- [111] T. Kikkawa, P. K. Saha, N. Sasaki, and K. Kimoto, "Gaussian Monocycle Pulse Transmitter Using 0.18  $\mu$ m CMOS Technology With On-Chip Integrated Antennas for Inter-Chip UWB Communication", IEEE Journal of Solid-State Circuits, Vol. 43, No. 5 (2008) pp. 1303-1312.

- [112] N. Sasaki, K. Kimoto, W. Moriyama and T. Kikkawa, "A Single-Chip Ultra-Wideband Receiver With Silicon Integrated Antennas for Inter-Chip Wireless Interconnection", IEEE Journal of Solid-State Circuits, Vol. 44, No. 2 (2009), pp. 382-393.

- [113] Youhua Shi, Nozomu Togawa, Masao Yanagisawa, and Tatsuo Ohtsuki, A Unified Test Compression Technique for Scan Stimulus and Unknown Masking Data with No Test Loss, IEICE Trans. on Fundamentals of Electronics Communications and Computer Science, Vol. E91-A, No. 12, pp. 3514-3523, Dec. 2008.

- [114] JIANG Minglu, HUANG Zhangcai, KUROKAWA Atsushi, LI Na, INOUE Yasuaki, "An advanced effective capacitance model for calculating gate delay considering input waveform effect," Chinese Journal of Electronics (SCI), Vol. 17, No. 4, pp. 633-639, Oct. 2008.

- [115] K. Hamamoto, H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye, "An Efficiency and Speed Controllability," IEICE Trans. on Electronics, Vol. E92-C, No. 2, pp. 281-285, February 2009.

- [116] S. Abe, M. Hashimoto and T. Onoye, "Clock Skew Evaluation Considering Manufacturing Variability

- in Mesh-Style Clock Distribution," IEICE Trans. Fundamentals, Vol. E91-A, No. 12, pp. 3481-3487, Dec. 2008

- [117] M. Hashimoto, J. Siriporn, A. Tsuchiya, H. Zhu, and C.-K. Cheng, "Analytical Eye-Diagram Model for On-Chip Distortionless Transmission Lines and Its Application to Design Space Exploration," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, Vol. E91-A, No. 12, pp. 3474-3480, December 2008.

- [118] Y. Mitsuyama, K. Takahashi, R. Imai, M. Hashimoto, T. Onoye, and I. Shirakawa, "Area-Efficient Reconfigurable Architecture for Media Processing," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, Vol. E91-A, No. 12, pp. 3651-3662, December 2008.

- [119] 達可敏充、"ダイナミックスペクトルアクセスを用いたコグニティブ無線ネットワークにおけるノード位置推定手法の一検討", pp. 523-528, 2009.

- [120] 鈴木寛人,和田和千,田所嘉昭, "広範囲に分布 するディジタル回路で発生する基板雑音の打ち 消し回路, "信学論(A), Vol. J92-A, No. 4, 2009年 4月(掲載決定).

- [121] Sejoon Lee and Toshiro Hiramoto, "Strong dependence of tunneling transport properties on overdriving voltage for room-temperature-operating single electron/hole transistors formed with ultra narrow [100] silicon nanowire channel", Applied Physics Letters, Vol. 93, No. 4, 043508, July, 2008.

- [122] Jiezhi Chen, Takura Saraya, Kousuke Miyaji, Ken Shimizu, and Toshiro Hiramoto, "Electron Mobility in Silicon Gate-All-Around [100]-and [110]-Directed Nanowire Metal-Oxide-Semiconductor Field-Effect Transistor on (100)-Oriented Silicon-on-Insulator Substrate Extracted by Improved Split Capacitance-Voltage Method", Japanese Journal of Applied Physics, Vol. 48, No. 1, 011205, January, 2009.

- [123] Arifin Tamsir Putra, Akio Nishida, Shiro Kamohara, and Toshiro Hiramoto, "Random Threshold Voltage Variability Induced by Gate-Edge Fluctuations in Nanoscale Metal-Oxide-Semiconductor Field-Effect Transistors". Applied Physics Express, Vol. 2, No. 2, 024501, January, 2009.

- [124] Koji Kotani and Takashi Ito, "Self-Vth-Cancellation

- High-Efficiency CMOS Rectifier Circuit for UHF RFIDs," IEICE Transactions on Electronics, Vol. E92-C, No. 1, pp. 153-160, Jan. 2009.

- [125] Miwa, J., Suzuki, Y., and Kasagi, N., "Adhesion-based Cell Sorter with Amino-functionalized Parylene Surface," J. Microelectromech. Syst., Vol. 17, No. 3, (2008), pp. 611-622.

- [126] Sakane Y., Suzuki, Y., and Kasagi, N., "Development of High-performance Perfluorinated Polymer Electret and Its Application to Micro Power Generation," J. Micromech. Microeng., Vol. 18, No. 10, (2008), 104011, 6pp.

- [127] Kasagi, N., Suzuki, Y., and Fukagata, K., "MEMS-Based Feedback Control of Turbulence for Skin Friction Reduction," Annu. Rev. Fluid Mech., Vol. 41, (2009), pp. 231-251.

- [128] Kamijo, T., Suzuki, Y., Kasagi, N., and Okamasa, T., "High-temperature Micro Catalytic Combustor with Pd/Nano-porous Alumina," Proc. Comb. Inst., Vol. 32, Issue 2, (2009), pp. 3019-3026.

- [129] Fan, Y., Suzuki, Y., and Kasagi, "Experimental Study of Micro-scale Premixed Flame in Quartz Channels," Proc. Comb. Inst., Vol. 32, Issue 2, (2009), pp. 3083-3090.

- [130] 星野隆行, 森島圭祐, "メカノバイオニックツールの構築 骨格筋細胞による人工微小骨格の駆動実験—", 日本ロボット学会論文誌, Vol. 26, No. 6, pp. 651-657 (2008).

- [131] Koji Takeda, Yasuki Kanema, Mitsuru Takenaka, Takuo Tanemura, and Yoshiaki Nakano, "Polarization-Insensitive All-Optical Flip-Flop Using Tensile-Strained Multiple Quantum Wells", IEEE Photonics Technology Letters, pp. 1851-1853, Vol. 20, No. 22, November (2008).

- [132] 武田浩司, 竹中充, 種村拓夫, 中野義昭, 「分布ブラッグ反射鏡を用いた全光フリップ・フロップの波長可変特性」, 電子情報通信学会 信学技報, Vol. 108, No. 183, pp. 61-64 (フォトニックネットワーク研究会 PN2008-24) 2008年8月.

- [133] M. Deura, T. Hoshii, M. Takenaka, S. Takagi, Y. Nakano, and M. Sugiyama, "Effect of Ga content on crystal shape in micro-channel selective-area MOVPE of InGaAs on Si", Journal of Crystal Growth, Volume 310, Issue 23, pp. 4768-4771, November 2008.

- [134] M. Deura, T. Hoshii, T. Yamamoto, Y. Ikuhara, M. Takenaka, S. Takagi, Y. Nakano, and M. Sugiyama,

- "Dislocation-Free InGaAs on Si (111) Using Micro-Channel Selective-Area Metalorganic Vapor Phase Epitaxy", Applied Physics Express, Volume 2, No. 1, 011101-1-011101-3, January 2009.

- [135] T. Tanemura, M. Takenaka, A. Al Amin, K. Takeda, T. Shioda, M. Sugiyama, and Y. Nakano, "InP/ InGaAsP integrated 1x5 optical switch using arrayed phase shifters," pp. 1063-1065, IEEE Photon. Technol. Lett. (2008).

- [136] Jean-Jacques Delaunay, Ippei Nagatomo, Ryohei Uchino, Yanbo Li, Masaki Shuzo, Ichiro Yamada, "Enhancement of gas response of ZnO micro-nano structured layers through plasma treatment", Advanced Materials Research, vol.47-50, pp. 634-637, 2008.

- [137] Ezoe, Y, Koshiishi, M, Mita, M, Maeda, Y, Mitsuda, K, Osawa, T, Suzuki, M, Hoshino, A, Ishisaki, Y, Takano, T, Maeda, R, "Micromachined X-ray collector for space astronomy", SENSORS AND ACTUATORS A-PHYSICAL, 145, 201-206, (2008).

- [138] H. Yoshitake, Y. Ezoe, T. Yoshino, K. Mukai, K. Ishikawa, K. Mitsuda, N. Y. Yamasaki, Y. Ishisaki, H. Akamatsu, R. Maeda, T. Takano, "Optimization of Structure of Large Format TES array", IEEE Transactions on Applied Superconductivity (2009) in press.

- [139] Yoshino, T, Mukai, K, Ezoe, Y, Yamasaki, NY, Mitsuda, K, Kurabayashi, H, Ishisaki, Y, Takano, T, Maeda, R, "The noise and energy resolution of the Ti/Au bilayer X-ray TES calorimeter with an Au absorber", JOURNAL OF LOW TEMPERATURE PHYSICS, 151, 185-189, (2008).

- [140] H. Suzuki, K. Nagato, S. Sugimoto, K. Tsuchiya, T. Hamaguchi, M. Nakao, "Iterative imprint for multilayered nanostructures by feeding, vacuum forming and bonding of sheets", J. Vac. Sci. Technol. B 26 (2008) 1753.

- [141] M. Yokoyama, S. Ohya, and M. Tanaka, "Strong In-plane Uniaxial Magnetic Anisotropy of [ (InyGa1-y) 1-xMnx]As Characterized by Planar Hall Effect", Jpn. J. Appl. Phys. 48, 023001/1-4 (2009).

- [142] Pham Nam Hai, Shinobu Ohya, Masaaki Tanaka, Stewart E.Barnes, Sadamichi Maekawa, "Electromotive force and huge magnetoresistance in magnetic tunnel junctions" Nature 458, pp. 489-492 (2009).

- [143] S. Yada, M. Tanaka, and S. Sugahara "Magneto-optical and magneto-transport properties of amorphous ferromagnetic semiconductor Gel-xMnx thin films" Appl. Phys. Lett. 93, 193108/1-3 (2008).

- [144] Y. Shuto, M. Tanaka, and S. Sugahara "Epitaxial growth of ferromagnetic semiconductor Gel-xFex thin films on Si (001) substrates" Jpn. J. Appl. Phys. 47, pp. 7108-7112 (2008).

- [145] Nguyen Binh-Khiem, Kiyoshi Matsumoto, Isao Shimoyama, "Polymer Thin Film Deposited on Liquid for Varifocal Encapsulated Liquid Lenses," vol.93, no.12, art. no.124101, Applied Physics Letters (2008).

- [146] 南川, 佐藤, 森, Damayanthi, 高橋, 大野, "Simulation of Transient Response of Ir-TES for Position-Sensitive TES with Waveform Domain Multiplexing", Journal of Low Temperature Physics 151, pp. 155-160 (2008).

- [147] Damayanthi, 福田, 高橋, 大久保, 大野, "Design of an optical absorption cavity for titanium transition edge sensor", Journal of Low Temperature Physics 151, pp. 46-50 (2008).

- [148] Peng Huei Lim, Yosuke Kobayashi, Shinya Takita, Yasuhiko Ishikawa, and Kazumi Wada, "Enhanced photoluminescence from germanium-based ring resonators", Appl. Phys. Lett. 93, 041103, 2008.

- [149] Kotera, Abe, Egawa, Takizawa, Kobayashi, "Power-Aware Ddynamic Cache Partitioning for CMPs," Trans. on Embedded Architectures and Compilers, Vol. 3, pp149-167, (2008).

- [150] A. Chekhovskiy, Y. Ohira, and H. Toshiyoshi, "Laser Breakdown 3D Display," IEICE Trans. Electron., vol.E91, No. C (10), 2008, pp. 1616-1620.

- [151] 谷 雅直, 赤松雅洋, 安田喜昭, 藤田博之, 年吉洋, 「圧電MEMS光スキャナによる画像ディスプレィ」レーザー研究, 第36巻4号, pp. 183-189, 2008.

- [152] B Charlot, W Sun, K Yamashita, H Fujita and H Toshiyoshi, "Bistable nanowire for micromechanical memory," J. Micromech. Microeng. 18 045005 (7pp), 2008.

- [153] A.Chekhovskiy and H.Toshiyoshi, "A use of laser burst for volumetric imaging inside of transparent liquid," Japanese Journal of Applied Physics, vol.47, no.8 2008, pp. 6790-6793.

- [154] Cheng-Yao Lo, Hiroyuki Fujita, and Hiroshi

- Toshiyoshi, "Toward realization of transmissive display by MEMS etalon", IEICE ELEX, Vol. 5, No. 9, pp. 326-331 (2008).

- [155] Makoto Mita and Hiroshi Toshiyoshi, "An Equivalent-circuit Model for MEMS Electrostatic Actuator using Open-source Software Ques," IEICE Electronics Express, vol.6, no.5, 2009, pp. 256-263.

- [156] アレクサンダー・チェコフスキー, 大平康隆, 大塚由紀子, 平川一彦, 年吉 洋, 「液中でのレーザ励起プラズマによる3次元カラー画像表示器」生産研究 vol.60, no.3, 2008, pp. 123-126.

- [157] B Charlot, W Sun, K Yamashita, H Fujita and H Toshiyoshi, "Bistable nanowire for micromechanical memory", Journal of Micromechanics and Microengineering, Vol. 18, No. 4, 045005 (7pp) (2008).

- [158] Ryoichi Ohigashi, Katsunori Tsuchiya, Yoshio Mita, and Hiroyuki Fujita, "Electric Ejection of Viscous Inks From MEMS Capillary Array Head for Direct Drawing of Fine Patterns", Journal of Microelectromechanical Systems, Vol. 17, No. 2, pp. 272-277 (2008).

- [159] 谷雅直, 赤松雅洋, 安田喜昭, 藤田博之, 年吉洋, "圧電MEMS光スキャナによる画像ディスプレイ", レーザー学会誌レーザー研究, Vol. 36, No. 4, pp. 183-189 (2008).

- [160] Hirofumi Miura, Junji Sone, Dominique Collard, Christophe Yamahata, Hiroyuki Fujita, "FEM Analysis of Mechanical Characteristics of Nano Tweezers with MemsOne (TM)", 電気学会論文誌, Eセンサ・マイクロマシン部門誌, Vol. 128, No. 5, pp. 252-256 (2008).

- [161] V.Senez, E.Lennon, S. Ostrovidov, T. Yamamoto, H.Fujita, Y. Sakai, and T. Fujii, "Integrated 3-D Silicon Electrodes for Electrochemical Sensing in Microfluidic Environments! Application to Single-Cell Characterization", IEE Sonsors Journal, Vol. 8, Nos.5&6, pp. 548-557 (2008).

- [162] Cheng-Yao Lo, Hiroyuki Fujita, and Hiroshi Toshiyoshi, "Toward realization of transmissive display by MEMS etalon", IEICE ELEX, Vol. 5, No. 9, pp. 326-331 (2008).

- [163] Christophe Yamahata, Dominique Collard, Bernard Legrand, Tetsuya Takekawa, Momoko Kumemura, Gen Hashiguchi, and Hiroyuki Fujita, "Silicon Nanotweezers With Subnanometer Resolution for the Micromanipulation of

- Biomolecules", Journal of Microelectromechanical Systems, Vol. 17, No. 3, pp. 623-631 (2008).

- [164] E. Sarajlic, C. Yamahata, M. Cordero, D. Collard, and H. Fujita, "HAREM: High Aspect Ratio Etching and Metallization for microsystems fabrication", Journal of Micromechanics and Microengineering, Vol. 18, No. 7, 075008 (8pp.) (2008).

- [165] Hideyuki F. Arata, Frederic Gillot, Takahiko Nojima, Teruo Fujii and Hiroyuki Fujita, "Millisecond denaturation dynamics of fluorescent proteins revealed by femtoliter container on microthermodevice", Lab on a Chip, Vol. 8, Issue 9, pp. 1436440 (2008).

- [166] R. Yokokawa, J. Miwa, M. C. Tarhan, H. Fujita, and M. Kasahara, "DNA molecule manipulation by motor proteins for its evaluation in single molecule level", Anal. Bioanal. Chem., Vol. 391, No. 8, pp. 2735-2743 (2008).

- [167] Liza Lam, Shouichi Sakakihara, Koji Ishizuka, Shoji Takeuchi, Hideyuki F. Arata, Hiroyuki Fujita and Hiroyuki Noji, "Loop-mediated isothermal amplification of a single DNA molecule in polyacrylamide gel-based microchamber", Biomedical Microdevices, Vol. 10, No. 4, pp. 539-546 (2008).

- [168] Hideyuki F. Arata, Momoko Kumemura, Naoyoshi Sakaki and Hiroyuki Fujita, "Towards single biomolecule handling and characterization by MEMS", Analytical and Bioanalytical Chemistry, Vol. 391, No. 7, pp. 2385-2393 (2008).

- [169] Dominique Collard, Shoji Takeuchi and Hiroyuki Fujita, "MEMS technology for nanobio research", Drug Discovery Today, Vol. 13, Issues 21-22, pp. 989-996 (2008).

- [170] Ersin Altintas, Karl F. Bohringer, and Hiroyuki Fujita, "Micromachined Linear Brownian Motor! Transportation of Nanobeads by Brownian Motion Using Three-Phase Dielectrophoretic Ratchet", Japanese Journal of Applied Physics, Vol. 47, No. 11, pp. 8673-8677 (2008).

- [171] Y.-A. Chapuisa, L. Zhoua, H. Fujita and Y. Hervea,

"MULTI-DOMAIN SIMULATION USING

VHDL-AMS FOR DISTRIBUTED MEMS IN

FUNCTIONAL ENVIRONMENT: CASE OF A 2-D

AIR-JET MICROMANIPULATOR", Sensors &

Actuators A. Physical, Vol. 148, Issue 1, pp. 224-238

(2008).

- [172] Ataka, M.; Legrand, B.; Buchaillot, L.; Collard, D.; Fujita, H., "Design, Fabrication, and Operation of Two-Dimensional Conveyance System With Ciliary Actuator Arrays", IEEE/ASME Transactions on Mechatronics, Vol. 14, Issue 1, pp. 119-125 (2009).

- [173] Tadashi Ishida, Yuuki Nakajima, Junji Endo, Dominique Collard and Hiroyuki Fujita, "Real-time transmission electron microscope observation of gold nanoclusters diffusing into silicon at room temperature", Nanotechnology, Vol. 20, No. 6, pp. 65705.1-6 (2009).

- [174] Tetsuhiko Iizuka, Naomichi Sakai and Hiroyuki Fujita, "Position Feedback Control using Magneto Impedance Sensors on Conveyor with Superconducting Magnetic Levitation", Sensors and Actuators A Physical, Vol. 150, Issue 1, pp. 110-115 (2009).

#### 2. 国際会議

- [1] M. Takamiya, K. Onizuka, and T. Sakurai, "3D-Structured On-Chip Buck Converter for Distributed Power Supply System in SiPs," IEEE International Conference on IC Design and Technology (ICICDT), Grenoble, France, pp. 33-36, June 2008.

- [2] L. Liu, Y. Miyamoto, Z. Zhou, K. Sakaida, J. Ryu, K. Ishida, M. Takamiya, and T. Sakurai, "A 100Mbps, 0.41mW, DC-960MHz Band Impulse UWB Transceiver in 90 nm CMOS," IEEE Symposium on VLSI Circuits, Honolulu, Hawaii, USA, pp. 118-119, June 2008.

- [3] T. Niiyama, P. Zhe, K. Ishida, M. Murakata, M. Takamiya, and T. Sakurai, "Increasing Minimum Operating Voltage (VDDmin) with Number of CMOS Logic Gates and Experimental Verification with up to 1Mega-Stage Ring Oscillators," International Symposium on Low Power Electronics and Design (ISLPED), Bangalore, India, pp. 117-122, Aug. 2008.

- [4] T. Niiyama, K. Ishida, M. Takamiya, and T. Sakurai, "Expected Vectorless Teacher-Student Swap (TSS) Test Method with Dual Power Supply Voltages for 0.3V Homogeneous Multi-core LSI's," IEEE Custom Integrated Circuits Conference (CICC), San Jose, USA, pp. 137-140, Sep. 2008.

- [5] K. Ishida, T. Yasufuku, S. Miyamoto, H. Nakai, M.

- Takamiya, T. Sakurai, and K. Takeuchi, "A 1.8V 30nJ Adaptive Program-Voltage (20V) Generator for 3D-Integrated NAND Flash SSD," IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, pp. 238-239, Feb. 2009.

- [6] K. Ishida, N. Masunaga, Z. Zhou, T. Yasufuku, T. Sekitani, U. Zschieschang, H. Klauk, M. Takamiya, T. Someya, and T. Sakurai, "A Stretchable EMI Measurement Sheet with 8 × 8 Coil Array, 2V Organic CMOS Decoder, and -70dBm EMI Detection Circuits in 0.18 um CMOS," IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, pp. 472-473, Feb. 2009.

- [7] Chihiro Kawabata, Yasuhiro Sugimoto, "A Current-mode DC-DC Converter using a Quadratic Slope Compensation Scheme", pp. 113-114, ASP-DAC (2008).

- [8] Tatsuya Ogino, Yasuhiro Sugimoto, "The Influence of Dummy Fills on an On-chip Spiral Inductor and theirOptimized Placement Scheme", J5-06, APMC 2008.

- [9] M. Ikeda, "Smart Image Sensors," University of Tokyo & INRIA & Ecole des Mines Paris & INRETS Joint Symposium on Electronics for Secure Life, Jul. 2008.

- [10] K. Asada, "Introduction to VDEC activities for design and Manufacturing in microelectronics," University of Tokyo & UC Santa Barbara Joint Workshop, Sept. 2008.

- [11] M. Ikeda, "Delay Variation Measurements on DCVSL Using Logic Tester," University of Tokyo & UC Santa Barbara Joint Workshop, Sept. 2008.

- [12] J. Kim, K. Ikai, T. Nakura, M. Ikeda, K. Asada, "Variation Tolerant Transceiver Design for System-on-Glass," in IEEE 34th European Solid-State Circuits Conference (ESSCIRC) Fringe, Sep. 2008.

- [13] M. Ikeda, "Self-synchronous architecture for margin aware operations against PVT variations," Shanghai Jiao Tong University & University of Tokyo Joint Symposium on Electronics, Information Technology, and Electrical Engineering, D-2, Oct. 2008.

- [14] S. Mandai, T. Monma, T. Nakura, M. Ikeda, and K. Asada, "Multi Functional Range Finder Employing a Dual Imager Core on a Single Chip",

- International SoC Design Conf. (ISOCC) 2008, pp. 89-92.

- [15] K. Ikai, J. Kim, M. Ikeda, and K. Asada, "Digital Integrated Circuit Design for System-on-Glass," Proceedings of International SoC Design Conference, pp. 172-175, Nov. 2008.

- [16] Y.K. Kim, M. Ikeda, and K. Asada, "Analysis on light attenuation through Multi-Metal-Layers for CMOS image sensors on System LSIs," International SoC Design Conference, No. 94, Nov. 2008.

- [17] K. Asada, "Nanotech-Net Project as an Academic-Industry Collaboration Platform," the 8th Taiwan-Japan Microelectronics Symposium 2008, 1-2, Dec. 2008.

- [18] M. Ikeda, "Self-Synchronous Architecture for Power Optimal Operations against PVT Variations," the 8th Taiwan-Japan Microelectronics Symposium 2008, 4-6, Dec. 2008.

- [19] K. Ikai, J. Kim, M. Ikeda, and K. Asada, "Circuit Design using Stripe-Shaped TFTs on Glass" Proceedings of IEEE Asia and South Pacific Design Automation Conference, pp. 105-106, Jan. 2009.

- [20] Kazunori SUZUKI, Takashi NAKADA, Masaki NAKANISHI, Shigeru YAMASHITA, Yasuhiko NAKASHIMA, "A Functional Unit with Small Variety of Highly Reliable Cells", 14th Pacific Rim International Symposium on Dependable Computing (PRDC'08), pp. 353-354, Dec. (2008).

- [21] Takashi Nakada, Yasuhiko Nakashima, Hajime Shimada, Kenji Kise, Toshiaki Kitamura, "OROCHI: A Multiple Instruction Set SMT Processor". First International Workshop on New Frontiers in High-performance and Hardware-aware Computing (HipHaC'08), pp. 1-8, Nov. (2008).

- [22] Akihito Ichiki, Takashi Nakada, Yasuhiko Nakashima, "A Hybrid Platform for Practical Evaluation of Processors", Coolchips-2008 (poster), Apr. (2008).

- [23] Kazuhiro Yoshimura, Takashi Nakada, Yasuhiko Nakashima: "A QoS Control Method for a Heterogeneous SMT Processor", Coolchips-2008 (poster), Apr. (2008).

- [24] H. Hatano, "SEU effects on static and clocked cascade voltage switch logic (CVSL) circuits", Proc. of the 8th European Workshop on Radiation

- Effects on Components and Systems, pp. 136-140, Jyvaskyla, Finland, 2008.

- [25] R. K. Pokharel, S. Sasaki, O. Nizhnik, H. Kanaya, and K. Yoshida, "Design of VCO Using On-Chip CPW Resonator for 5 GHz-Band Wireless Applications", 2008 Asia-Pacific Microwave Conference Proceedings, C1-06 (2008).

- [26] A Tomar, R Pokharel, H Kanaya, K Yoshida, "Design of Digitally Controlled LC Oscillator with Wide Tuning Range in 0.18 um TSMC CMOS Technology", 2008 Asia-Pacific Microwave Conference Proceedings, C5-07 (2008).

- [27] A. I. A. Galal, R. K. Pokharel, H. Kanaya, and K. Yoshida, "2008 Asia-Pacific Microwave Conference Proceedings, H6-05 (2008).

- [28] S. Ogawa, T. Tanigawa, and D. Adachi, "An interfaces based on switched-capacitor sample/hold circuit of differential capacitance transducers," Proc. of ITC-CSCC2008, pp. 353-356, July 2008.

- [29] I. Sakagami, M. Tahara, and M. Fujii, "Planar Four-Way Power Divider Using Impedance-Transforming Branch-Line Couplers," 2008 Asia-Pacific Microwave Conf., B1-04, Hong Kong and Macau, China (Dec. 2008).

- [30] Masashi Imai, Takashi Nanya, "A Design Method for 1-out-of-4 Encoded Low-Power Self-Timed Circuits using Standard Cell Libraries," Proc. ACSD08, pp. 21-26, Jun., (2008).

- [31] Masashi Imai, Takashi Nanya, "Performance Comparison between Self-timed Circuits and Synchronous Circuits Based on the Technology Roadmap of Semiconductors," Proc. DSN08 2nd Workshop on Dependable and Secure Nanocomputing, Supplemental Proceedings, pp. C23-C28, Jun., (2008).

- [32] Y. Suwaki, T. Matsumoto, S. Matsufuji, "Experimental Evaluation of Optical ZCZ-CDMA System," Proc. of The 23rd International Technical Conference on Circuits/Systems, Computers and Communications, pp. 1809-1812 (2008).

- [33] T. Matsumoto, S. Matsufuji, "Matched Filter Implementation on FPGA for Integrand Code Using a Real-Valued Shift-Orthogonal Finite-Length Sequence, Proc. of the 11th International Conference on Advanced Communication Technology, pp. 179-183 (2009).

- [34] H. Myoren, and T. Taino, "Preparation of Submicron-wide Microstrip Lines for SFQ Circuits,"

- Proceedings of Superconducting SFQ VLSI Workshop SSV 2008, Yokohama, March 17, 2008, pp. 13-14.

- [35] H. Myoren, Y. Yoshizawa, T. Taino, and S. Takada, "SFQ Multiplexed Signal Processing Circuits for Superconducting Tunnel Junction Photon Detector Arrays," on 2008 Applied Superconductor Conference (2008 ASC), Chicago, August 20, 3EPE09.

- [36] Satoko Kagami, Fumitsugu Suzuki, and Takayuki Hamamoto, "Implementation and Evaluation of Wide-dynamic-range Image Sensor Adapted to Brightness Distribution of Objects", Int. Workshop on Image Media Quality and its Applications (IMQA'08), B-4, pp. 40-44 (2008).

- [37] Kenichi Nakayama, Atsunori Shikino, Takayuki Hamamoto, Kazuya Kodama, "3D motion estimation of imaging device using on-sensor motion detection". Int. Topical Meeting on Information photonics, P3-7, pp. 174-175 (2008).

- [38] K. Suzuki, T. Nakada, M. Nakanishi, S. Yamashita, and Y. Nakashima, "A Functional Unit with Small Variety of Highly Reliable Cells," Proc. of 14th Pacific Rim International Symposium on Dependable Computing (PRDC'08), pp. 353-354, December 2008.

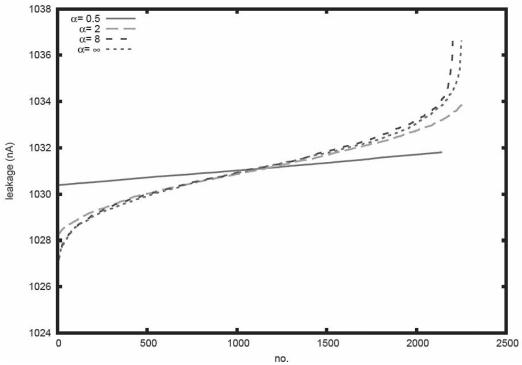

- [39] G. Fey, S. Komatsu, Y. Furukawa, M. Fujita, "Targeting Leakage Constraints during ATPG", 5th IEEE International Workshop on Silicon Debug and Diagnosis (SDD08), 2008.

- [40] S. Komatsu, "VLSI Test Exercise Courses for students in EE Department," IEEE International Test Conference, 2008.

- [41] G. Fey, S. Komatsu, Y. Furukawa, M. Fujita, "Targeting Leakage Constraints during ATPG," 17th Asian Test Symposium (ATS'08), pp. 225-230, 2008.

- [42] Shuangyu Ruan, Kazuteru Namba and Hideo Ito, "Soft Error Hardened FF Capable of Detecting Wide Error Pulse," Proc. 2008 IEEE Int. Symp. Defect and Fault Tolerance in VLSI Systems, pp. 272-280, 2008.

- [43] K. Okazaki, K. Awane, N. Nagaoka, T. Sugahara, T. Koide, and H. J. Mattausch, "Low-Power Image-Segmentation VLSI Design Based on a Pixel-Block Scanning Architecture", Extended Abstracts of the 2002 International Conference on Solid State Devices and Materials (SSDM2008), pp. 474-475,

(2008.9).

- [44] N. Nagaoka, K. Okazaki, T. Sugahara, T. Koide and H.J. Mattausch, "Grouping Method based on Feature Matching for Tracking and Recognition of Complex Objects," Proceedings of the 2008 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS2008), pp. 421-424, (2009.2).

- [45] K. Okazaki, N. Nagaoka, T. Sugahara, T. Koide and H.J. Mattausch, "Low Power and Area Efficient Image Segmentation VLSI Architecture Using 2-Dimensional Pixel-Block Scanning," Proceedings of the 2008International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS2008), pp. 441-444, (2009.2).