2018

**VLSI Design and Education Center, The University of Tokyo Annual Report**

# 東京大学 大規模集積システム設計教育研究センター

# 年 報

VLSI Design and Education Center The University of Tokyo 2018

# VLSI Design and Education Center The University of Tokyo

4月1日より、浅田前センター長の後任としてセンター長に就任いたしました、藤田昌宏です。大規模集積システム設計教育センター(VDEC)は、1996年5月にスタートし、22年が経過しています。初代センター長、鳳教授、ならびに2代目センター長、浅田教授のリーダーシップの基、VDECは日本のアカデミアにおける半導体チップとデバイス試作において、非常に大きなユーザ数を持つ、日本全体にとって欠かせない組織に発展してきていると考えています。VLSIチップ試作およびそのための設計ツールの提供に対しては、年間300の研究室に利用され、また各種デバイス試作のためのクリームルームや関連施設・設備は、年間200近くの研究室に利用されるようになっています。

半導体産業は世界全体として継続的に成長しており、これからも IoT 関連など、持続的な成長が予想されています。その土台となるアカデミアの研究開発を支援することは、極めて大きな責務であり、VDECの重要性はますます大きくなっています。海外にもVDECのような組織は米国、カナダ、ヨーロッパ、韓国、台湾などに、地域によっては複数あり、VDECと同様の使命を担っています。これらの組織間で毎年定例の会議を開催しており、お互いにアイデアを出しながら、VLSIチップやデバイス試作に関するユーザへのサービス提供に関し、世界レベルでの協調を進めており、今後より密な連携作業が進められる予定です。

また、寄付研究部門 D2T も設立から10年近くたち、海外から多数の客員教員が滞在し、教育・研究の両面で大きなインパクトを与えています。広い意味でのテストと設計をキーワードとした多くの研究が立ち上げられ、研究成果が生まれ、その産業界での利用も進んでいます。今後、VLSIチップとデバイス試作の両面に関連して、さらに活動を活発化する予定です。

VDEC はこれまで大きく発展して来ていますが、今後は、従来のチップやデバイスの試作の範囲を超えて、情報系のリソースも取り込んだ、電子機器システム全体の研究開発の支援へと発展できればと考えています。そのためには、より大規模なチップ試作の効率化、商用利用も考慮した設計ツールの提供、VLSIチップ試作とデバイス試作の統合化などにも取り組んでいきたいと思っています。これからもご支援をよろしくお願いいたします。

(全国共同利用施設) 東京大学大規模集積システム設計教育研究センター センター長 藤 田 昌 宏

藤四昌宏

# 巻頭言

| 第1章                 | VDEC 事業の紹介と平成 29 年度事業報告 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 1.1 VDEC 事業の紹介と平成 29 年度事業報告 ······ <b>2</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 1.2 CAD ソフトウェアの整備 ······ <b>5</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | 1.3 VLSI チップ試作 ······ <b>6</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | 1.4 セミナー 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     | 1.5 装置の整備・運用・利用公開 ······ <b>13</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     | 1.6 平成 30 年度の活動計画 ······ 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 1.7 VDEC 発ベンチャー ······ <b>17</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | 1.8 超微細リソグラフィー・ナノ計測拠点 ······ <b>18</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 第2章                 | 「アドバンテスト D2T 寄附研究部門」活動報告                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>第4</b> 早         | 7 I TO 7 TO I DO BY INCOME STATE OF THE STAT |

|                     | 2.1 「アドバンテスト D2T 寄附研究部門」の紹介 ······ <b>19</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

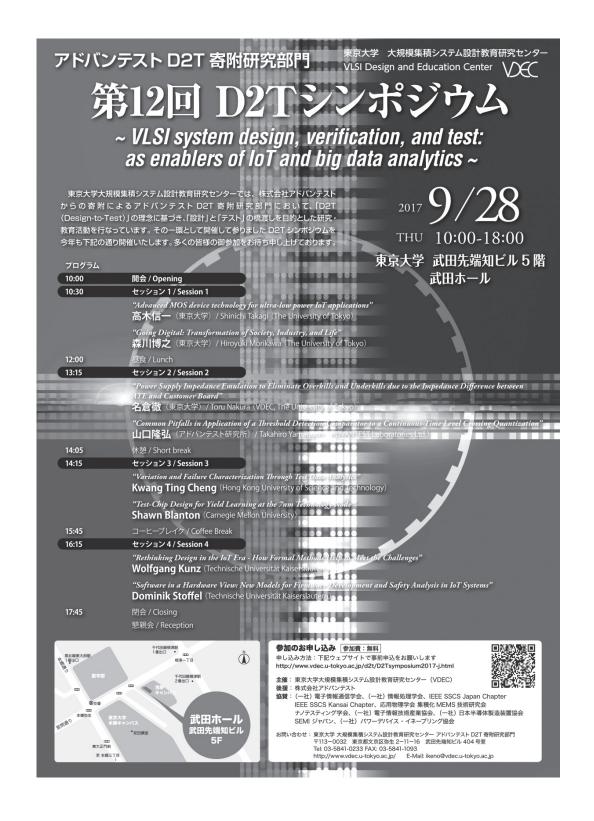

|                     | 2.2 「第 12 回 D2T シンポジウム」 開催報告 ······ <b>20</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | 2.3 研究活動報告 ······ <b>22</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 2.4 研究発表 ······ <b>23</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

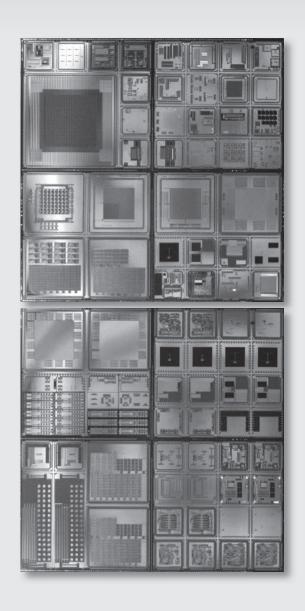

| 第3章                 | チップ試作結果報告                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | 3.1 試作ラン別一覧 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | 3.2 チップ種別一覧 ······ <b>31</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     | 3.3 各チップの詳細 <b>35</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 313 E 7 7 7 97 E 1 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>牲 / 主</b>        | VDEC 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>新</b> 4 早        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | 4.1 組織概要 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 4.2 人事報告 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 4.3 新任・退任のご挨拶 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | 4.4 決算報告 ····· <b>87</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 笙5音                 | 研究報告 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| N1 0 4              | 5.1 全体概況 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 5.1 至[[本成元 ····· ] <b>60</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     | 5.3 研究概要 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 5.4 研究発表 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | 5.5 特許,受賞等112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | J.J. 何町, 又貝守 ······ 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ppendix <sup></sup> | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     | A. Publication list ····· 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | B. VDEC の利用規定・申し込みガイド ······ <b>169</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

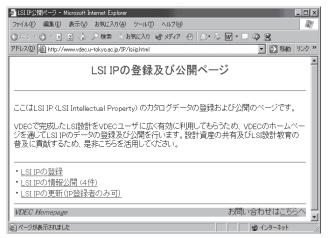

C. IP データベースの整備 ····· *172*

# 第 1 章 VDEC 事業の紹介と平成 29 年度事業報告

# 1.1 VDEC 事業の紹介と平成 29 年度事業報告

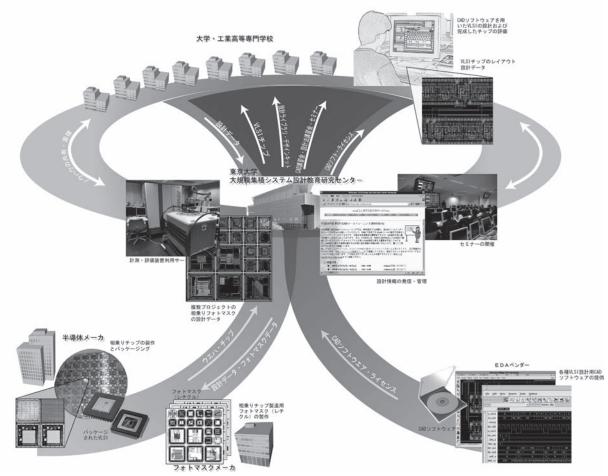

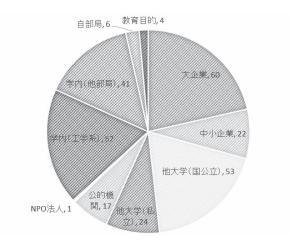

東京大学大規模集積システム設計教育研究センター (VDEC)は、平成8年の発足以来『LSI教育情報の発信拠点形成』、『VLSI設計支援教育用CADソフトウエアの整備』、『VLSIチップ試作支援』を3つの柱として、円滑な運営を目指した事業を展開した。図1.1に示すVDECの活動内容に基づき、以下に平成29年度の概要を報告する.

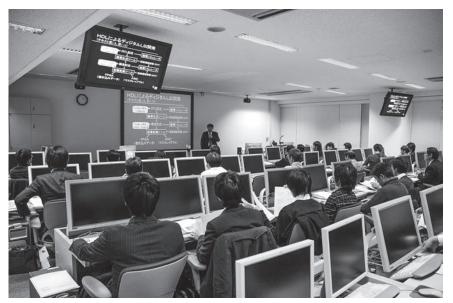

VDECの使命は全国の国公私立大学および高専のLSI設計研究・教育を高度化し、産業界に対しても優秀なLSI設計技術者を数多く送り出すことである。VDECの発足より22年経過し、各大学におけるCADソフトウエアの利用技術教育やLSI設計・設計フローに関する教育の充実が図られている。その一方で、先端のLSI設計技術およびそれに対応するCADソフトウエアは一層複雑化し続けている。そのため、CADツールの導入に際しては、CADベンダーから講師を招いてのセミナーの開催を継続しており、参加者の利便を図るために平成21年度より東京での開催と同時に映像配信による拠点校での遠隔受講としている。VDECとしては各ユーザ研

究室内で"技術伝承"され、VDEC 主催のセミナーがトリガーとなって最新の CAD 利用技術が全国的に広がることを期待している(1.3 章参照). また、各社のツールチェインが複雑化し導入しているツールを十分に使いこなすことが困難となっているという現状を鑑み、各ツールベンダーの推奨するツールチェインに関する講演会もツールセミナーの開催に合わせる形で実施した.

LSI 設計フローセミナーは LSI 設計の基本概念教育と 複数の CAD ツールを連携する実用的設計例の体験教育 である. この目的で VDEC では社会人のリフレッシュ教育プログラムと兼ねて LSI 設計教育セミナーを開催してきた. 平成 29 年度は,7月~9月に,"アナログ設計コース", "RF 設計コース", 平成 24 年から開始した" MEMS 設計コース"を実施した. いずれも演習を伴う体験教育コースであり, 主要大学の経験豊かな教官を講師に招いて実施している. 加えて各プロセスに特化した設計フローに関するセミナー" VDEC 環境におけるトランジスタレベル設計講習会", "VDEC EDA 環境におけるディジタルル設計手法講習会"を大学における設計者に向け

図 1.1 VDEC の活動内容

て実施している. なお, 平成26年度から本設計フロー に関するセミナーに関しても有料化して実施している.

これらセミナーに加えて VDEC では年1回、若手教 官と学生を中心とした VDEC デザイナー・フォーラム を開催している. これはワークショップ形式の会合で あり、企業・大学からの招待講演に交えて、参加者が 設計事例を持ち寄ってその成功談, 失敗談を交換する. これから設計を始めたいと考えている学生・教官もこ こでさまざまなノウハウを得ることができる. 特に平 成23年度から、VDEC活動における表彰として「IEEE SSCS Japan Chapter VDEC Design Award」の最終審 査・表彰を VDEC デザイナー・フォーラムの場で行っ ており、平成 29 年は、IEEE SSCS Japan Chapter VDEC Design Award として、神戸大学の浅野大樹さん、3件 の VDEC デザインアワード優秀賞, (浅野大樹(神戸大 学), 藤本光輝(奈良先端大), 松下悠亮(慶応大学)), 3 件の VDEC デザインアワード奨励賞(山口貴大(奈良先 端大), 速水一(奈良先端大), 孫鶴鳴(早稲田大学)), 3 件の VDEC デザインアワードアイデアコンテスト部門 嘱望賞(照月大悟(東京大学))を授与した.

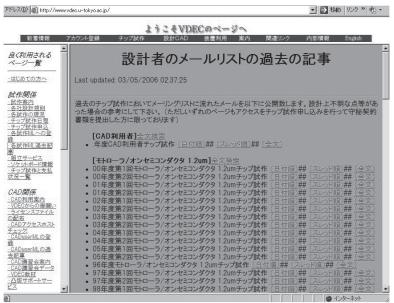

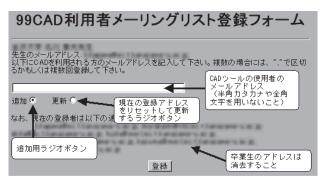

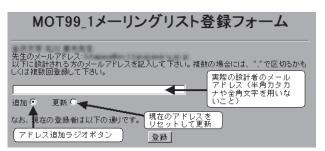

このようなセミナー、フォーラムを通じた教育システムにより LSI 設計の基本的項目を学習できるようになっているが、それでも実際の LSI 設計の場面では、さまざまな困難に直面することが多い。初心者にとっては CAD ソフトウエアのセットアップは最大の問題である。セットアップの後も CAD ソフトウエアが発する "難解なエラーメッセージ"でとまどうことも多い。このような場合に力を発揮するものが VDEC メールグループである。VDEC ユーザは VDEC のホームページから CADメールグループや試作技術対応のユーザグループに登録することができ、そこに直面する疑問点を投稿し、助けを求めることができる。メールグループの登録ユーザは

それに回答する義務を負っているわけではないが、ほとんどの場合、数時間から数日以内に経験豊かなユーザからの支援を得ることができる。また、今まで蓄積されてきたメールグループの情報が VDEC の WEB 上で認証された VDEC ユーザへ公開され、教育上の資産として残していく仕組みになっている。ぜひこの仕組みを活用することで問題解決の一助としていただきたい(図 1.2).

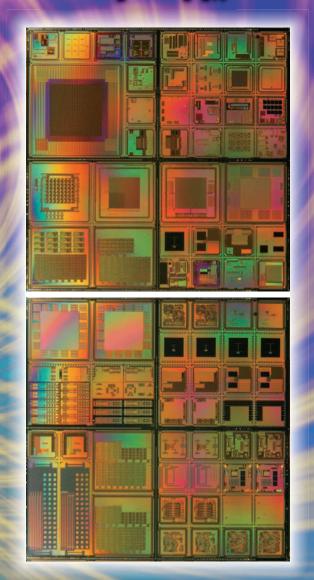

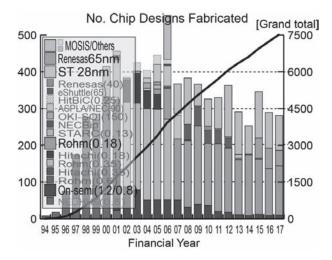

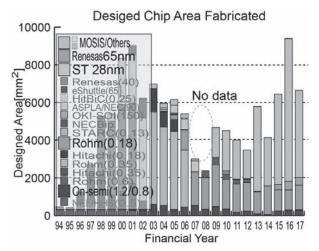

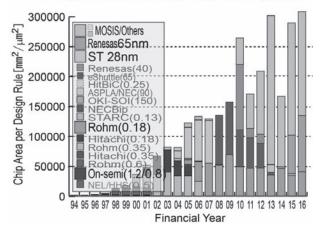

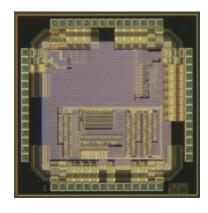

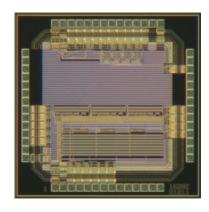

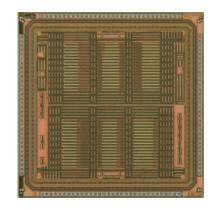

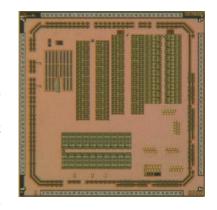

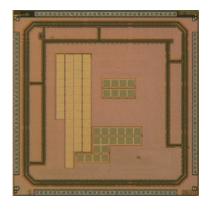

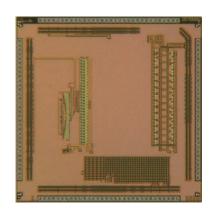

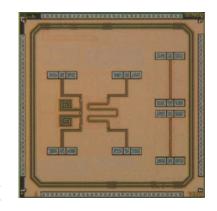

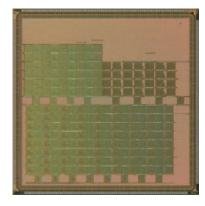

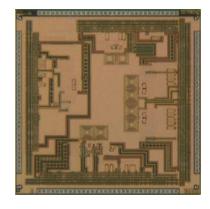

VLSI チップ試作支援に関しては、ルネサスエレクトロニクス社 SOTB 65 nm CMOS 試作を呈上試作として開始し、ローム  $0.18\,\mu$ m CMOS、オンセミ - 三洋半導体  $0.8\,\mu$ m CMOS 試作とともに実施した.

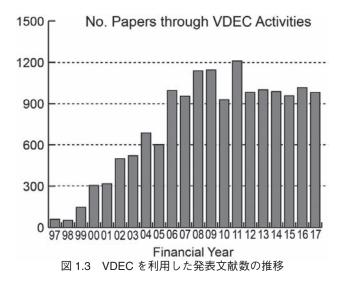

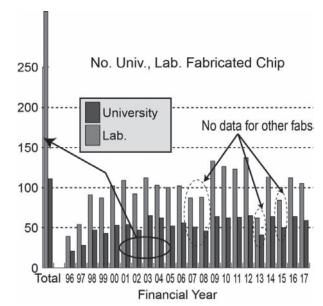

平成20年10月に設置されたアドバンテスト社から寄附部門「Design To Test (D2T)」では、LSIのテストに関する教育の充実とともに、設計とテストの架け橋を目指した研究が進められている。これまでの活動を振り返ると、VDEC発足以来の活動の中でLSI設計文化が根付いた研究室や大学ではすでに活発な設計研究・教育が進行している。図1.3にVDECを利用した研究成果の指標として、VDECに関係する発表文件数の推移を示す。単純に比較はできないが発表文献の数は増加傾向にあり、VDEC発足以来、集積回路に関係する研究が活性化されていることが確認できる。

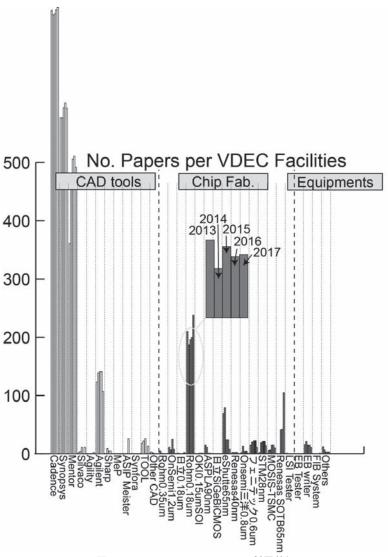

図 1.4 に VDEC に関係する発表文献の VDEC ファシリティー利用状況を示す. 論文執筆にあたり CAD ソフトウエアが幅広く利用されていることが確認できる. CAD ソフトウエアはチップ設計だけでなくチップ試作の準備段階で利用される場合が多いため、研究の基本アイデアを実証するツールとしての貢献度も大きい. また、研究論文には最先端のプロセステクノロジが好んで利用される傾向にあり世界的には 32 nm CMOS, 22 nm CMOS, 14 nm CMOS による設計事例報告が増加しており、VDEC においても最先端プロセステクノロジメ

図 1.2 VDEC メーリングリストの過去記事

ニューの充実をはかっていきたい. 加えて, More than Moore が叫ばれており, MEMS 混載 CMOS メニューなどの充実を図っていきたい. そのほかのファシリティー

として、LSIテスターや FIB 加工装置、EB 描画装置などが研究目的に幅広く利用されることを期待する.

図 1.4 VDEC ファシリティー利用状況

# 1.2 CAD ソフトウェアの整備

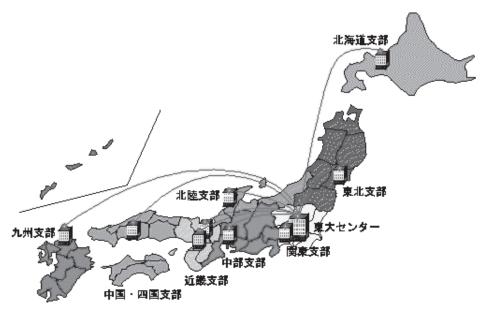

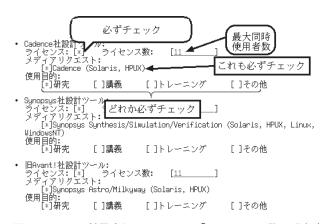

平成8年度から整備を行っているCADソフトウエアは、平成30年度は表1.2.1に示すツール群を全国の大学に提供している。CADソフトウエアの利用は、図1.2.1に示す全国地域拠点校10箇所にライセンスサーバを設置し、全国各大学の利用者が手許の計算機にインストールしたCADソフトウエアを、最寄のライセンスサーバにおいて認証を行うことで、ネットワークを利用した運

用形態となっている. ライセンス数は CAD の項目ごと に100から1000程度のフローティングライセンスとなっ ており、全国の国・公・私立大学・高専において教育・研究目的に限り利用できるようになっている.

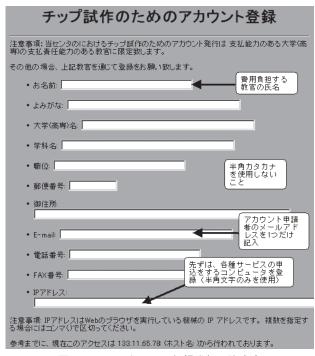

VDEC の CAD の利用、および「1.3章」のチップ試作の利用のためには、あらかじめユーザ登録が必要となっている。

表 1.2.1 導入された CAD システム

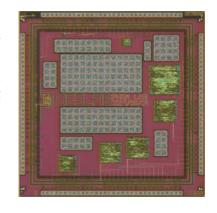

| 名称              | 用途                                                                                                                                       | メーカ                          |