Systems Design Lab

2023

Systems Design Lab, School of Engineering,

The University of Tokyo

Annual Report

ISSN 2436-6552

東京大学大学院工学系研究科 附属システムデザイン研究センター 先端設計研究部門・先端デバイス研究部門 (旧VDEC) 基盤設計研究部門・基盤デバイス研究部門

# 年 報

Systems Design Lab, School of Engineering

The University of Tokyo 2023

## Message from the Director of d.lab

東京大学大学院工学系研究科附属システムデザイン研究センター (d.lab)

## 黒田 忠広

Chris Miller氏が著した『CHIP WAR』が多くの人に読まれています。副題にThe fight for the world's most critical technology とあるように、国家間の攻防の歴史が克明に描かれています。

CHIP WAR は一面でしかない、別の未来も描ける。そう考えた私は、『半導体民主主義』という原稿を書きました。『半導体超進化論-世界を制する技術の未来-』とタイトルを変更して出版されています。

この本で描いた未来像は以下のとおりです.

◇◇◇◇◇◇◇ (あとがきより)

半導体民主主義と半導体戦争はコインの表裏である。私はこの本で半導体民主主義を描きたかった。

19世紀にビスマルクが「鉄は国家なり」と演説した。そして鉄は近代都市をつくり、兵器を生んだ。

現代では半導体の技術覇権が争われる.「半導体は国家なり」である. 半導体が何をつくりだし,何を破壊するのか. 私たちの創造力と知恵が試される.

チップメーカーは、次世代チップの生産をめぐって熾烈な争いを繰り広げている.

半導体戦争を煽るのではなく、チップネットワークを構築しなければならない。

技術はますます複雑化する。だから、木を見て森を見ずではいけない。森を育てること、つまり豊かな産業エコシステムをつくることが、これからの世界の課題である。

それを考えるうえでヒントとなったのが、植物だ

鮮やかに瑞々しく地球を覆いつくす植物. 今日の地球をつくりあげた大革命は、植物が「花」を持ったことで引き起こされた.

花と昆虫の間に「共生」関係が生まれ、互いが互いを進化させる進化の応酬である「共進化」が起こったのである。 花の誕生をきっかけに生き物たちの進化が一気に加速した。

ダーウィンが唱えた進化論では、生存に有利なものが生き残り子孫を残す。つまるところは、この世は競争。しかしながら、最新の科学で解明されようとしている生き物たちの隠された進化の仕組みは、競争するだけでなく互いを支え合う協力のルール、つまり「超進化論」である。

「半導体の森」を豊かにするためには、「花」を見つけることが大切であろう。 そう考えながら、本書では「半導体の超進化論」を説いた。

まずは、高性能な半導体をいかに製造するかを More Moore と More than Moore の観点で説明した.

次に、高性能な半導体で何を生み出すかをイノベーションの観点、すなわち More People の観点で考えた。

半導体を競争の時代から共生・共進化の時代に進めるために、半導体の「花」を見つけることができるだろうか。 半導体がグローバルコモンズになるためには、お金やムーアの法則以上のものが必要になる。

それは、多くの人を惹きつけること.

More Peopleだ.

$\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond$

1点、アジャイルについて、補足します.

やがて, 花は新しい能力を身につけた.

世代交代のスピードアップである. 受粉から受精までに要する時間を1年から数時間に縮めた. これがすべての生物の進化を加速したのだ.

$y = a (1+r)^n$

これは複利計算の式である。rが利率でnが運用回数。元本のaが小さくても長く運用すれば将来価値が大きくなる。nを1/tで置き換えれば,デジタル経済の基本式になる。tは開発のサイクルタイムである。この式は,チップの性能向上にも会社の成長にも当てはまる。

いいかえると、高速サイクルで改良を何度も繰り返すことが、デジタル経済の成長戦略である。改善率 (r) よりも改善回数 (n) を大きくすること、つまり開発のサイクルタイム (r) を短くすることが肝要である。

だからアジャイルなのだ.

$\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond\Diamond$

この本には、d.labの基本思想が記されています。お手にとってご覧いただけると幸いです。

黑田忠太

## NTENTS

| <b>巻頭言</b>                          |

|-------------------------------------|

| ご挨拶 ········1                       |

| <b>第1章 d.labの紹介</b> 4               |

| <b>第2章 d.lab 事業の紹介と2022年度事業報告</b> 5 |

| <b>2.1 先端設計研究部門</b> 5               |

| 2.2 先端デバイス研究部門10                    |

| 2.3 基盤設計研究部門11                      |

| 2.4 基盤デバイス研究部門14                    |

| 2.5 「アドバンテスト D2T 寄附講座」活動報告17        |

| <b>第3章 d.lab概要</b> 20               |

| 3.1 組織概要20                          |

| 3.2 人事報告21                          |

| 3.3 決算報告25                          |

| <b>第4章 研究報告 - 各研究室 -</b>            |

| 4.1 全体概況27                          |

| 4.2 研究室構成員(2022年度)28                |

| <b>4.3 研究概要······</b> 32            |

| <b>4.4 研究発表</b> 46                  |

| 4.5 特許,受賞等79                        |

| 付録(Appendix) 82                     |

| A. 旧VDEC事業関連·······82               |

| <b>A.1 CADソフトウェアの整備8</b> 2          |

| A.2 基盤設計研究部門におけるチップ試作支援の実施状況83      |

| A.3 セミナー86                          |

| A.4 VDEC発ベンチャー88                    |

| B. チップ試作結果報告·······89               |

| B.1 試作ラン別一覧·······90                |

| B.2 チップ種別一覧·······94                |

| B.3 各チップの詳細97                       |

| C. Publication list·······130       |

| D. VDECの利用規程・申し込みガイド·······161      |

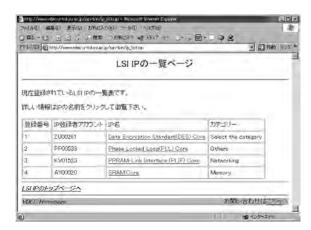

| <b>E. IP</b> データベースの整備·······166    |

## 第1章 d.labの紹介

1996年に大規模集積システム設計教育センター (VDEC) が設立されました. 当時は、日本の半導体が世界の半導体市場 (5兆円) の5割を占めており、即戦力となる人材が求められました. VDECは、世界に類のない卓越した教育を行い、優れた人材を半導体産業界に輩出してきました.

しかし、彼らはその才能を遺憾なく発揮できたでしょうか。この四半世紀の間に、世界の半導体産業は年率7%の高成長を遂げたにもかかわらず、日本の半導体は徐々にその地位を低下させ、現在のシェアは市場(50兆円)の1割程度に落ち込んでいます。

半導体ビジネスは、汎用チップを大量生産する薄利 多売のビジネスです。汎用チップが大量に売れる理由 は、コンピュータがメモリとプロセッサで構成できる フォン・ノイマン・アーキテクチャを採用しているか らです。日本はメモリデバイスのイノベーションで世 界をリードしましたが、ビジネスでは資本競争に敗れ ました。

大量生産・大量消費には、しかしながら限界があります。環境負荷が過大となり、世界はエネルギー危機に直面しています。ビッグデータをAIで分析するためには、さらに大きな電力が必要になります。

そこでついに、ゲームチェンジが起きました。半導

体メーカーから汎用チップを調達していたのでは競争 に勝てない、そう考えたGAFAなどの巨大IT企業が専 用ロジックチップの自社開発に乗り出したのです。

こうした時代のうねりの中で、東京大学は2019年の10月にシステムデザイン研究センター (d.lab) を開設し、11月にはTSMCと戦略的提携を結びました。d.labには、VDECと武田クリーンルームを運営する基盤設計研究部門と基盤デバイス研究部門に加えて、先端設計研究部門と先端デバイス研究部門が創設されました。2020年の10月からd.lab協賛事業を開始し、協賛会員は現在40社余りに増えています。

加えて、2020年の8月に先端システム技術研究組合 (RaaS) を設立して、産学官連携の体制を整えました. d.labと RaaSのオープン・クローズ戦略を両輪にして、学術・社会連携と産学協創を推進しています. 研究の目標は、半導体のタイムパフォーマンスを追究すること、すなわちエネルギー効率と開発効率を10倍高めることです.

日本は、工業・情報社会から人間中心の社会「Society5.0」を目指しています。知価社会において、半導体は産業のコメから社会の神経細胞へと進化します。

半導体戦略はどうあるべきでしょうか?その答えを 探すのがd.labのミッションです.

## 第2章 d.lab事業の紹介と2022年度事業報告

## 2.1 先端設計研究部門

## 2.1.1 先端設計研究部門の事業概要紹介

先端設計部門は,教授4名,准教授1名,講師1名,特任教授1名,上席研究員1名,特任研究員1名 (兼務含)で構成されており,エネルギー効率と設計効率の高い半導体集積回路の設計を目指しています。

2022年8月に国立研究開発法人新エネルギー・産業技術総合開発機構(以下「NEDO」)の「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発/研究開発項目④AIエッジコンピューティングの産業応用加速のための技術開発」の中で、「万能高位合成と新型汎用データフロー計算機構」を研究テーマとして、日本電気株式会社と東京大学とキヤノン株式会社が実施予定先として採択されました。本研究は2025年3月31日までの期間で行う予定であります。

各研究室での研究とは別に、組織として大きく2つの活動を行っています。1つ目は、d.lab協賛事業です。これはd.lab内の他部門の方々にもご協力いただいているものです。2つ目は、先端システム技術研究組合への参画です。本節では、これら2つの2022年度の活動について報告いたします。

## 2.1.2 d.lab協賛事業

システムデザイナーと半導体関連事業者が集い,情報・意見交換を行い,学術・社会連携をオープンに議論する 国際知価センター を目指して d.lab 協賛事業を2020年度に開設しました. IoT, AI, 5G,自動運転・制御,ヘルスケアなどのシステムデザイナーのアイデアと,先端CMOS や3D 集積などの先進半導体技術と,それを支える素材や製造装置を結びつけるハブを目指しています. 2022年度は,昨年度よりも6社増え,最終的に49社にご参加いただきました.表2.1.1が2022年度の協賛会員企業一覧です.参加いただいた各社の皆様にこの場であらためてお礼申し上げます.

2022年度は、コロナ禍の影響が幾分和らいだので、協賛事業設立時の構想にあったようにd.labの研究成果の報告にとどまらず、東京大学の著名教授や学生との交流、世界の大学や研究機関との交流、国際会議の情報提供、産業界のトップレベルの交流、TSMCなどの最先端技術の紹介や視察などを従来のWebinar形式の各種セミナーに加えたプログラムを構成できました。

以下2022年度の協賛事業の活動を報告いたします. 2022年度も5月から3月のほぼ1年間にわたり活動を行いました。表2.1.2に2022年度に開催したセミナーの一覧を示します.

2022年5月25日に2022年度第1回イベントとして, MITテクノロジレビュー受賞若手研究者による特別講 演及びキックオフ行いました. 2021年度 MIT Technology Review Innovators Under 35を受賞した3名の 若手研究者による次世代エレクトロニクス技術の講演 会を開催し、引き続いて2022年度の協賛事業の概要説 明をいたしました. 最初の登壇者は、モーションリブ 株式会社 CEO 溝口貴弘様です。感触や力加減を制 御するリアルハプティクス技術と、その中核となる半 導体チップABC-COREを開発されました。繊細な作業 が可能なロボットで人手不足の課題解決を支援する事 業についてご講演頂きました。2番目の登壇者は、東京 大学大学院工学系研究科 笹谷拓也特任助教です. 部 屋全体で充電できるワイヤレス充電技術を開発されま した. 「ケーブルのない」生活スタイルを実現に向け, ワイヤレス充電技術を中核とした応用技術の研究開発 についてご講演頂きました。3番目の登壇者は、東京大 学大学院附属システムデザイン研究センター 小菅敦 丈講師です。 超低消費電力のAIチップ技術を開発して おられます. 少子高齢化社会における労働力不足解消 に向け、工場や建設現場における自動化の普及・進化 を可能にする、AIセンシング技術について講演いただ きました。その後、d.labセンター長 黒田忠広教授よ り、22年度d.lab協賛事業の概要説明をさせていただき ました.

6月22日には、IBM dayと題し、2021年1月に引き続き、IBM Albanyの御紹介、及び IBM Quantum コンピュータに関するアップデートを行っていただきました。本イベントは、Web通常の配信とあわせて IBM 新川崎事業所(新川崎・創造のもり)で開催致しました。現地では講演の前後で量子コンピュータの実機の見学会を行っていただきました。また、ポスターセッションも合せて行いました。Albanyに関しては、IBM AI Hardware Centerで研究・開発している先進的AI Core、Chip、パッケージング、及びテスト環境の技術的アッ

プデート,及び参画方法の説明を,同社 山道新太郎様に行っていただきました.IBM Quantum コンピュータでは,技術,ロードマップ,また,ハードウェアを含めたエコシステム構築について,同社 中野大樹様,岩崎礼江様にご紹介いただきました.

7月20日には、2022 IEEE 72nd Electronic Components and Technology Conference (ECTC 2022) の報告会を行 いました. 本会議は, IEEE Electronics Packaging Society が主催するパッケージ, 部品, マイクロエレクトロニ クスシステムについての科学・技術について幅広く議 論する、今年で72回目の開催となる伝統のある世界有 数の国際会議です。今回は3年ぶりの現地開催となりま した. 技術プログラムは、パッケージング技術全般に わたる最先端の開発成果と革新技術をカバーし, 先端 パッケージング, モデリングとシミュレーション, フ ォトニクス, インターコネクション, 材料とプロセス, 信頼性, 製造技術, コンポーネントとRF, および新興 技術が主なトピックスとして構成されています。本報 告会では、現行事業の主流技術である先端パッケージ 技術と次世代のコア技術であるハイブリッドボンディ ング技術にフォーカスし, その技術動向とトピックス について報告しました.

8月25日には6/12~6/17に米国ホノルルにて開催され たVLSIシンポジウム (The 2022 IEEE VLSI Symposium on Technology & Circuits) の報告会を行いました. 本会 議は、1987年以来, IEEE Electron Device Society/Solid State Circuits Society と応用物理学会 (協賛:電子情報通 信学会)が主催する最先端の半導体デバイス・プロセ ス技術、半導体回路技術に関するマイクロエレクトロ ニクス業界のプレミア国際会議です。毎年、日米(京 都/ホノルル)交互で開催され、今年は米国開催とな りました。(コロナ禍の影響により今年は3年ぶりのリ アルイベント) 今年のテーマである「未来を担う不可 欠な社会基盤のためのVLSIテクノロジーと回路」に基 づいて、先端ロジックCMOS、メモリー、イメージセ ンサー,フォトニクス,機械学習, AI, デジタル,通 信、アナログなどの最先端技術のプログラムで構成さ れ、将来技術に対する開発・製造、人材育成の在り方 なども議論されています。報告会では、回路・通信シ ステム, AI・機械学習, 先端CMOS, メモリー, 3D集 積にフォーカスし, その技術動向とトピックスについ て報告しました。

10月26日には、昨年に引き続き、企業交流会を開催しました。皆様からのご要望に応え、今年度は武田先端知ビル5F 武田ホールでの現地開催が実現できまし

た. パネル展示を希望いただいた13社によるショートプレゼンテーションのあと、ホワイエにおいてポスター発表を行っていただきました。会員の皆さんに交流いただける場となり、主催者としてもうれしい限りのイベントでした。

11月29日には、TSMC 3DICセンター見学及び現地交 流会を行いました。TSMCジャパン3DIC研究開発セン ターは、Taiwan Semiconductor Manufacturing Company (TSMC) が、台湾の以外で初めて設立した研究開発拠 点です。昨年6月24日には政府要人等を含む来賓を招 いたオープニングセレモニーが行われました。3次元 (3D) 実装を含め、後工程の重要性が高まる中、日本 の材料/半導体製造装置メーカーや研究機関, 大学と 連携しながら最先端の3D IC実装の研究開発を行うこ とが目的と言われています. 同社のご厚意により, TSMCジャパン3DIC研究開発センターの見学会が実現 しました. 当日は、同センターのあるつくば中央駅に 近いつくば国際会議場において、同社の講演を聞いた 後,3班に分かれて同センターの見学を行いました。真 新しいクリーンルームの中にまで入れていただき最新 技術の説明を受けました.

先端半導体のさらなる高性能化の実現には、デバイスの微細化技術とチップレットに代表される先端パッケージング技術の両輪の進展が不可欠となっています。12月13日には、昨年に引き続き imec day と題し、imec からこれらの領域を牽引しておられる幹部をお招きして、世界最先端の3Dシステムインテグレーション技術についてご紹介いただきました。同技術で世界をリードする imec のお話を生で聴ける絶好の機会となりました。「Future CMOS device scaling by 3D architectures」と題し、imec Logic CMOS device program directorである、Naoto Horiguchi様にご講演いただくとともに、「3D Integration Technology: Enabling Heterogeneous System Scaling」と題して、imec Senior Fellow、VP R&D、Program Director 3D System Integrationである Eric Beyne様にご講演いただきました。

年が明けて2023年1月18日には、IEDM2022報告会を行いました。IEDM (International Electron Devices Meeting) はIEEEが主催するデバイス技術に関する世界最高峰の国際会議で、12月3日~7日にIn-personおよびOn-demandのハイブリッド形式で開催されました。IEDM会議全体概要の報告と先端CMOSデバイス技術・材料技術、不揮発メモリ技術、コンピューティング技術、3D集積技術にフォーカスした最新デバイス技術の動向についてd.lab教授陣が解説を行いました。

近年、ムーアの法則の限界が本格的に議論されるようになり、チップレットや3DIC半導体パッケージの開発が具体化してきました。半導体パッケージの集積度が高くなるに従い、適用される材料には高性能に加えて難度の高いプロセス適合性が要求されています。2月8日には、d.lab材料セミナーと題し、熱制御技術や最新のパッケージング技術とともに、d.labが描く材料戦略について紹介しました。東京大学生産技術研究所野村政宏教授には、「半導体の放熱で重要となる熱輸送の物理と熱流制御技術」を、株式会社レゾナック阿部秀則理事には、「新生レゾナックにおける共創型化学会社としての半導体材料開発の取組」をご講演いただきました。加えて、d.lab 山本和徳特任研究員より、「新d.lab の描く半導体パッケージ材料戦略」と題して講演させていただきました。

2022年度のセミナーシリーズは、3月15日の2023 International Solid-State Circuits Conference (ISSCC2023) の報告会で結びました。ISSCCは今年で70周年を迎えました。機械学習用プロセッサ技術がますます盛んに議論される一方で、アジア地域が強いイメージャ、メモリなども数多く発表されました。2月に開催された集積回路技術に関する最高峰の国際会議ISSCCから、今後の半導体産業を牽引するであろう集積回路技術の最新トレンドをISSCCの技術プログラム委員長などを歴任されてきた池田誠教授をはじめとするd.lab教授陣が解説しました。

2022年度の活動は、コロナ禍の状況を見極めつつ、 リモートセミナーとリアルイベントを織り交ぜた開催 としました。IBMやTSMCへの見学訪問など従来には なかったような企画も組み込みことができました。引 き続き2023年度も、会員と大学人、あるいは会員間の 知的交流を活性化できるイベントの企画を行っていき たいと考えています。

#### 2.1.3 先端システム技術研究組合

先端システム技術研究組合 (RaaS: Research Association for Advanced Systems) は2020年8月17日に開設されました。RaaSは、データ駆動型社会を支えるシステムに必要な専用チップのデザインプラットフォームを構築し、オープンアーキテクチャを展開することで、専用チップの開発効率を10倍高めることを目標に掲げています。さらに、3次元集積技術を研究開発し、最新の7nm CMOSテクノロジーで製造したチップを同一パッケージ内に積層実装することで、エネルギー効率を10倍高めることが目標です。

我々は半導体ビジネスの主役が、汎用チップから専用チップに再びスイングすると考えています。その背景にはデータ社会特有の「エネルギー危機」があります。データが急増し、AI処理が高度化して、エネルギー危機に拍車がかかっています。このままいくと、2030年には現在の総電力の倍近い電力をIT関連機器だけで消費し、2050年にはそれが約200倍になると予想されています。デジタルトランスフォーメーションに莫大なエネルギーを費やして地球環境を破壊することになるのなら、サステイナブルな未来は望めません。

こうした状況下では、エネルギー効率を10倍高めた者だけが、コンピュータを10倍高性能にでき、スマートフォンを10倍長く使えます。あらゆるタスクをこなせる汎用チップに比べて、無駄な回路をそぎ落とした専用チップはエネルギー効率を桁違いに改善できます。専用チップが求められる理由がここにあります。さらに、AI処理に用いられる神経回路網はデータを並列処理するので、逐次処理をするフォン・ノイマン・アーキテクチャでは性能を引き出せません。AIアクセラレータのための専用チップが世界中で開発されています。また、ムーアの法則が減速していることも専用チップの時代の追い風になっています。

ところが、専用チップの開発は誰にでも簡単にできるものではありません。チップに集積されるトランジスタ数は世界人口を超えようとしています。開発費は近年急増して100億円にも達する勢いです。数100人の設計者を配しても開発に数年を要します。技術進歩が早い現代においては全く間に合いません。

ソフトウェアは、バグがあっても後でパッチを当てて修復できます。しかし、ハードウェアは完璧に仕上げなければなりません。ハードウェアはソフトウェアより設計が難しくて開発リスクが高く、"hard"です。

もし、ソフトウェアの開発に用いられるコンパイラーのような技術がチップの開発にも用いられたならば、 すなわちシリコンコンパイラーができたならば、ハードウェアの開発費が下がりリスクも下がるでしょう。 ハードウェア設計者の人口も増えます。やがてオープンソースの文化が根付き、エコシステムのネットワークが重層的に拡大発展すれば、マスコラボレーションも可能になるでしょう。そうなれば、まさにソフトウェアを書くようにチップを作ることができます。

かつてアラン・ケイが「ソフトウェアを本気で考える人たちは、自分でハードウェアを作ることになる」と言いました。システム開発には、ハードウェアとソフトウェアの両方が必要です。

私たちの目標は、シリコン技術の民主化 (democratize access to silicon technology) です。シリコンコンパイラーをイノベーションし (design chips as writing software), 短時間でプロトタイプを作れる開発プラットフォームを創出します (agile authentic prototyping).

技術目標は、開発効率10倍かつエネルギー効率10倍です。開発効率を高めるために、アジャイル設計プラットフォームを創出し、オープンアーキテクチャを展開します。また、エネルギー効率を高めるために、チップを先端CMOS技術で製造し、3次元実装します。

半導体を製品として売るのではなく、サービスとして提供する。そのための技術をRaaS(ラース)は研究開発します。

RaaSは東京大学目白台インターナショナルビレッジ内に各組合員から研究員が集結し、互いに刺激しあいながら研究開発を遂行する計画でありましたが、コロナ禍においてはリモートワーク中心の活動形態をとっております。

2021年度には、国立研究開発法人新エネルギー・産業技術総合開発機構(以下「NEDO」という。)の、「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発(b)先端半導体の後工程技術(More than Moore技術)の開発」に係る公募にRaaSとして応募し採択されました。開発テーマは、「(b2)エッジコンピューティング向け実装技術」です。

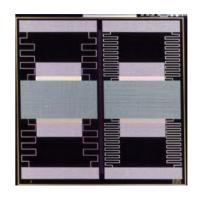

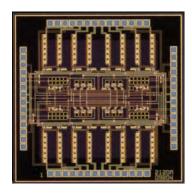

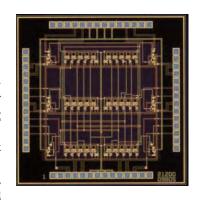

2022年度は、システム系研究開発においては、7nmプロセスでの試作したチップの評価を進め、RaaSとして東京大学と共著で複数の学会発表を行ったことが成果です。テクノロジー系研究開発においては、前述のNEDOプロジェクトを柱に、ダイレクト接合3D積層技術開発(WoWおよびCoW向け装置・プロセス開発)としてCu-Cu の低温ハイブリッド接合によるWoW(Wafer on Wafer)接合技術及びCoW(Chip on Wafer)接合技術の構築とその実装化に取り組んでおります。

| 表2.1.1 2022年度 d.lab 協賛会員(50音順)    |

|-----------------------------------|

| アオハ株式会社                           |

| 旭化成エレクトロニクス株式会社                   |

| 株式会社アドバンテスト                       |

| アナログ・デバイセズ株式会社                    |

| ウシオ電機株式会社                         |

| オルガノ株式会社                          |

| キオクシア株式会社                         |

| ギガフォトン株式会社                        |

| 株式会社神戸製鋼所                         |

| 株式会社コベルコ科研                        |

| 株式会社サムスン日本研究所                     |

| シーメンス EDA ジャパン株式会社                |

| JSR株式会社                           |

| 株式会社JCU                           |

| 信越化学工業株式会社                        |

|                                   |

| 株式会社SCREENホールディングス(RaaS)          |

| 住友商事株式会社                          |

| 株式会社ソシオネクスト                       |

| ソニーグループ株式会社                       |

| ダイキン工業株式会社(RaaS)                  |

| 大日本印刷株式会社                         |

| 株式会社ディスコ                          |

| 東京エレクトロン株式会社                      |

| 東京応化工業株式会社                        |

| 東洋紡株式会社                           |

| 東レ株式会社                            |

| 凸版印刷株式会社(RaaS)                    |

| 長瀬産業株式会社                          |

| 株式会社ニコン                           |

| 日本アイ・ビー・エム株式会社                    |

| 日本ケイデンス・デザイン・システムズ社               |

| 日本シノプシス合同会社                       |

| 日本電子株式会社                          |

| 株式会社ネクスティ エレクトロニクス                |

| パナソニック インダストリー株式会社                |

| パナソニック コネクト株式会社(RaaS)             |

| 株式会社半導体エネルギー研究所                   |

| 株式会社日立製作所(RaaS)                   |

| 富士通株式会社                           |

| 富士フイルム株式会社(RaaS)                  |

| マイクロンメモリジャパン株式会社                  |

| 三井化学株式会社                          |

| 三菱ケミカル株式会社                        |

|                                   |

| 三菱電機株式会社<br>株式会社ミライズテクノロジーズ(RaaS) |

|                                   |

| 株式会社村田製作所                         |

| ルネサスエレクトロニクス株式会社                  |

| 株式会社レゾナック                         |

ローム株式会社

表2.1.2 2022年度 d.lab 協賛事業セミナー

| 開催日        | タイトル                                  | 講師                                                                                                                                                                                                                       |  |  |

|------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2022/5/25  | MITテクノロジレビュー受賞若手研究者による特別講演<br>及びキックオフ | モーションリブ株式会社 CEO 溝口貴弘様<br>東京大学大学院工学系研究科 笹谷拓也特任助教<br>d.lab 小菅敦丈 講師<br>d.lab 黒田 忠広 教授                                                                                                                                       |  |  |

| 2022/6/22  | IBM day                               | IBM 中野 大樹 様<br>  IBM 岩崎 礼江 様<br>  IBM 山道 新太郎 様                                                                                                                                                                           |  |  |

| 2022/7/20  | ECTC 2022 報告会                         | d.lab 竹内 魁 特任研究員<br>d.lab 川野 連也 特任研究員<br>d.lab 丹羽 正昭 上席研究員<br>d.lab 高木 剛 主幹研究員                                                                                                                                           |  |  |

| 2022/8/25  | VLSI シンポジウム2022報告会                    | d.lab濱田 基嗣 特任教授 d.lab小菅 敦丈 講師 d.lab平本 俊郎 教授 d.lab高木 信一 教授 d.lab小林 正治 准教授 d.lab丹羽 正昭 上席研究員                                                                                                                                |  |  |

| 2022/10/26 | d.lab協賛企業交流会                          | d.lab 若林 一敏 上席研究員<br>株式会社アドバンテスト<br>株式会社神戸製鋼所<br>株式会社コベルコ科研<br>株式会社JCU<br>昭和電エマテリアルズ株式会社<br>大日本印刷株式会社<br>大日本印刷株式会社<br>株式会社ディスコ<br>東洋紡株式会社<br>東レ株式会社<br>株式会社ニコン<br>日本ケイデンス・デザイン・システムズ社<br>三菱ケミカル株式会社<br>ルネサス エレクトロニクス株式会社 |  |  |

| 2022/11/29 | TSMC 3DICセンター見学及び現地交流会                | d.lab 黒田 忠広 教授                                                                                                                                                                                                           |  |  |

| 2022/12/13 | imec day                              | imec Dr. Naoto Horiguchi<br>imec Dr. Eric Beyne                                                                                                                                                                          |  |  |

| 2023/1/18  | IEDM2022報告会                           | d.lab 平本 俊郎 教授 d.lab 高木 信一 教授 d.lab 小林 正治 准教授 d.lab 竹内 健 教授 d.lab 高木 剛 主幹研究員                                                                                                                                             |  |  |

| 2023/2/8   | d.lab材料セミナー                           | 東京大学生産技術研究所 野村 政宏 教授<br>株式会社レゾナック 阿部 秀則 理事<br>d.lab山本 和徳 特任研究員                                                                                                                                                           |  |  |

| 2023/3/15  | ISSCC2023報告会                          | d.lab 池田 誠 教授<br>d.lab 小菅 敦丈 講師<br>d.lab 濱田 基嗣 特任教授<br>d.lab 飯塚 哲也 准教授<br>d.lab 竹内 健 教授                                                                                                                                  |  |  |

## 2.2 先端デバイス研究部門

先端デバイス部門では、データ駆動型システムを実現するため半導体システムのエネルギー効率を10倍改善することを目指し、3次元集積技術と先端デバイス技術の研究を行っている.

#### 2.2.1 構成

| 教授    | 高木  | 信一        |       |

|-------|-----|-----------|-------|

| 教授    | 平本  | 俊郎        | (部門長) |

| 教授    | 染谷  | 隆夫        |       |

| 教授    | 内田  | 建         |       |

| 准教授   | 小林  | 正治        |       |

| 上席研究員 | 丹羽  | 正昭        |       |

| 主幹研究員 | 高木  | 剛         |       |

| 特任研究員 | 山本  | 和徳        |       |

| 特任研究員 | 最上  | 徹         |       |

| 特任研究員 | 川野  | 連也        |       |

| 特任研究員 | 二宮  | 健生        |       |

| 特任研究員 | 王 俊 | <b>建沙</b> |       |

|       |     |           |       |

## 2.2.2 事業報告

データ駆動型社会の実現を目指して、エネルギー効率10倍を可能とする次世代3D集積技術のコアとなるプロジェクトを行っている。AIをはじめ大量のデータ処理を必要とするコンピューティング技術において、メ

モリとプロセッサとの間の大量で頻繁なデータ移動に伴うエネルギー消費が大きな課題となっている。そのような課題を解決する技術として、チップレベルもしくはウェハレベルで直接接合を形成して、データの移動距離を短縮しエネルギー効率を高めるダイレクト接合3D積層技術に注目し研究を行っている。

2021年度に採択されたNEDO事業「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発(助成)」において、d.labが組合本部となり運営している3D集積技術に関する技術研究組合である先端システム技術研究組合(Research Association for Advanced Systems: RaaS)が、『ダイレクト接合3D積層技術開発(WoWおよびCoW向け装置・プロセス開発)』というテーマにRaaS組合員企業とともに取り組んでいる。Cu-Cuの低温ハイブリッド接合によるWoW(Wafer on Wafer)接合技術及びCoW(Chip on Wafer)接合技術に関するチョークポイント技術の開発とその実装化を目指したプロジェクトである。

今年度は、プロジェクト2年目にあたり、主要な設備の導入・立ち上げと、要素技術の構築に注力している。 プロジェクトは順調な立ち上がりを示し、概ね計画通り進行している。2023年12月に予定されている中間ゲートの目標値達成に向け研究開発を加速している。

## 2.3 基盤設計研究部門(旧VDEC部門)2022年度事業報告および2023年度事業計画

## 2.3.1 基盤設計研究部門概要

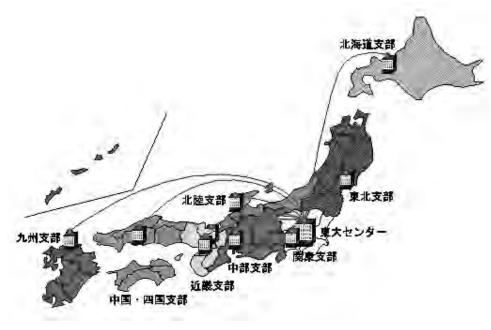

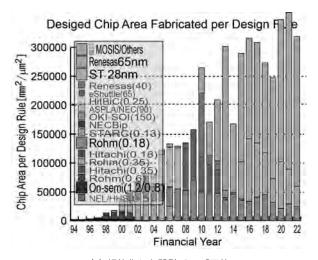

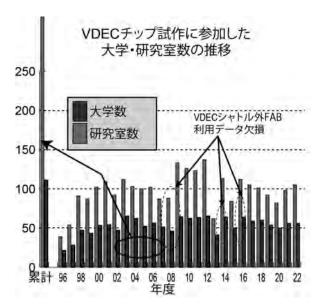

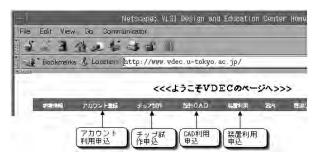

東京大学大規模集積システム設計教育研究センター (VDEC) は、1996年の発足以来『LSI教育情報の発信 拠点形成』、『VLSI設計支援教育用 CAD ソフトウエアの 整備』、『VLSIチップ試作支援』を3つの柱として、日本の大学・高専における集積回路設計教育に資する事業を展開してきた。2019年10月1日に東京大学における、半導体集積回路関係の強化を目指した組織改編により、東京大学大規模集積システム設計教育研究センターは東京大学大学院工学系研究科附属システムデザイン研究センター (d.lab) へと改組され、その中で、基盤設計研究部門がこれまでのVDECの担ってきた機能を引き続き担い、シームレスに活動を継続している。ここでは、d.lab 基盤設計研究部門の活動内容に基づき、以下に2022年度の概要を報告する。

VDECの使命は全国の国公私立大学および高専のLSI 設計研究・教育を高度化し、産業界に対しても優秀な LSI設計技術者を数多く送り出すことである、VDECの 発足より27年経過し、各大学におけるCADソフトウエ アの利用技術教育やLSI設計・設計フローに関する教 育の充実が図られている。その一方で、先端のLSI設 計技術およびそれに対応する CAD ソフトウエアは一層 複雑化し続けている。そのため、CADツールの導入に 際しては、CADベンダーから講師を招いてのセミナー の開催を継続しており、参加者の利便を図るために 2009年度より東京での開催と同時に映像配信による拠 点校での遠隔受講としている。VDECとしては各ユー ザ研究室内で"技術伝承"され、VDEC主催のセミナー がトリガーとなって最新のCAD利用技術が全国的に広 がることを期待している。なお、2022年度においては、 すべてのセミナーをオンラインで実施している. 一部 の項目に関しては、オンデマンド+ライブQ&Aという 形で実施し、参加への利便性の向上への取り組みを行 った。また、各社のツールチェインが複雑化し導入し ているツールを十分に使いこなすことが困難となって いるという現状を鑑み,各ツールベンダーの推奨する ツールチェインに関する講演会もツールセミナーの開 催に合わせる形で実施した.なお、2019年度末からの COVID-19感染拡大を受けて、各EDAベンダーから EDAツールの自宅からの利用に関する許諾を受け、 2022年度においても、日本国内における集積回路設計 研究・教育に遅滞の生じないよう取り組んだ.

## 2.3.2 基盤設計研究部門における教育の実施状況

LSI設計フローセミナーはLSI設計の基本概念教育と 複数のCADツールを連携する実用的設計例の体験教育 である。この目的でVDECでは社会人のリフレッシュ 教育プログラムと兼ねてLSI設計教育セミナーを開催 してきたが、2022年度は開催を断念している。

これらセミナーに加えてVDECでは年1回, 若手教官 と学生を中心としたVDEC デザイナー・フォーラムを 開催している。これはワークショップ形式の会合であ り、企業・大学からの招待講演に交えて、参加者が設 計事例を持ち寄ってその成功談,失敗談を交換する. これから設計を始めたいと考えている学生・教官もこ こでさまざまなノウハウを得ることができる。2022年 度はVDECデザイナー・フォーラムを9月30/10月1に温 泉ゆぽぽ秋田芸術村にてハイブリッド開催した。2011 年度から、VDEC活動における表彰として「IEEE SSCS Japan Chapter VDEC Design Award」の最終審査・表彰 をVDECデザイナー・フォーラムの場で行っており、 2022年は、IEEE SSCS Japan Chapter VDEC Design Award として、東京大学の島田泰慎さん、4件のVDEC デザイ ンアワード優秀賞, (島田泰慎 (東京大学), フーシー (東京工業大学), 李政 (東京工業大学), 岡田竜馬 (奈 良先端科学技術大学院大学), 3件のVDEC デザインア ワード奨励賞 (渡部吉祥 (東北大学), 長田将 (東京大 学),山口駿 (京都大学)),1件のVDEC デザインアワ ードアイデアコンテスト部門嘱望賞(三井健司(大阪 大学))を授与した.

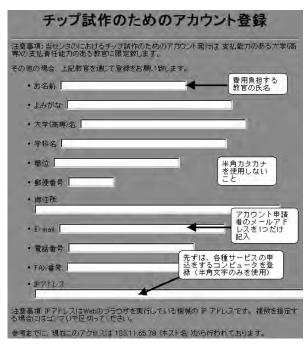

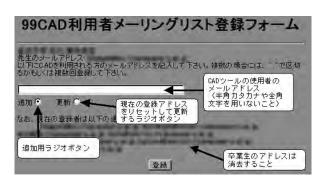

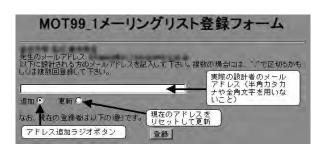

このようなセミナー、フォーラムを通じた教育システ ムによりLSI設計の基本的項目を学習できるようになっ ているが、それでも実際のLSI設計の場面では、さまざ まな困難に直面することが多い。初心者にとってはCAD ソフトウエアのセットアップは最大の問題である。セッ トアップの後もCADソフトウエアが発する"難解なエ ラーメッセージ"でとまどうことも多い。このような場 合に力を発揮するものがVDECメールグループである. VDECユーザはVDECのホームページからCADメール グループや試作技術対応のユーザグループに登録する ことができ、そこに直面する疑問点を投稿し、助けを 求めることができる。メールグループの登録ユーザは それに回答する義務を負っているわけではないが、ほ とんどの場合, 数時間から数日以内に経験豊かなユー ザからの支援を得ることができる。 ぜひこの仕組みを 活用することで問題解決の一助としていただきたい。

## 2.3.3 基盤設計研究部門における発表文献の推移

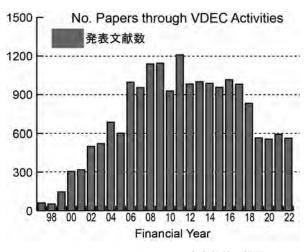

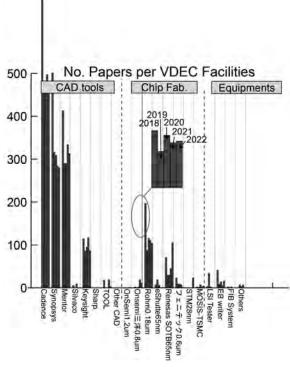

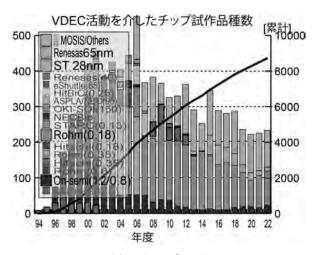

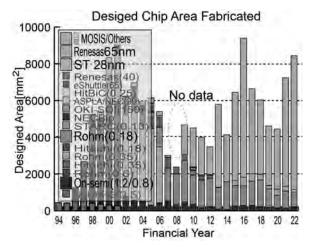

図2.3.1にVDECに関係する発表文献のVDECファシリティー利用状況を示す。論文執筆にあたりCADソフトウエアが幅広く利用されていることが確認できる。CADソフトウエアはチップ設計だけでなくチップ試作の準備段階で利用される場合が多いため、研究の基本アイデアを実証するツールとしての貢献度も大きい。

## 2.3.4 基盤設計研究部門におけるAIチップ設計拠点 活動概況

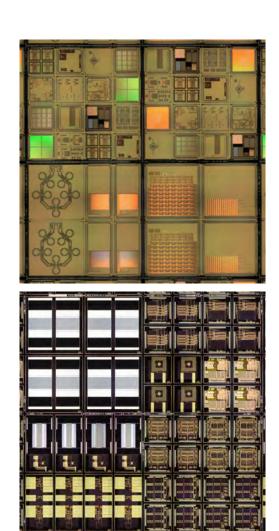

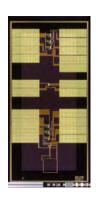

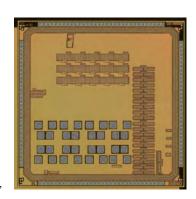

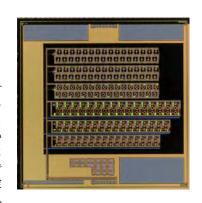

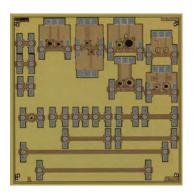

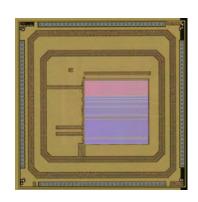

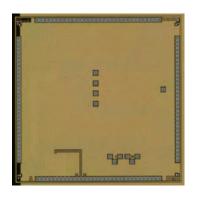

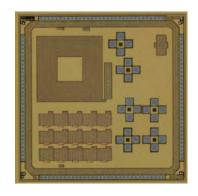

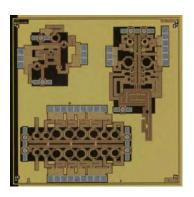

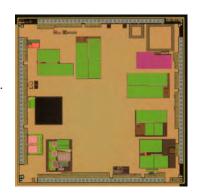

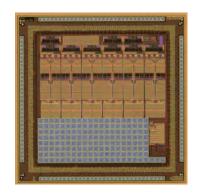

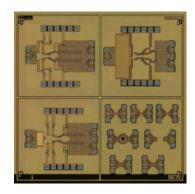

平成30年度 (2018年度) から東京大学VDEC, 国立 研究開発法人産業技術総合研究所が共同でNEDOから 受託している「AIチップ開発加速のためのイノベーシ ョン推進事業/研究開発項目②:AIチップ開発を加速 する共通基盤技術の開発」により、国内のベンチャー ・中小企業向けのEDA利用・設計環境を構築し、AIチ ップ設計拠点として活動を行っている. 本活動では, ベンチャー・中小企業がエンジニアリングサンプルま で試作可能なEDAツールライセンスの導入に加え, 40nm, 28nm, 12nm向けのIPを導入, また, 同プロジェ クト開始時に経済産業省からの補助金により導入され た、ハードウエアエミュレータによる大規模・高速設 計検証環境の提供を行っている。2020年度にNoCおよ びPCIe, DDR4などを備え、複数の機能IPコアを搭載可 能なSoCプラットフォームのAI-One設計を行い、利用 者の設計したAI IPコアを複数搭載したSoCとしてテー プアウトを行ったものが、組み立て等の関係で大幅に 遅れて2022年1月に納品され1週間足らずでSoCの基本 機能の検証,2021年度中にほぼすべてのIPコアの基本 動作の確認が完了するという大きな成果を上げてい る. さらに2022年6月には12nmで4種類のAI IPコアを 搭載したAI-Twoの設計試作を行い2023年3月までにす

図2.3.1 VDECを利用した発表文献数の推移

べてのIPコアのデモの実現を行っている。また、同活動をより強化するために、2019年9月1日に、「産総研・東大 AIチップデザインオープンイノベーションラボラトリ」(AIDL)を東京大学浅野キャンパス武田ビル内に設置し研究を加速させている。

## 2.3.5 基盤設計研究部門の2023年度の活動計画

2023年度においても、従来通りアカデミック向けの活動を継続する.

## 【設計情報発信・セミナー開催】

本年度は、1997年度より継続しているCADツール利用法に関する技術セミナー、1998年度から継続している社会人向けの「リフレッシュセミナー」、1996年度より継続している若手のための「デザイナーズフォーラム」を継続して開催する。教科書、教材の整備充実を行なうことを予定している。

## 【CADツール提供】

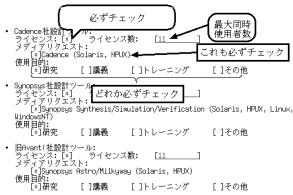

上流設計 (Cadence, Synopsys), 中流設計 (Synopsys, Cadence), 下流設計 (Cadence) の各基本ツールを, 2023年度もサポートしていく. これに加え2002年度から 導入 した 設計 検証 (Mentor: Caribre, ModelSim, Catapult等), 2004年度から導入したアナログRF設計ツール (Agilent: ADS/EMPro/GoldenGate) を継続してサポートするとともに, 2005年度より提供を受けている

図2.3.2 VDECファシリティー利用状況

Sharp社Cベース設計ツール(BachC)を継続してサポートする。2008年度より提供を開始しているTOOL社レイアウト表示プラットフォーム(Lavis)に関しても利用状況に基づき継続を行うとともに、2011年度からのSpringSoft社の検証ツールは、SpringSoft社がCadence社に買収されCadence社のツール群としてのサポートが継続されることになっている。

## 【チップ試作支援】

2023年度は、2022年度から引き続きローム株式会社の0.18umCMOSプロセスおよびオンセミ-三洋半導体0.8μmCMOSを定常試作として継続する(すでに一部の試作は進行中である)。なお、一部のチップ試作に関

しては試作申込数が少ない場合に試作キャンセルとなることがある.また,2020年度に検討を開始した,IHP SiGeBiCMOS 0.18um試作を継続する.

## 【そのほか】

経済産業省・NEDOの「AIチップ開発加速のためのイノベーション推進事業」における「AIチップ開発を加速する共通基盤技術の開発」」事業が2023年3月に終了し、この事業を自立して活動するために、「産総研・東大 AIチップデザインオープンイノベーションラボラトリ」(AIDL) 第2期を東京大学浅野キャンパス武田ビル内に設置し、AIチップの設計・評価・検証等の開発環境を中小・ベンチャー企業への提供を継続している。

表2.3.1 VDECチップ試作スケジュール(2023年度)

【CMOS 0.8 μ m 2P2M】 オン・セミコンダクタ

|           | 試作申込締切   | 設計締切      | 納品・試作完了    |

|-----------|----------|-----------|------------|

| 2023年度第1回 | 2023/7/3 | 2023/9/25 | 2023/12/18 |

| 2023年度第2回 | 2023/1/9 | 2023/3/25 | 2023/6/24  |

## 【CMOS 0.18 μ m 1P5M (+MiM)】 ローム株式会社

|                       | 試作申込締切    | 設計締切       | 納品・試作完了    |

|-----------------------|-----------|------------|------------|

| 2023年度第1回(2023年7月試作)  | 2023/4/3  | 2023/6/26  | 2023/10/13 |

| 2023年度第2回(2023年9月試作)  | 2023/6/12 | 2023/9/4   | 2023/12/16 |

| 2023年度第3回(2023年11月試作) | 2023/7/31 | 2023/10/23 | 2024/2/9   |

| 2023年度第4回(2024年3月試作)  | 2023/12/4 | 2024/2/26  | 2024/6/7   |

## 2.4 基盤デバイス研究部門

## 2.4.1 基盤デバイス研究部門のミッション

d.lab 基盤デバイス研究部門は、自らも現役研究者と してクリーンルームにおいて実験研究を牽引する三田 吉郎教授を部門長とし、関連専攻(総合研究機構、電 気系工学専攻,機械系工学専攻等)と人的・予算的協 力を行いながら、高度微細デバイス研究の必須3要素 (後述)を整備・運営・研究する30名規模のチームであ る、特に令和4年度は、武田先端知に集う人的知を研究 レイヤーで見える化するために新しく二つの組織が成 立した. 一つ目は「ナノシステム集積センター (NanoHub) であり、このうち三田教授はデバイス試作 研究部門長を務め、デバイス研究の国際共同研究を含 む活発化を目指す。二つ目は基盤デバイス研究部門の 寄付講座「ナノシステム集積技術の創製」である。こ れは、「武田先端知に集う技術を再利用可能な形で蓄積 し,新たな共同研究で展開をする」という主旨に武田 先端知がゆかりとなった寄付者の賛同を得て設立した ものであり、令和4年度より5年間存続する。

集積回路に代表される半導体エレクトロニクス素子,センサ・マイクロシステムなど新規分野の研究には,①加工・計測装置への膨大な設備投資と,②学問に裏付けられた微細加工技術の厚い蓄積,そして③最先端の加工技術を開拓する研究開発力が必須である.上記高度微細デバイス研究の必須3要素は,個々の研究室で開発され,個々の研究室に知見が蓄積されるのが20世紀後半の我が国の大学における基本形態であった.しかしながら,加工・計測装置は年々高度化・大型化し,21世紀に至り,潤沢に資金を持つ研究室であっても一流装置の調達そして維持が困難な時代となった.もと

より大学高専、企業や国研、NPOにおける個々の研究室全てが等しく潤沢に巨額の資金と潤沢な人的リソースを「独占所有」することは不可能であるが、1996年のVDEC設立時に整備した「集積回路設計研究におけるシェアードエコノミーモデル(ファウンドリ)」を微細加工・計測研究分野に対して水平展開し、何人に対しても開かれた「オープンプラットフォーム」を整備し運用する「互助」の仕組みを成立させられれば、恵まれた環境を「等価的に所有(共有)」でき、全国津々浦々で最先端研究を実施することができる。

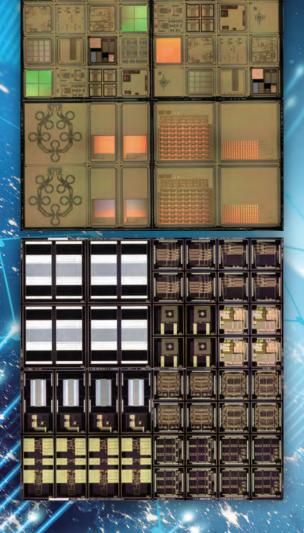

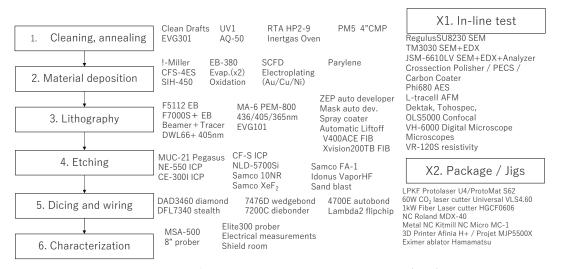

上記目的を達成するために d.lab 基盤部門では, 2001 年に武田郁夫氏 (現アドバンテスト創業者) による工 学系研究科(小宮山宏工学部長)及び大規模集積シス テム設計教育研究センター(浅田邦博センター長)に 対して行われた巨額の寄付により、2003年12月に竣工 した「武田先端知ビル」地下スーパークリーンルーム (ISO クラス3, 実測クラス1を含む600㎡), 及び上層階 スペースの固有面積および借室面積を利用、価値総額 43億円を超える一流の微細加工・計測装置を戦略的に 展開, 共用授業を展開している (図1). 管理する公開 装置は、アドバンテスト株式会社大浦会長決断の寄付 による「世界最速」高速電子線描画装置F5112+VD01 に始まり、平成24年度補正予算(アベノミクス「第一 の矢」)によって導入された高精細電子線描画装置 F7000S-VD02, シリコン高速深掘りエッチング装置 SPTS MUC-21 ASE-Pegasus, 研究室レベルで導入できる 最も高精細なクラスの走査型電子顕微鏡 Hitachi Regulus SU8230等約100台であり、洗浄、製膜、リソグラフィ、 エッチング,組み立て,評価プロセスの大半をカバー

図1 武田先端知スーパークリーンルーム沿革

図2 d.lab基盤デバイス部門が管理公開する共同利用装置(抜粋)

している. 現時点でカバーできていない技術分野の装置は, ナノテクノロジープラットフォーム16拠点のネットワークによって提供している.

## 2.4.2 基盤デバイス研究部門が運営する「武田先端 知クリーンルーム」共有環境

拠点は, 文部科学省事業(2020-2031)「マテリアル先 端リサーチインフラ事業東京大学ハブ微細加工拠点」 または「武田先端知クリーンルーム」と呼ばれ、「装置 共用という価値観を共有する者」に対して広く開かれ ている。単なる試作の外注先ではないと、利用者一人 一人が自覚することが非常に大切であり、「自助・共助 ・公助」という価値観を理解し共有することによって 初めて、研究室運営者としての自分が当然支払うべき コスト(人的,金銭的,時間的)を最低限に抑えて直 ちに最先端の研究が展開できる。価値観の共有による 利益は例えば,建物も含め83億円を超える施設整備 費,年間3.5億円の運転経費,これらを整備し先端プロ セスの知見を蓄積していた20年という時間の短縮効果 である。このように絶大な効果のため、多数の研究室 の賛同を得ている。 賛同研究室数は過去12年で550研 究室を超え、登録者は年間1062名となった。

運用は「自助・公助・共助」を旨とし、利用者負担金 (内規に基づく)、d.lab運営費交付金、文部科学省ナノテクノロジープラットフォーム事業、関連研究室(武田先端知ビルおよびクリーンルームの借室研究室)やd.labと直接共同研究関係のある企業等からの研究資金を収入とし、それぞれの予算使途を厳密に区分して各種法規規則や命令を完全に遵守して公正に運用している。運転資金年間3.5億円の内訳は大づかみに整備費、電気代・修理費・人件費からなる。特に昨今電気代の

負担増が厳しい。法人化以降,中期計画に基づいた弾力的な運用が可能であり,節約できた運営費を原資として職員の安定雇用や小・中規模装置の更新,増強に割り当てている。

基盤デバイス研究部門では、多数の利用者が抱える 微細加工への期待に日夜接することで、技術動向の「空 気感」を持っている. 需要が高く、分野を超えた普遍 性が見込まれる基幹技術については自らのチームで技 術開発を行い、積極的に論文発表して公共財とするよ うに努めている.

さらに、d.labの一部門であるという「地の利」を活 かし、集積回路素子 (LSI) と新規MEMS構造の集積 化,所謂「集積化MEMS」の研究開発を10年以上にわ たって実践している。詳細は原著論文[2]にまとめてい るとおり、「LSIファウンドリ」機能によって、特定用 途向け電子デバイスの搭載されたシリコンウエーハを 協力会社(例:フェニテックセミコンダクター社)で 試作し,取得したウエーハに対して武田先端知ビルス ーパークリーンルームを始めとするオープンプラット フォームにおいて微細後加工を施し、センサ・アクチ ュエータ素子とする仕組みである. この仕組みによれ ば、信頼性が必要であるトランジスタ回路部分は全く 苦労することなく入手でき、新規機能であるために外 注の引受先が存在しないMEMS部分は自前で行う。ま さに「世界初の機能を」「世界最高の性能で」実現する ことが可能な、世界的にもユニークな仕組みといえる. 企業も含む共同研究ベースで年1回の共同試作(固定枠 方式)を行っている.

[2] Y. Mita et al., Japanese Journal of Applied Physics, 56,p. 06GA03, 2017 (2017) DOI: 10.7567/JJAP.56.06GA03

#### 2.4.3 基盤デバイス研究部門2022年活動報告

【受賞】文部科学省事業ナノテクノロジープラットフォ ームでは、毎年3000件を超える利用報告書の中から特 に優れた利用成果を有識者による委員会により数件選 定, 顕彰している. 基盤デバイス研究部門が推薦した 利用成果「静的・動的局所結晶格子制御による酸化物 材料の機能創発」課題が秀でた利用成果最優秀賞を受 賞した (図3) [3]. 2019年の秀でた利用成果受賞, 2020 年の秀でた利用成果最優秀賞、2021年の秀でた利用成 果最優秀賞に続く四年連続の受賞、三年連続最優秀賞 の栄誉. このように、ナノプラ10年の歴史で誰にも超 えられない領域に到達しつつあることが客観的に明ら かになっている. 受賞者は満を持して推薦した東京大 学田畑仁教授 (バイオエンジニアリング専攻) の研究 であり、研究成果の学術的重要性はもちろんのこと、 成果をベンチャー展開するにあたり電子デバイスとし ての性能を短期間に検証できる武田先端知スーパーク リーンルームの効能が認められた.

[3] https://www.t.u-tokyo.ac.jp/press/pr2023-01-17-001

【感染0&前年以上の利用成果を得る】2020年度に引き続き、完全なパンデミック対策を施した。クリーンルームに入った後発症したケースがあった(利用者、業者等)が、伝染は0であった。年間アクセス回数は2万

回に至っており、本拠点で取っている感染症対策は有効であるという事実が着実に積みあがっている.

【ポストナノプラへの参画・採択】クリーンルーム運営「公助」は、平成24年度より主にナノテクノロジープラットフォーム事業で賄われてきた。令和3年度で10年間の期限が終了したが文部科学省が中心となって、ナノプラのヘリテージを活かした、プロセスを含むマテリアルDX(ディジタルトランスフォーメーション)事業が令和3年度より開始された。ナノプラは「構造解析・微細加工・分子物質合成」という分野別の横連携方式であったが、マテリアルDXでは「研究領域ごとのハブースポーク」方式となった。

d.lab 基盤部門は、総合研究機構ナノ工学センターと連携し、さらに情報基盤センターを加えて、幾原雄一教授代表で計画に参画している。次世代X-nics研究拠点にd.labが採択され、その一部のプロジェクト実施のため同じく令和3年度、4年度にわたり措置され、装置整備が加速されている。年間運転経費3.5億円に加え、装置で45億円が世界一流のプラットフォームに伍すために必要で、定期的なメンテナンス(例えば14年償還とすると年間3億円ずつ)が引き続き必要とされているので、公助、共助、自助が手を携えながら引き続き「装置・技術・人」の集積化に努めてゆく。

図3 ナノテク展での受賞記念ポスターを前に関係者で記念撮影

## 2.5 「アドバンテストD2T寄附講座」活動報告

## 2.5.1 「アドバンテストD2T寄附講座」の紹介

## 2.5.1.1 アドバンテスト D2T 寄附研究部門(現寄 附講座)設立の趣旨

これまでのVDECの活動を通じ、多くの大学・高専でVLSI設計・試作文化が根付き、活発な設計研究・教育活動が行われています。このような状況の中、株式会社アドバンテストからの寄附金により、「アドバンテストD2T寄附研究部門」が2007年10月に VDEC内に設立されました。「アドバンテストD2T寄附研究部門」は、全国の学生にVLSIの設計からテストまで一貫した研究・教育環境を提供することで、テスト設計の専門家となりえる人材を育成するとともに、SoCの設計に関する研究を支援することを目的としております。従来、VDECではVLSIの「設計・試作」という面からの活動を重点的に行ってまいりましたが、「設計」だけでなく「テスト」の観点からも研究・教育の中心拠点となるべく "Design to Test (D2T)"の理念のもと、国内

の大学・高専における「テスト研究・教育」の拠点と しての活動を行っています.

当部門はこれまで2007年10月~2010年9月 (第1期), 2010年10月~2013年9月 (第2期), 2013年10月~2016年 9月 (第3期), 2016年10月~2019年9月 (第4期) の計12 年間に渡るプロジェクトを遂行してきました. 東京大 学大学院工学系研究科附属システムデザイン研究セン ター (d.lab) が2019年10月に発足後、D2T 寄附研究部 門は研究のさらなる発展, D2T教育により重心を置い た「アドバンテストD2T寄附講座」としてセンター内 に設置されました。2019年10月から株式会社アドバン テストのご厚意により新たに開始した第6期(2022年10 月~2025年9月) の1年目が開始いたしました。本報告 は第5期の最終年度、2021年10月~2022年9月の活動報 告となります。D2Tに関する研究とともに、教育活動 の充実図っていく予定であります。当寄附講座の活動 の詳細については、続く各章においてそれぞれ報告い たします.

## 2.5.1.2 アドバンテスト D2T 寄附講座構成員

特任教授

池田

誠

特任講師

肥後

昭男

博士研究員 Zolboo Byambadorj

共同研究員 浅見 幸司

(株式会社アドバンテスト研究所)

共同研究員 石田 雅裕

(株式会社アドバンテスト)

学術支援職員 山口 隆弘 事務補佐員 岡崎 真紀子

## 2.5.2 「第17回 D2T シンポジウム」 開催報告

2022年9月15日(木)に、オンライン(一部ハイブリッド)開催による「第17回D2Tシンポジウム」を開催し、たくさんの皆様にご参加を頂きました。

今回のシンポジウムでは、国内外から著名な招待講演者として香港大学のZhongrui Wang先生、キオクシアの市原麗華様、アイオーコアの中村隆宏様、岐阜大学の久武信太郎先生、NICTの原基揚先生、北海道大学の冨岡克広先生をお招きし、最新の研究についての貴重な講演を頂きました。「ミリ波測定、シリコンフォトニクス、メモリ、メモリスタ、III-V族ナノワイヤデバイス、原子時計」をキーワードに最新の研究についての貴重な講演を頂きました。

このようなCOVID-19新型コロナ感染症影響下でしたので、ハイブリッド開催とはなりましたが、大変盛況な会となりましたことを改めて御礼申し上げるとともに、2023年9月8日(金)に開催する第18回シンポジウムは対面実施をいたしますのでご参加を心よりお持ち申し上げる次第です。

## 17th D2T Symposium Program ONLINE September 15, 2022

| 10:00 | Opening Remarks                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------|

|       | Makoto Ikeda (d.lab, School of Engineering, the University of Tokyo)                                                    |

|       | Yoshiaki Yoshida (President & CEO, ADVANTEST CORPORATION)                                                               |

| 10:10 | Session 1 (Chairperson: Tetsuya Iizuka, d.lab, the University of Tokyo)                                                 |

|       | Measurements in millimeter-wave and THz wave band based on photonics                                                    |

|       | Shintaro Hisatake, Associate Professor (Gifu University)                                                                |

|       | High-density integrated optical transceiver based on silicon photonics technology"                                      |

|       | Takahiro Nakamura, Ph.D. (AIO Core Co., Ltd.)                                                                           |

| 11:40 | Lunch                                                                                                                   |

| 13:10 | Session 2 (Chairperson: Atsutake Kosuge, d.lab, the University of Tokyo)                                                |

|       | Reliability study of ferroelectric HfO2 memory using advanced analytical techniques                                     |

|       | Reika Ichihara (Institute of Memory Technology R&D, Kioxia Corporation)                                                 |

|       | Memristor-based echo state networks                                                                                     |

|       | Zhongrui Wang, Assistant Professor (Department of Electrical and Electronic Engineering at the University of Hong Kong) |

| 14:40 | 15min break                                                                                                             |

| 14:55 | Session 3 (Chairperson: Yoshio Mita, d.lab, the University of Tokyo)                                                    |

|       | Vertical III-V Nanowire Transistors and Prospects                                                                       |

|       | Katsuhiro Tomioka, Associate Professor (Hokkaido University)                                                            |

|       | CLIFS: Chip Level Integrated Frequency Standard, How do we approach the cliff of CLIFS?                                 |

|       | Motoaki Hara, Senior Researcher (National Institute of Information and Communications Technology (NICT))                |

| 16:15 | Session 4                                                                                                               |

|       | Recent D2T research department progress                                                                                 |

|       | Akio Higo, Lecturer (d.lab, the University of Tokyo)                                                                    |

| 16:30 | Closing Remarks                                                                                                         |

|       | Tadahiro Kuroda (Director, d.lab, School of Engineering, the University of Tokyo)                                       |

## 2.5.3 研究活動報告

## ■高精度波形測定技術

山口 隆弘, 肥後 昭男, 飯塚 哲也, 池田 誠 確率的アナログ - デジタル変換器 (Stochastic Analog to Digital Converter; ADC) の研究をおこなっている. とくに, 耐不規則性をより向上させるための, 確率の中央値をもちいたレベル交叉時刻検出方式について研究している.

2乗平均誤差の有効性の検証をすすめた. 『プロセス変動<u>あり</u>のコンパレータ』に対応する理論を, MC (モンテカルロ) 実験により検証した.

## ■5G多チャンネル・ミリ波信号測定手法の研究

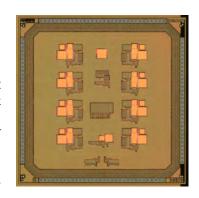

浅見 幸司,Byambadorj Zolboo,小池 良吾, Sheng Guo, Mai-Khanh Nguyen Ngoc,肥後 昭男, 飯塚 哲也,藤田 昌宏,松本 高士,池田 誠

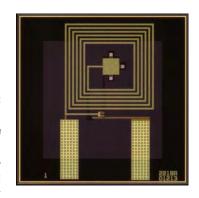

ミリ波信号をover-the-air (OTA) 環境で測定するための、要素技術の研究を行っている.ミリ波用アンテナの近傍界測定のため、4-channelのプラナー型アレイアンテナを開発した.アンテナ間カップリングを低く抑えるため、メタサーフェス技術を採用した.実際にプローブを作製し、特性の確認およびアンテナ測定実験を進めている。また、測定アルゴリズムの確認のため、市販のホーンアンテナをプローブとして用い、5G用アンテナを測定した.測定した近傍界からプローブの影響を補正し、精度よく遠方界を推定できることを確認した.

## ■ ATE向け高速・高精度な多ピンタイミング CAL技術

石田雅裕, 大塚日嵩, 飯塚哲也, 徐祖楽, 肥後昭男, 藤田昌宏, 池田誠

半導体試験装置 (ATE) では数千から数万ピンの信 号入出力チャンネルをもち、被試験デバイス (DUT) へ出力される試験信号のタイミングおよびDUTから出 力される信号の比較タイミングをそれぞれ一致させる タイミングキャリブレーション (CAL) が必要である. 本研究テーマでは、ATE に適用可能な高速かつ高精度 な多ピンタイミングCAL方式の研究をおこなってい る. 本年度は、昨年度TSMC 65nm CMOSプロセスで 試作したTEG回路の評価をおこない、コンパレータ CAL用の基準タイミング発生器, および, ドライバ CAL 用のタイミング測定器のCh間特性差が動作環境(温 度,電源電圧)により大きく変化しないことを確認し, CAL精度の目標1psを実現できる見込みを得た。タイミ ングCAL用回路を多ch実装したときのクロストークや 信号の取り出し、CAL用回路のCALなどの課題をまと め, 多ピンタイミング CAL 技術に関する共同研究テー マを完了した.

## 2.5.4 研究発表

## 論文誌

[1] Zolboo Byambadorj, Koji Asami, Takahiro J. Yamaguchi, Akio Higo, Masahiro Fujita and Tetsuya Iizuka, "High-Precision Sub-Nyquist Sampling System Based on Modulated Wideband Converter for Communication Device Testing," IEEE Transactions on Circuits and Systems-I: Regular Papers, vol. 69, no. 1, pp. 378 - 388, Jan. 2022

## 第3章 d.lab概要

## 3.1 組織概要

東京大学大学院工学系研究科附属システムデザイン研究センター (d.lab) は、2019年10月に、東京大学における半導体関連研究の強化を目指し設置された. d.lab は、知識集約型社会の到来に備え、システムのアイデアを持つ者が誰でも専用チップを即座に入手できるよう、デザインの手法と製造のエコシステムを再構築することを目指している。また、データ駆動型システムのデザインプラットフォームを作り、データ駆動型社会で活躍する人材の育成を目標とする。

センター長の下,先端設計研究部門,基盤設計研究部門,先端デバイス研究部門,基盤デバイス研究部門の4つの部門において,互いに連携しながら活動を行っている。なお、専任教員のほか,東京大学の他部局や工学系研究科を本務とする教員が,兼務で在籍している。

東京大学大規模集積システム設計教育研究センター (VDEC) は、1996年5月に全国共同利用施設として発足し、国立大学法人化に伴い東京大学の1部局としての位置づけを経て、国公私立大学と工業高等専門学校におけるVLSI設計教育の充実と研究活動を継続してきたが、d.lab設置の際にこれに合流することとなった。それまでVDECが担ってきた活動は、d.labの基盤設計研究部門における「VDEC機能」として継続しつつ、先端設計研究部門における産学連携をも強化した最先端設計研究の強化を目指した活動が行われている。

VDECの発足当初は、専任教官5名と事務官1名という小さな組織であったが、2023年4月1日現在、d.labの人員構成は、教授11名(内専任2名、兼任8名、特任1名)、准教授3名(内専任2名、特任1名)、講師2名(内

専任1名,特任1名),助教2名,研究員18名 (内上席研究員2名,主幹研究員1名,特任研究員15名),学術専門職員11名,副課長1名,係長2名,特任専門職員1名,係員1名となっている.

なお、VDECの時代には2年を単位として2名の教官 を派遣する「流動教官制度」を実施していたが、現在 では基盤設計研究部門に「協力教員制度」を有してお り、全国の各大学との教員との連携を図っている。

d.labは、研究探求と技術実践の橋渡しの場、また産学官連携と人的交流を促進する場として、2020年から協賛事業を開始し、40社を越える企業から参加を頂いている。また、2022年には文科省次世代X-nics半導体創成拠点形成事業に採択され、半導体技術の民主化を実現する基幹技術(Agile技術)を整備し、プラットフォームとして研究に展開し、研究成果・産業への波及効果・高度人材の育成を目指している。さらに、目白台インターナショナル・ビレッジに研究スペースを設け、先端システム技術研究組合に参画するなど、活動を日々加速させているところである。

2018年度-2022年度には、経済産業省/NEDOのプロジェクト「AIチップ設計拠点」として、国内の中小企業ベンチャー向けのチップ設計環境の整備を、産業技術総合研究所(産総研)とともに実施した。2023年度からは、産総研が東大内に設けるオープンイノベーションラボラトリ(OIL)「AIDL」が主体として拠点を運営することで、アカデミック向けのチップ設計環境「VDEC機能」、中小ベンチャー向けのチップ設計環境「AIチップ設計拠点」のチップ設計の拠点機能を拡充させていく。

## 3.2 人事報告

## d.lab人事(2023年4月1日付け)

| 先端設計<br>基盤設計<br>先端デバ<br>(東京大学 | 長・教授<br>研究部門長・特任教授<br>研究部門長・教授<br>イス研究部門長・教授<br>学生産技術研究所) | 黒濱池平                                    | 田田田本 | 基俊  |               |

|-------------------------------|-----------------------------------------------------------|-----------------------------------------|------|-----|---------------|

|                               | イス研究部門長・教授<br>学大学院工学系研究科<br>学専攻)                          | ======================================= | 田    | 吉   | 郎             |

|                               | 授<br>学大学院情報理工学系                                           | 中                                       | 村    |     | 宏             |

|                               | 授<br>学大学院工学系研究科<br>学専攻)                                   | 竹                                       | 内    |     | 健             |

|                               | 授<br>学大学院工学系研究科<br>学専攻)                                   | 高                                       | 木    | 信   | _             |

|                               | 授<br>学大学院工学系研究科<br>学専攻)                                   | 染                                       | 谷    | 隆   | 夫             |

| 教<br>(東京大学                    | 授<br>学大学院工学系研究科<br>ル工学専攻)                                 | 内                                       | 田    |     | 建             |

| 教                             | 授<br>学大学院工学系研究科                                           | 竹                                       | 中    |     | 充             |

|                               | 師(産業界客員教員)                                                | 水                                       | 野    | 正   | 之             |

| 准教                            | 授                                                         | 小                                       | 林    | 正   | 治             |

| 准教                            | 授                                                         | 飯                                       | 塚    | 哲   | 也             |

| 特任准教                          | 授                                                         | 中                                       | 根    | 了   | 昌             |

| 講                             | 師                                                         | 小                                       | 菅    | 敦   | 丈             |

| 特任講                           | 師                                                         | 肥                                       | 後    | 昭   | 男             |

| 助                             | 教                                                         | NG                                      | JYEN | N N | GOC MAI KHANH |

| 助                             | 教                                                         | 松                                       | 本    | 高   | 士             |

| 上席研究                          | 員                                                         | 若                                       | 林    | _   | 敏             |

| 上席研究                          | 員                                                         | 丹                                       | 羽    | 正   | 昭             |

| 主幹研究                          | 員                                                         | 高                                       | 木    |     | 剛             |

| 特任研究                          | 員                                                         | 島                                       | 本    | 直   | 伸             |

| 特任研究                          | 員                                                         | 荒                                       | Ш    | 文   | 男             |

| 特任研究                          | 員                                                         | 落                                       | 合    | 幸   | 徳             |

| 特任研究                          | 員                                                         | BYA                                     | MBA  | DOI | RJ ZOLBOO     |

| 特任研究                          | 員                                                         | $\vec{-}$                               | 宮    | 健   | 生             |

| 特任研究                          | 員                                                         | 坪                                       | 井    | 伸   | =             |

特任研究員 特任研究員 特任研究員 特任研究員 特任研究員 特任研究員 特任研究員 特任研究員 特任研究員 学術専門職員 学術専門職員 学術専門職員 学術専門職員 学術専門職員 学術専門職員 学術専門職員 学術専門職員 学術専門職員 学術専門職員

川野連也 CHITRA PANDY 山本和徳 最 上 徹 藤田昌宏 DURAN CKRISTIAN 博 文 角 鈴木康之 WANG JUNSHA 長谷川 岡田光司 四手井 綱 章 泰 林 弘 太田悦子 YIP WAI YEUNG 窪 田 通 孝 賀 浩 有 小倉建治 上 友里恵 井

副 課 長 係 長 長 特任専門職員

学術専門職員

中村羽明彦靖史明郎和田嶋舞芳郎郎

近藤翔午

※ ( ) が記載されている教員は、( ) 内が本務先である.

## 2022年度東京大学大学院工学系研究科附属システムデザイン研究センター基盤設計研究部門 (VDEC) 全国運営協議会委員名簿

| 氏  | 名  | 所属 · 職 位                            | 任期                                                 | 連絡先                                           |                                |  |  | 連絡が | 絡 先 |

|----|----|-------------------------------------|----------------------------------------------------|-----------------------------------------------|--------------------------------|--|--|-----|-----|

|    | 10 | 門 周 朝 1立                            | 江朔                                                 | TeL/Fax                                       | E-mail                         |  |  |     |     |

| 池田 | 誠  | 東京大学大学院工学系研究科附属システムデザイン研究センター 教授    | 2022.4.1~<br>2024.3.31                             | TEL 03 (5841) 6661                            | ikeda@silicon.u-tokyo.ac.jp    |  |  |     |     |

| 黒田 | 忠広 | 東京大学大学院工学系研究科附属システムデザイン研究センター 教授    | 2022.4.1~<br>2024.3.31                             | TEL 03 (5841) 6561                            | kuroda@ee.t.u-tokyo.ac.jp      |  |  |     |     |

| 高木 | 信一 | 東京大学大学院工学系研究科電気系工学<br>専攻 教授         | 2022.4.1~<br>2024.3.31                             | TEL 03 (5841) 7467                            | takagi@ee.t.u-tokyo.ac.jp      |  |  |     |     |

| 池辺 | 将之 | 北海道大学量子集積エレクトロニクス研究<br>センター 教授      | 2022.4.1~<br>2024.3.31                             | TEL/FAX 011-716-6004                          | ikebe@ist.hokudai.ac.jp        |  |  |     |     |

| 黒田 | 理人 | 東北大学大学院工学研究科技術社会シス<br>テム専攻 教授       | 2022.4.1~<br>2024.3.31                             | TEL 022 (795) 4836                            | rihito.kuroda.e3@tohoku.ac.jp  |  |  |     |     |

| 一色 | 剛  | 東京工業大学 工学院 情報通信系 教授                 | 2022.4.1~<br>2024.3.31                             | TEL/FAX 03 (5734) 2842                        | isshiki@ict.e.titech.ac.jp     |  |  |     |     |

| 岡田 | 健一 | 東京工業大学工学院電気電子系 教授                   | 2022.4.1~<br>2024.3.31                             | TEL 03-5734-3764                              | okada@ee.e.titech.ac.jp        |  |  |     |     |

| 史  | 又華 | 早稲田大学基幹理工学部電子物理システム学科 教授            | 2022.4.1~<br>2024.3.31                             | TEL 03-5286-3400                              | shi@waseda.jp                  |  |  |     |     |

| 北川 | 章夫 | 金沢大学理工研究域電子情報通信学系<br>教授             | 2022.4.1~<br>2024.3.31                             | TEL 076 (234) 4863<br>FAX 076 (234) 4863      | kitagawa@is.t.kanazawa-u.ac.jp |  |  |     |     |

| 石原 | 亨  | 名古屋大学大学院情報学研究科情報シス<br>テム学専攻 教授      | 2022.4.1~<br>2024.3.31                             | TEL 052 (789) 4363                            | ishihara@i.nagoya-u.ac.jp      |  |  |     |     |

| 佐藤 | 高史 | 京都大学大学院情報学研究科通信情報システム専攻 教授          | 2022.4.1~<br>2024.3.31                             | TEL 075 (753) 4801<br>FAX 075 (753) 4802      | takashi@i.kyoto-u.ac.jp        |  |  |     |     |

| 廣瀬 | 哲也 | 大阪大学大学院工学研究科電気電子情報<br>通信工学専攻 教授     | 2022.4.1~<br>2024.3.31                             | TEL 06 (6879) 7761                            | hirose@eei.eng.osaka-u.ac.jp   |  |  |     |     |

| 藤島 | 実  | 広島大学大学院先進理工系科学研究科<br>量子物質科学プログラム 教授 | 2022.4.1~<br>2024.3.31                             | TEL 082 (424) 6269                            | fuji@hiroshima-u.ac.jp         |  |  |     |     |

| 井上 | 弘士 | 九州大学大学院システム情報科学研究院<br>情報知能工学部門 教授   | 2022.4.1~<br>2024.3.31                             | TEL 092 (802) 3793<br>FAX 092 (802) 3786      | inoue@ait.kyushu-u.ac.jp       |  |  |     |     |

| 宇野 | 重康 | 立命館大学理工学部電気電子工学科<br>教授              | 2022.4.1~<br>2024.3.31                             | TEL 077 (599) 4278                            | suno@fc.ritsumei.ac.jp         |  |  |     |     |

| 兵庫 | 明  | 東京理科大学理工学部電気電子情報工学科 教授              | 2022.4.1~<br>2024.3.31                             | TEL 04(7124)1501<br>内3756<br>FAX 04(7122)5171 | hyogo@ee.noda.tus.ac.jp        |  |  |     |     |

| 石黒 | 仁揮 | 慶應義塾大学理工学部電子工学科 教授                  | 2022.4.1 ~<br>2022.7.31<br>2023.4.1 ~<br>2024.3.31 | TEL 045 (566) 1815                            | ishikuro@elec.keio.ac.jp       |  |  |     |     |

| 永田 | 真  | 神戸大学大学院科学技術イノベーション<br>研究科 教授        | 2022.4.1~<br>2024.3.31                             | TEL 078 (803) 6569<br>or 6221                 | nagata@cs.kobe-u.ac.jp         |  |  |     |     |

| 名倉 | 徹  | 福岡大学工学部電子情報工学科 教授                   | 2022.4.1~<br>2024.3.31                             | TEL 092 (871) 6631                            | nakura@fukuoka-u.ac.jp         |  |  |     |     |

## 2022年度 システムデザイン研究センター運営委員会委員名簿

| 区分   | 氏  | 名  | 所 属                     | 任 期                    | メールアドレス                               |

|------|----|----|-------------------------|------------------------|---------------------------------------|

| 委員長  | 黒田 | 忠広 | システムデザイン研究センター<br>センター長 | -                      | kuroda@dlab.t.u-tokyo.ac.jp           |

| 1号委員 | 染谷 | 隆夫 | 工学系研究科長                 | _                      | someya@ee.t.u-tokyo.ac.jp             |

| 2号委員 | 竹内 | 健  | 電気系工学専攻長                | _                      | takeuchi@co-design.t.u-tokyo.ac.jp    |

| 3号委員 | 柴田 | 直哉 | 総合研究機構長                 | _                      | shibata@sigma.t.u-tokyo.ac.jp         |

| 4号委員 | 池田 | 誠  | システムデザイン研究センター          | 2021.4.1~<br>2023.3.31 | ikeda@silicon.u-tokyo.ac.jp           |

| 4号委員 | 小林 | 正治 | システムデザイン研究センター          | 2021.4.1~<br>2023.3.31 | masa-kobayashi@nano.iis.u-tokyo.ac.jp |

| 4号委員 | 飯塚 | 哲也 | システムデザイン研究センター          | 2021.4.1~<br>2023.3.31 | iizuka@vdec.u-tokyo.ac.jp             |

| 5号委員 | 高木 | 信一 | 電気系工学専攻                 | 2021.4.1~<br>2023.3.31 | takagi@ee.t.u-tokyo.ac.jp             |

| 5号委員 | 霜垣 | 幸浩 | マテリアル工学専攻               | 2021.4.1~<br>2023.3.31 | shimo@dpe.mm.t.u-tokyo.ac.jp          |

| 5号委員 | 鈴木 | 雄二 | 機械系工学専攻                 | 2021.4.1~<br>2023.3.31 | ysuzuki@mesl.t.u-tokyo.ac.jp          |

| 6号委員 | 中村 | 宏  | 情報理工学系研究科               | 2021.4.1~<br>2023.3.31 | nakamura@hal.ipc.i.u-tokyo.ac.jp      |

| 6号委員 | 平本 | 俊郎 | 生産技術研究所                 | 2021.4.1~<br>2023.3.31 | hiramoto@nano.iis.u-tokyo.ac.jp       |

## 3.3 決算報告

## 1. 運営費交付金

(円)

| 事 項  | 収入(予算配分)額   | 支 出 額       | 過不足額        |

|------|-------------|-------------|-------------|

| 共通経費 | 637,644,957 | 454,570,028 | 183,074,929 |

| 研究経費 | 8,205,354   | 10,302,962  | △ 2,097,608 |

| 計    | 645,850,311 | 464,872,990 | 180,977,321 |

## 2. 2022年度公的機関からの研究費

|    | 教員名 |    |                                |                                                                                                          | 委 託 者 | 研 究 課 題       | 種 類 | 受入金額(円) |

|----|-----|----|--------------------------------|----------------------------------------------------------------------------------------------------------|-------|---------------|-----|---------|

| 1  | 黒田  | 忠広 | 文部科学省                          | Agile-X〜革新的半導体技術の民主化拠点                                                                                   | 受託研究  | 1,299,999,999 |     |         |

| 2  | 黒田  | 忠広 | 国立研究開発法人 科学技術振興機構              | 積層型AIチップの低電力高効率アーキテクチャ                                                                                   | 受託研究  | 5,382,000     |     |         |

| 3  | 黒田  | 忠広 | 国立研究開発法人理化学研<br>究所             | 三次元積層 SRAM の検証と MD シミュレーション加速機構の設計評価                                                                     | 共同研究  | 29,900,000    |     |         |

| 4  | 池田  | 誠  | 電子商取引安全技術研究組<br>合(ECSEC)       | 戦略的イノベーション創造プログラム(SIP)<br>第2期/IoT社会に対応したサイバー・フィジ<br>カル・セキュリティ/(A1)IoTサプライ<br>チェーンの信頼の創出技術基盤の研究開発         | 受託研究  | 11,931,000    |     |         |

| 5  | 池田  | 誠  | 電子商取引安全技術研究組<br>合(ECSEC)       | 「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発/研究開発項目①革新的AIエッジコンピューティング技術の開発」AIエッジデバイスの横断的なセキュリティ評価に必要な基盤技術の研究開発 | 受託研究  | 10,005,000    |     |         |

| 6  | 池田  | 靓  | 国立研究開発法人 新エネル<br>ギー・産業技術総合開発機構 | AIチップ開発加速のためのイノベーション推進事業/AIチップ開発を加速する共通基盤技術の開発                                                           | 受託研究  | 1,070,598,000 |     |         |

| 7  | 池田  | 記成 | 国立研究開発法人 新エネル<br>ギー・産業技術総合開発機構 | 高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発/研究開発課題発掘のための先導調査研究/RISC-Vシステム設計プラットフォームの研究開発                       | 受託研究  | 6,913,000     |     |         |

| 8  | 池田  | 誠  | 国立研究開発法人 新エネル<br>ギー・産業技術総合開発機構 | 高効率・高速処理を可能とする AI チップ・次世代コンピューティングの技術開発/ AI エッジコンピューティングの産業応用加速のための技術開発/ RISC-V システム設計プラットフォームの研究開発      | 受託研究  | 59,995,000    |     |         |

| 9  | 池田  | 誠  | 国立研究開発法人 科学技術<br>振興機構          | Smart – Xを実現する高信頼のサイバー・フィジカル・コグニティブ・システムの構築                                                              | 受託研究  | 35,100,000    |     |         |

| 10 | 池田  | 誠  | 国立研究開発法人産業技術<br>総合研究所          | AIチップ開発を加速する共通基盤技術の開発                                                                                    | 共同研究  | 1,650,000     |     |         |

| 11 | 池田  | 誠  | 国立研究開発法人産業技術<br>総合研究所          | AI機能付デジタル・アナログ・センサ(DAS)<br>集積システムに関する研究開発                                                                | 共同研究  | 550,000       |     |         |

| 12 | 小林  | 正治 | 国立研究開発法人 科学技術 振興機構             | ナノスケール強誘電体トランジスタの研究開<br>発と機械学習アクセラレータへの応用                                                                | 受託研究  | 1,999,800     |     |         |

| 13 | 飯塚  | 哲也 | 国立研究開発法人 科学技術<br>振興機構          | リアルタイム学習推論機能創出に向けた回路<br>設計技術基盤構築                                                                         | 受託研究  | 16,146,000    |     |         |

| 14 | 飯塚  | 哲也 | 国立研究開発法人 科学技術<br>振興機構          | AIによる回路トポロジー合成を実現する高度<br>なアナログ回路設計プラットフォームの開発                                                            | 受託研究  | 15,366,000    |     |         |

| 15 | 飯塚  | 哲也 | 国立研究開発法人宇宙航空<br>研究開発機構         | 深宇宙・表面探査用ワンチップ無線機に向け<br>た研究                                                                              | 共同研究  | 550,000       |     |         |

| 16 | 小菅  | 敦丈 | 国立研究開発法人 科学技術<br>振興機構          | デバイス・システム協調による超低電圧布線<br>論理型 AI プロセッサ                                                                     | 受託研究  | 14,300,000    |     |         |

| 17 | 若林  | 一敏 | 国立研究開発法人 科学技術<br>振興機構          | MEC用マルチノード向けの総合高位合成システムの研究開発                                                                             | 受託研究  | 13,000,000    |     |         |

|     | 教員名   | 委 託 者                          | 研 究 課 題                                                                                              | 種類            | 受入金額(円)    |

|-----|-------|--------------------------------|------------------------------------------------------------------------------------------------------|---------------|------------|

| 18  | 若林 一敏 | 国立研究開発法人 新エネル<br>ギー・産業技術総合開発機構 | 高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発/研究開発課題発掘のための先導調査研究/データ構造処理を加速可能な新型計算機構の研究開発                    | 受託研究          | 16,744,000 |

| 19  | 若林 一敏 | 国立研究開発法人 新エネル<br>ギー・産業技術総合開発機構 | 高効率・高速処理を可能とする AI チップ・次世代コンピューティングの技術開発/AI エッジコンピューティングの産業応用加速のための技術開発/万能高位合成と新型汎用データフロー計算機構」に係る委託業務 | 受託研究          | 96,070,000 |

| 合 計 |       |                                |                                                                                                      | 2,706,199,799 |            |

<sup>※</sup>合計金額は、上記1~19の各課題の合計金額を記載している.

## 3. 2022年度民間企業等からの研究費

|     | 教員名 |    | 申込者                                                    | 研 究 課 題                                                                                             | 種類   | 受入金額(円)    |

|-----|-----|----|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------------|

| 1   | 黒田  | 忠広 | Taiwan Semiconductor<br>Manufacturing<br>Company, Ltd. | Read Only Memory-oriented Neuron Cell<br>Array using Non-Linear Neural Network                      | 受託研究 | _          |

| 2   | 黒田  | 忠広 | Taiwan Semiconductor<br>Manufacturing<br>Company, Ltd. | Leakage power saving 3D-stacked SRAM module for AI applications                                     | 受託研究 | _          |

| 3   | 黒田  | 忠広 | 三菱電機株式会社                                               | 基地局増幅器のための広帯域化回路技術の研究開発                                                                             | 共同研究 | _          |

| 4   | 黒田  | 忠広 | 三菱電機株式会社                                               | チップ間ミリ波信号無線伝送技術の研究(3)                                                                               | 共同研究 | _          |

| 5   | 池田  | 誠  | キオクシア株式会社                                              | ストレージシステム向け高機能暗号回路技術 の研究                                                                            | 受託研究 | _          |

| 6   | 池田  | 誠  | 株式会社アドバンテスト                                            | 先端LSI開発環境・テスティング技術                                                                                  | 共同研究 | _          |

| 7   | 池田  | 誠  | 株式会社村上開明堂                                              | ドライバー見守りシステム用セキュリティ技<br>術の研究                                                                        | 共同研究 | _          |

| 8   | 三田  | 吉郎 | 株式会社ニューフレアテク<br>ノロジー                                   | 集積回路の高密度接合に向けた微細電極形成<br>手法の研究                                                                       | 受託研究 | _          |

| 9   | 三田  | 吉郎 | 株式会社ニューフレアテク<br>ノロジー                                   | 先端MEMS構造および製造プロセスにおける<br>指導,助言                                                                      | 受託研究 | _          |

| 10  | 三田  | 吉郎 | 株式会社ニューフレアテク<br>ノロジー                                   | 三次元MEMS構造プロセスの研究                                                                                    | 共同研究 | _          |

| 11  | 三田  | 吉郎 | 株式会社アドバンテスト                                            | 集積化微小MEMSによる高機能センサの研究                                                                               | 共同研究 | _          |

| 12  | 小林  | 正治 | Taiwan Semiconductor<br>Manufacturing<br>Company, Ltd  | Channel and Interface Engineering of Ferroelectric-HfO2 FeFET for 3D integrated high density memory | 受託研究 | _          |

| 13  | 小林  | 正治 | 株式会社神戸製鋼所<br>株式会社コベルコ科研                                | 大規模集積回路応用に向けたIn-Ga-Zn-Sn-Oを用いたデバイスプロセスに関する研究                                                        | 共同研究 | _          |

| 14  | 小菅  | 敦丈 | 株式会社EX-Fusion                                          | レーザー応用に向けた外観検査技術の開発(3)                                                                              | 共同研究 | _          |

| 15  | 肥後  | 昭男 | トーカロ株式会社                                               | シリコン微小ピラーの形成プロセスに関する<br>研究                                                                          | 共同研究 | _          |

| 合 計 |     |    |                                                        |                                                                                                     |      | 84,353,064 |

<sup>※</sup>合計金額は、上記1~15の各課題の合計金額を記載している.

## 4. 2022年度寄附金

受入件数:6件 受入額 計 93,200,000円

(株式会社アドバンテスト,株式会社エフ・イー・ティー・ジャパン,株式会社ジーダット,一般財団法人電子回路基板技術振興財団,東芝デバイス&ストレージ株式会社,東京エレクトロン株式会社)

<sup>※</sup>受入金額の「-」は非公表を意味している.

## 第4章 研究報告 -各研究室-

## 4.1 全体概況

|         | 研究室構成 | 研究発表 |      |     | <b>菜∌</b> /Ⅲ\ | 特許(冊) | 巫告 (/#\ |

|---------|-------|------|------|-----|---------------|-------|---------|

|         | 人数(名) | 研究論文 | 国際会議 | その他 | 著書(冊)         | 特許(冊) | 受賞(件)   |

| d.lab教員 | 80    | 19   | 28   | 88  | 0             | 5     | 15      |

| 協力教員    | 156   | 42   | 88   | 109 | 2             | 0     | 17      |

## 4.2 研究室構成員(2022年度)

## 黒田・小菅研究室 構成

黒 田 忠 広 教授 濱 基 嗣 特任教授 田 菅 敦 丈 講師 小 丹 羽 正 昭 上席研究員 若 林 敏 上席研究員 剛 主幹研究員 高 木 野 連 也 特任研究員 Ш 和 徳 特任研究員 本 Щ 特任研究員 最 上 徹  $\stackrel{-}{\longrightarrow}$ 宮 健 生 特任研究員 四手井 綱 章 学術支援専門職員 光 岡 田 司 学術支援専門職員 Wai-Yeung Yip 学術支援専門職員 林 泰 弘 学術支援専門職員 窪 田通 孝 学術支援専門職員 王 俊 沙 学術支援専門職員 翔 午 近 藤 学術支援専門職員 柴 康 太 博士3年 Meng Haopeng 博士1年 柴田彩登 修士2年 Lixing Yu 修士2年 Yao-Chung Hsu 修士2年 修士2年 Ximing Wang 澄 川玲 修士1年 維 堂 楓 馬 修士1年 本 詹 智 杰 学部4年 内 間 典 子 特任専門職員 豊 井 弘 美 特任専門職員 大 典 子 特任専門職員 賀

## 竹内健研究室 構成

俊

介

中島幹子

越 能

内 竹 健 教授 松 井 千 尋 特任助教  $\equiv$ 澤 奈央子 学術支援専門職員 合 田 晃 博士3年 和 樋 英 博士3年  $\Box$

修士2年

特任専門職員

吉 清 秦 生 修士2年 忠 范 忠 修士2年 孫 英 皓 修士2年 歩 Щ 田 修士1年 Ш 裕 也 修士1年 市 黄 志 遠 修士1年 薛 寒 煕 修士1年 一帆王 修士1年 王 内 堅 学部4年 Щ 心 村 拓 学部4年 西 人 竜 平 学部4年 Щ П П 竜 平 学部4年 Ш 林 学部4年 小 知 幾 小 林 英太郎 学部4年

## 中村研究室 構成

村 教授 中 宏 高 瀬 英 希 准教授 島 拓 也 助教 小 上 野 洋 典 学振研究員 胡 思 已 博士3年 博士1年 岡 田 怜  $\pm$ 修士2年 山 大次郎 小 茆 黄 潤 修士2年 海 修士2年 或 分 渡 富 田 祐 永 修士2年 島 太 修士2年 中 創 志 修士2年 前 田 温 雄 修士2年 Щ 崎 輔 夏 世 修士1年 傑 齌 藤 直 修士1年 田 中 晴 亮 修士1年 棚 瀬 健 修士1年 森 学部4年 勇 介 金 沓 名 海 斗 学部4年

祐

学部4年

佐々木 大

## 池田研究室 構成

池 田 誠 教授 本 松 高 助教  $\pm$ 俊 之 吉 Ш 特任研究員 荒 川 文 男 特任研究員 繆 逸杰(Yijie Miao) 博士2年 Bayasgalan Amartuvshin 博士2年 博士2年 Zeyu Wang Anawin Opasatian 博士1年 叶 子楊(Ziyang Ye) 博士1年 Hung Quoc Bui 修士2年 (現在 NEC) 赵 寅帆(Yinfan Zhao) 修士2年 (現在博士1年)

Jiyuan Xin 修士1年 岡才 菊 人 修士1年 正 田 薫 修士1年 健太郎 小 谷 学部4年(現在佐藤研修士1年) 竹 島 優 太 学部4年(現在修士1年) 田桃 福 子 学部4年(現在修士1年)

修士2年 (現在 SONY)

修士2年 (現在 SONY)

## 飯塚研究室 構成

程

鎮宇

修士1年

部 浩太郎

慎

田 泰

島

飯 塚 哲 准教授 也 グェン ゴック マイカーン 助教 ビャムバドルジ ゾルボー 特任研究員 翔 宇 特任研究員 楊 尊 松 特任研究員 ドラン クリスティアン 特任研究員 長 田 将 博士2年 李 爍 煒 博士2年 堀 川貴 道 修士2年 岩 下 僚 我 修士2年 柴 田凌 弥 修士2年 袁 浩 晨 修士2年 郭 晟 修士2年 張 浩 明 修士2年 加 納 創 太 修士1年 陽 熊 野 修士1年 朱 玉 揚 修士1年

伊藤峻学部4年竹中理太郎学部4年和久井優斗学部4年

## 平本研究室 構成

平 本 教授 俊 郎 更 屋 拓 哉 助手 竹 内 潔 特任研究員 谷 水 朋 子 特任研究員 伊 藤 夫 特任研究員 木 特任研究員 鈴 慎 特任研究員 高 倉 俊 彦 福 井 特任研究員 宗 利 高 瀬 博 行 特任研究員 櫛 田 知 義 特任研究員 博士1年 周 翔 豪 刘 子 博士1年 姫 佩 琳 修士2年 午 金 駿 修士2年 木 大 輝 修士1年

## 小林研究室 構成

小 林 正 治 准教授 Chitra PANDY 特任研究員 李 卓 博士2年 糸 矢 祐 喜 修士2年 金 在 顕 修士2年 郝 俊 翔 修士2年 綺 修士2年 宮 雲 Deepak Ganesh Sharma 修士1年 日 掛 凱 斗 修士1年 黄 星 宇 修士1年

## 高木研究室 構成

木 信

高

トープラサートポン カシディット 講師 陳 驄 博士3年(工学系) 家 姜 旼 秀 博士3年(工学系) 博士3年(工学系) 隅 田 圭 韓 雪 揚 博士1年(工学系) 名 幸 瑛 心 博士1年(工学系) 琴 修士2年(工学系) Ш 野 麻 修士2年(工学系) 吉 遼 平 津 岩 重 宏一郎 修士1年(工学系) 修士1年(工学系) 大 友 将 樹 劉 振 泓 修士1年(工学系) 陳 修士1年(工学系) 育 同 陸 学部4年(工学部) 鈴 木 央

教授

## 竹中研究室 構成

竹 中 充 教授 唐 睿 特任助教 湯 涵 智 博士3年(工学系) 武 悠 博士2年(工学系) 宮 人 ティパットピヤパッタラクン 博士2年(工学系) 柴 成 立 博士1年(工学系) 潘 杰 博士1年(工学系) 張 超 修士2年(工学系)

城 和 修士2年(工学系) 高 馬 中 Щ 武 修士2年(工学系) 壽 明 修士2年(工学系) 黄 智 修士1年(工学系) 澤 智 熙 田将 修士1年(工学系) 藤 大 傅 晟 修士1年(工学系) 本 宙 彌 学部4年(工学部) 作 脇 田 耀 学部4年(工学部)

## 内田研究室 構成

教授 内 田 建 田 中 貴 久 助教 藤 る 学術支援職員 加 2 朗 博士2年 藤 太 加 梅 田 竜 生 修士2年 中 悠 輔 修士2年 濱 雄 修士1年 成 田 紀 NAKWARANGKUL Prach 修士1年 尾 知 寿 修士1年 宮 谷 П 雄 麻 学部4年 吉 永 啓 学部4年

## 染谷研究室 構成

染 谷 隆 夫 教授 之 横 田 知 准教授 成 講師 李 薫 川友 特任助教 多 作 葉 頼 松 重 特任研究員 Ш 島 伊久衞 学術専門職員 立 花 勇太郎 学術専門職員 泉 真 学術専門職員 小 里 和歌子 学術専門職員 雪 田 池ケ谷 智 子 特任専門職員 畄 代 特任専門職員 松 Ш 﨑 祥 子 特任専門職員 原 技術補佐員 Ŧī. 月 博士3年 程 董 凱 汪 浩 洋 博士3年

| 王   |     | 佳   | 辰     | 博士3年 |

|-----|-----|-----|-------|------|

| 杜   |     | 宝   | 才     | 博士2年 |

| 加   | 藤   |     | 裕     | 博士2年 |

| ハリム | ルティ | スクス | マンディラ | 博士2年 |

| 王   |     | 文   | 清     | 博士1年 |

| 加   | 藤   | 由太  | に郎    | 修士2年 |

| 森   |     | _   | 馬     | 修士2年 |

| ウィミ | シャヤ | テオド | ルス    | 修士2年 |

| 郭   |     | 舒   | 揚     | 修士2年 |

| 奥   | 田   | 知   | 華     | 修士1年 |

| 海老  | 经原  | 祐   | 輔     | 修士1年 |

| 徐   |     | 嘉   | 穎     | 修士1年 |

| 江   |     | 静   | 怡     | 修士1年 |

| 三   | 室   | 真   | 帆     | 学士4年 |

| 佐々  | 木   | 光   | 生     | 学士4年 |

| 宮   | 瀬   |     | 環     | 学士4年 |

| 鷲   | 見   |     | 直     | 学士4年 |

## 三田研究室 構成

| 三田吉郎              | 教授                 |

|-------------------|--------------------|

| 肥 後 昭 男           | 特任講師 (ADVANTEST    |

|                   | D2T)               |

| 黄 吉卿              | 客員研究員 (LIMMS研究所    |

|                   | /仏CNRS C2N研究所)     |

| 落 合 幸 徳           | 特任研究員 (マテリアル先端     |

|                   | リサーチインフラ事業 専任      |

|                   | マネージャ)             |

| 島本直伸              | 特任研究員 (次世代X-nics 拠 |

|                   | 点形成事業)             |

| 坪 井 伸 二           | 特任研究員 (マテリアル先端     |

|                   | リサーチインフラ事業 クリ      |

|                   | ーンルーム支援担当)         |

| 安 永 竣             | 特任研究員 (JST CREST)  |

| Anne-Claire EILER | 特任研究員 (JST CREST)  |

| 水島彩子              | 技術専門職員 (マテリアル先     |

|                   | 端リサーチインフラ事業 技      |

|                   | 術支援担当)             |

| 豊 倉 敦             | 技術専門職員 (電気系一般      |

|                   | 電子実験室, 武田先端知204バ   |

ックエンド加工室支援担当)

| 澤 | 村  | 智  | 紀       | 技術専門職員 (武田先端知        |

|---|----|----|---------|----------------------|

|   |    |    |         | クリーンルーム管理室)          |

| 太 | 田  | 悦  | 子       | 学術専門職員 (マテリアル先       |

|   |    |    |         | 端リサーチインフラ事業 技        |

|   |    |    |         | 術支援担当)               |

| 河 | 井  | 哲  | 子       | 学術専門職員 (マテリアル先       |

|   |    |    |         | 端リサーチインフラ事業 デ        |

|   |    |    |         | ィレクション担当)            |

| 渡 | 邊  | かき | とる      | 特任専門職員 (マテリアル先       |

|   |    |    |         | 端リサーチインフラ事業 事        |

|   |    |    |         | 務局)                  |

| 井 | 上  | 友里 | <b></b> | 学術専門職員 (マテリアル先       |

|   |    |    |         | 端リサーチインフラ事業 技        |

|   |    |    |         | 術支援担当)               |

| 藤 | 原  |    | 誠       | 支援員 (マテリアル先端リサ       |

|   |    |    |         | ーチインフラ事業 技術支援        |

|   |    |    |         | 担当)                  |

| 中 | 山  | 雄  | 太       | 共同研究員 (電気系, コニカ      |

|   |    |    |         | ミノルタ)                |

| 梅 | 田  | 賢  | _       | 共同研究員 (NanoHub, AGC) |

| 三 | 角  |    | 啓       | 博士1年                 |

| 山 | П  | 貴  | 史       | 修士2年                 |

| 辻 |    | 啓  | 吾       | 修士2年                 |

| 山 | 形  | 昌  | 弘       | 修士1年                 |

| 松 | 岡  |    | 朣       | 修士1年                 |

| 島 | 村  | 龍  | 伍       | 学部4年                 |

| 中 | 島  | 志  | 温       | 学部4年                 |

|   | ほカ | 3名 |         | 共同研究員                |

|   |    |    |         |                      |

|   |    |    |         |                      |

|   |    |    |         |                      |

|   |    |    |         |                      |

|   |    |    |         |                      |

## 4.3 研究概要

## 黒田・小菅研究室

(http://www.kuroda.t.u-tokyo.ac.jp/index.html)

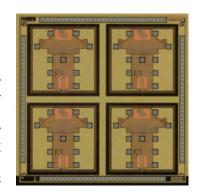

## TCI: ThruChip Interface

黒田 忠広, 濱田 基嗣, 小菅 敦丈, 四手井 綱章, 岡田 光司, イップ ウェイイェン, 柴康太

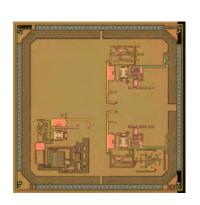

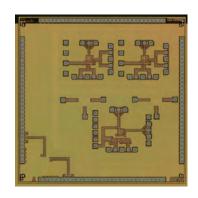

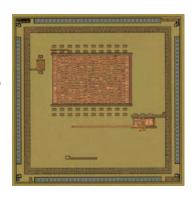

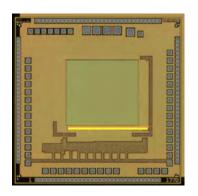

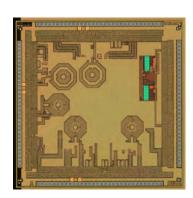

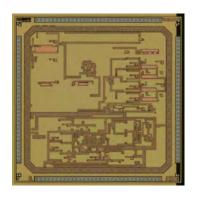

チップの配線を巻いて作ったコイルの誘導結合を用いて積層チップ間でデータ転送を行う3次元集積技術の研究を行っている。TSV(シリコン貫通電極)と同等以上の性能を低コストで実現可能である。本年度は、TCIを用いた3次元SRAM積層技術に関する発表及びそれに向けたアーキテクチャ、AI処理アルゴリズムの研究と、RaaSと共同でTCIを活用した3次元積層SRAMのテストチップの設計を行った。またTCIに向けた3次元積層の設計検証方法の基礎検討を行った。3次元実装技術についてはHotChips'22、A-SSCC'22等の国際学会にて発表を行った。

## TLC: Transmission Line Coupler

黒田 忠広,濱田 基嗣,小菅 敦丈,林 泰弘, Ximing Wang

ボード上の伝送線路の電磁結合を用いて、ボード間でデータ転送を行う技術の研究を行っている。従来型のコネクタで問題となる、摩耗、耐震性、インピーダンス整合などの問題がなく、安価で高性能な無線コネクタを実現可能である。本年度は企業との共同研究を通じ、パッケージ基板とPCBとを接続するための小型かつ高密度TLC実装技術の研究開発、そして非接触給電とTLCとを同軸配置し近接させた状態で同時通信を行う完全密封型の非接触コネクタ技術の研究を行った。特に後者においては無線給電と非接触通信との相互干渉を防ぐため、GNDシールド技術の基礎検討を実施した。研究成果はICECS'22にて口頭発表を行った。

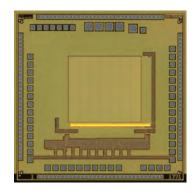

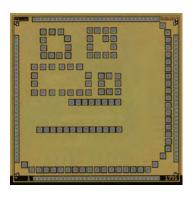

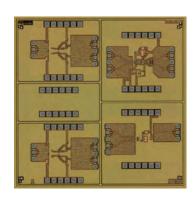

## RFID無線タグ

黒田 忠広, 濱田 基嗣, 小菅 敦丈, 柴田 彩登

1mm角以下の極小チップにアンテナと無線回路を集積した無線タグを実現し、インテリジェントなリーダと組み合わせることで通信距離を確保し、極めて安価な IoE (Internet of Everything) システムを追究する。今年度は断熱回路を活用し受信信号に基づいて決定論的に衝突を回避する新た衝突回避機能を実現し、さらに

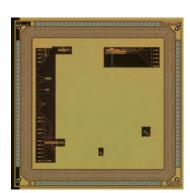

断熱論理回路自体を工夫することにより低電力化を実現した RFID タグ回路を TSMC 0.18μm CMOS プロセスで開発した。同じく RFID タグ上に実装したコイルと PCB 基板上のコイルとが磁界結合する、ボンディングレス実装技術も新たに開発した。コストの高いフリップチップ実装やボンディングが不要になる。TSMC 0,18μm CMOS プロセスでテストチップを開発評価し、SSC-Lにて論文発表を行った。

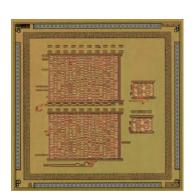

## 超低電力AIプロセッサ

黒田 忠広, 濱田 基嗣, 小菅 敦丈, 柴 康太, Yao-Chung Hsu, 澄川 玲維, 本堂 楓馬, 柴 康太, 詹 智杰

処理量の多いAIが多数社会実装されるにつれて急増 する電力消費を抑えるため、Wired-logicに着目した非 ノイマン型AI Processorを研究している. Wired-logicを 用いることでDRAMやSRAMアクセスを最小化でき電 力効率を大幅に向上できるが、膨大な素子をチップ上 に実装する必要があるため面積効率は大幅に劣化す る. そこで(1)人間の脳におけるプルーニングと呼ば れる不要なニューロンとシナプスを削除しネットワー クを最適化する技術、そして(2)従来以上に大幅にプ ルーニングし素子数を節約するため、人間のニューロ ンが持つ多種多様な非線形関数を適材適所使い分けて 演算強度を増す性質を取り入れた、非線形ニューラル ネットワーク技術, そして (3) 畳み込みアルゴリズム の処理に合わせて回路を再利用する畳み込み型Wiredlogic architecture 回路の3つの技術を開発している。本年 度は10種の一般物体を見分けるCIFAR-10のデータセッ トに対して基礎技術検討と学習アルゴリズムの開発を 行い、FPGAを用いて原理実証し、研究成果は HotChips'22にて口頭発表を行った. また省面積回路技 術も併せて開発し、手書き文字認識を題材にASICを開 発, SSDM'22および JJAPにて論文発表を行った。同時 にSRAMを用いたCompute in Memory技術も開発して おり、特にスパースな行列に対して計算効率が向上す るように行列を並び替える Polynomio アーキテクチャを 開発. NEWCAS'22で発表を行った. 本成果は高く評 価されTCAS-1の特集号に招待されている。

## ミリ波イメージングレーダ

黒田 忠広, 濱田 基嗣, 小菅 敦丈, イップ ウェイイェン, 末廣 知士

過酷環境下(悪天候、不十分な夜間照明、カメラへ の汚れ付着)では、従来の画像認識による人・物体識 別器は精度が低い課題があった。高い耐環境性を持つ ミリ波は有望であるが、画像と異なり深層学習型AI適 用には学習データ作成に課題があった. 本研究では新 規半自動学習データ生成技術を軸に、 ミリ波イメージ を扱う深層学習AI技術を新規開発し、高精度な人・物 体識別 AI 技術を開発する。本年度は主にミリ波レーダ ーのデータ特徴とそれに即したネットワーク構造の検 討,並びにカメラ-レーダー協調半自動学習データ生 成技術の開発に取り組み、6種類の物体の種類と位置を 画像認識と同等の精度で検知できるミリ波レーダーAI システムを開発した. 本成果はIEEEの測定機器分科会 のフラグシップジャーナルである, IEEE Transactions on Instrumentation and Measurement 誌に論文が採択され掲 載された.

## 竹内研究室

(https://co-design.t.u-tokyo.ac.jp/)

## Computation in memory (CiM) に関する研究

竹内健,松井千尋

Computation in Memory (CiM) はメモリアレイ構造を利用して乗算・累積 (multiply-and-accumulate: MAC) 演算を行う事が可能になる。MAC 演算はディープニューラルネットワーク (DNN) の中で最も計算資源を消費する演算である。DNNの精度を評価するシミュレータを開発した。シミュレータでは畳み込み層と全結合層における重みを任意に量子化し、重みに任意の分布に従ったばらつきを付加することや、一定の値で加減させることができる。以上により、DNNの重みを操作することでCiMメモリセルにおけるデバイスの非理想性を再現することが可能になった。

## Simulated Annealing に関する研究

竹内健,松井千尋,三澤奈央子

組合せ最適化問題の1つであるナップサック問題を、 シミュレーティッドアニーリングを用いてコンピュテ ーション・イン・メモリ (CiM) で解く場合、従来の エンコーディングはナップサック容量が増えると回路面積が線形的に大きくなるという問題があった。そこでログ・エンコーディングによるReRAMコンピュテーション・イン・メモリを提案した。提案のログ・エンコーディングは従来のエンコーディングに比べ、CiMの回路面積が97.6%縮小する。ReRAMデバイスの非対称なエラー特性を考慮し、二次形式のハミルトニアンにおけるQUBO行列の"0"をHRSに記憶することで、許容できるビット・エラー率(BER)が10倍、許容できるビット精度が5ビットまで減らすことが可能になった。

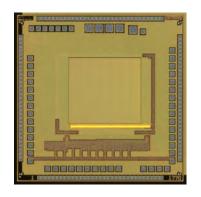

## インセンサ・コンピューティングの研究

竹内健,松井千尋

センシングのためのEvent-based vision sensor (EVS) と 統 合し 演算 する低消費 エネルギーの SRAM Computation-in-Memory (CiM)を提案した。従来のフレームカメラと比較して、EVS は画素の光の強度変化を非同期で検出し出力するため、データは空間的に疎で時間的に密という特徴がある。提案する SRAM CiM は EVS から出力されるイベントを受け取り、On-event および Off-event をそれぞれ演算する。イベントデータを演算する spiking neural network (SNN)のマルチビット重みは SRAM CiM に保存されている。提案した EVS向けの SRAM CiM は EVS のデータの特徴により、フレームカメラと比較して10<sup>-6</sup>倍のエネルギー効率を達成できた。

## 中村研究室

(http://www.hal.ipc.i.u-tokyo.ac.jp/)

## IoTネットワークセキュリティに関する研究

中村宏

Zigbee は近距離無線通信規格の一つで、転送可能距離が短く転送速度も低速である代わりに、安価で消費電力が少ないという特徴を持っており、電池で動くような小型のセンサやIoT などで幅広く使用されている. Zigbee はこの低消費電力を実現するために間接通信を採用しているため、LDoS 攻撃への脆弱性の要因ともなっている. この問題に対し、処理にさける資源が少なく許容消費電力も小さいというIoT機器の制約を満たしつつ、LDoS攻撃を防ぎ攻撃者を特定する手法

を提案した. さらに、その手法を実現するハードウェア機構を検討しその有効性を示した.

## 粗粒度再構成アーキテクチャ Coarse-Grain Reconfigurable Architecture

小島 拓也,中村宏

粗粒度再構成可能アーキテクチャ CGRA (Coarse-Grained Reconfigurable Architecture) は高いエネルギー効 率とプログラミング柔軟性という特徴を有するため, 組込みシステムから高性能コンピューティングまでの 広い応用が期待されている。CGRAは多くのPE (Processing Element) が2次元アレイ状に配置された構 成であり、その有効性は、処理をこれらのPEにマッピ ングするコンパイラの質に依存する. 我々は、このマ ッピングのフレームワークとして、遺伝的アルゴリズ ムを用いた GenMap (A Genetic Algorithmic Approach for Optimizing Spatial Mapping)という手法を提案してい る. このGenMapを空間だけではなく時間的にも再構 成可能なCGRAへ適用できるように拡張し、その有効 性を確認した. また、CGRAに近似計算を取り入れる ことで、要求精度を満たしつつ省面積かつ省電力に処 理を実現できることを示した.

## 組込みデバイス向けのROS 2ノード軽量実行環境

高瀬 英希,中村宏

ROS (Robot Operating System) 及びその後継である ROS2は、分散型のロボットシステムにおけるソフトウェア開発プラットフォームとして注目されている. ROS2の問題の1つは、動作環境としてLinuxを必要とするため、高性能で消費電力の大きい計算リソースを必要とすることである。そのため、応答性や消費電力の点で、ROS2を組み込みデバイスへ適用する際の障害となっている.

そこで組込みデバイス向けの実行環境であるmROS2の研究を行っている。mROS2の利点は、高効率な通信を実現しメモリ軽量であることである。現在、目的の実現に求められる設計要件を整理し、効率的な通信処理を実現するためのソフトウェア構成および動作フローを設計している。この研究はモバイルロボットシステムの低消費電力化とリアルタイム性の向上に貢献することが期待されている。

## 池田研究室

(http://www.mos.t.u-tokyo.ac.jp)

## 高機能暗号の設計最適化

池田 誠,Anawin Opasatian,正田 薫,福田 桃子, 竹島 優太

ペアリング暗号 (PBC) は最新の様々な暗号方式において最も重要な基盤の一つとなっている。PBCでは通常膨大な計算を伴うために高性能なアクセラレータは多くのアプリケーションにとって有用である。我々は暗号演算の最適化を目指し幾つかの曲線(非対称ペアリング:BLS12-381, BLS24-315, BLS24-317及びBLS24-509/対称ペアリング:SS1024) 上のペアリング演算を実行可能な高性能アクセラレータを設計し、IDベース暗号 (IBE)、共通鍵ベースの検索可能暗号 (SSE)、属性ベース暗号 (ABE) 等への応用も検討している。設計したアーキテクチャは Hash-to-point の高速化にも発展させている。スケジュールの自動生成による設計時間の短縮と剰余乗算器の最適化の研究も行っている。

## 完全同型暗号の実装

池田誠,島田泰慎,赵寅帆

完全準同型暗号 (Fully homomorphic encryption, FHE) は、データ処理を委任することができ、それにアクセ スすることなく処理を行う方法です。この技術は秘密 鍵を使用せずに、暗号文を計算することができます. FHEは、安全な委任計算に使用されることが期待され ていますが、現在はその計算速度が非常に遅いため、 実用的な応用には至っていません。本研究の目的は、 TFHEやBGVなどのFHEをハードウェア実装によって 高速化することです。 今年、FPGA上の実装はCPUに 比べて4倍の速さを達成しました。今後もさらなる改善 が必要です。また、FHEアルゴリズムの最適化にも注 力しています。トレードオフを数多く検討した結果、 同型論理ゲートの入力ポートの数を3から10に増やしま した. また、FHEのパラメータを最適化して、実行時 間,復号失敗率,およびセキュリティレベルを維持し ました.

## 耐量子計算暗号の実装

池田 誠, Hung Quoc Bui, 島田 泰慎, 小谷 健太郎 耐量子計算暗号 (PQC) は, 従来の計算機および量 子計算機の両者に対して攻撃態勢を有する公開鍵暗号及びディジタル署名方式となっており、量子計算機により多項式時間で解けるようになるとされているDiffie-Hellman、RSA、楕円曲線暗号を置き換えるために開発が進んでいる。標準化が進められているPQCは、格子暗号ベースのCRYSTALS-Kyber、CRYSTALS-Dilithium、FALCON、およびハッシュベースのSPHINCS+の4種類に加え、現在第4ラウンドの議論が進められている。本研究では、CRYSTALS-Kyberを65nmASICで実装したほか、SIKEおよび同種写像の基礎演算をFPGA上で実装し性能評価を行っている。

## 暗号の安全性評価

池田 誠, 阿部 浩太郎, 菊岡 才人

暗号実装はサイドチャネル攻撃耐性を持つ必要があ り、耐性評価が求められる。256ビットECDSAハード ウェア実装におけるスカラー倍算に対して実測による 消費電流波形を利用したテンプレート攻撃を行うによ ってサイドチャネル攻撃耐性を評価したうえで、有効 と思われるいくつかの対策を組み込んだ実装に関して 論理合成後の性能評価と論理シミュレーションに基づ くテンプレート攻撃の漏洩成功率の推定を行った。こ れにより対策手法ごとの有効性の評価と設計段階での 定量的な漏洩評価が可能となった。楕円曲線ペアリン グを用いた暗号回路のハードウェア実装では、十分な 安全性と可能な限り小さいコストを両立する最適曲線 の選択が重要となる。本研究では、DLP (離散対数問 題)やECDLP(楕円曲線上の離散対数問題)に対する 暗号としての安全性と、演算器面積や所要サイクル数、 演算器遅延時間といったハードウェア的観点における コストを, 有限体の標数のみを変数として見積もる手 法を提案し、BN曲線、BLS12曲線、BLS24曲線に対し て適用した結果を示した。

## ニューラルネットワークとそのセキュリティ

池田 誠, Zeyu Wang, 繆 逸杰,

Bayasqalan Amartuvshin

スパイクニューラルネットワーク (SNN) は高いエネルギー効率を実現する可能性があり、ニューロモーフィックセンサーとの統合にも期待されるため、注目を集めています。しかし、SNNのハードウェア実装は、スパイキングニューロンによって導入された膜電

位によって、大きな困難を抱えています。そこで我々は、膜電位の圧縮方法を提案し、推論精度に影響を与えずに初めて深層 SNN において膜電位を低精度固定小数点で扱うことを可能にし、同じ FPGA ベースの SNN推論アクセラレータの中で最小のリソース使用と最高のエネルギー効率を実現した。

一方、近年、ニューラルネットワークの複雑な計算 により、クラウドコンピューティングが注目されてい る. しかし、データプライバシーは、クラウドコンピ ューティングを広く応用するにおいてまだ問題となっ ている. 完全準同型暗号は、プライバシー保護する方 法として期待されているが、速度が遅いという欠点が ある。われわれは、ソフトウェアとハードウェアの両 面から、完全準同型暗号を用いたニューラルネットワ ーク計算速度を改善することに取り組んでいる。まず, FHEを用いた再帰型ニューラルネットワーク (RNN) の推論における高速アルゴリズムを設計し、時間がか かるブートストラップの回避とスループットの大幅向 上を実現した。完全剰余数系 (RNS) に基づく完全準 同型暗号向けのハードウェアにより計算は更に高速化 されることができる. 他のハードウェア設計に比べて, 完全剰余数系を利用することで、複雑な大きな数値計 算を避け、ハードウェアリソースを大幅に削減するこ とができる.

## 論理回路およびプロセッサの安全性

池田 誠,叶子楊,Jiyuan Xin,松本 高士, 荒川 文男,吉川 俊之

ロジカルロッキングは、不正アクセスやリバースエンジニアリングからデジタル回路を保護、回路の改竄や偽造を防止するために用いられる技術である.この技術は、鍵に依存する要素を回路に追加し、回路の構造やレイアウトを鍵に依存する形で変更することで実現される.従来の手法では、オーバーヘッドが大きい欠点に加え、セキュリティ上不十分であるといった課題が存在していた。本研究では、アトラクタによって制御される小空間のカオス構造を回路に挿入し、異なる鍵入力によって異なる論理演算を実現している。カオス構造の数を調整することで、セキュリティとオーバーヘッドのバランスを取ることが可能な手法として期待されている.

オープンソースの命令セットアーキテクチャ RISC-V

にポスト量子暗号化アクセラレータ統合・命令拡張することで、オープンソース ハードウェアでの公開鍵暗号化のパフォーマンスを向上の検討も行っている.

### 飯塚研究室

(http://www.mos.t.u-tokyo.ac.jp/iizuka)

#### 低雑音位相同期回路技術

飯塚哲也,楊尊松,長田将,岩下僚我

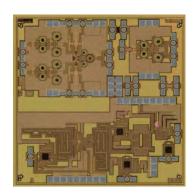

リング電圧制御発振器(VCO)は小さい面積や複数位相の出力、さらには磁気的なカップリングがないなどの利点がある。しかし5 GHzを超える低ジッタPLLの場合、ほとんどの先行研究では大面積のインダクタや磁気的な結合という課題を抱えているLC型VCOが用いられている。本研究では超低ジッタのインダクタレスカスケードPLLを提案した。第1ステージではシングルステージのサンプルアンドホールドサブサンプリング位相検出器が提案されている。この検出器ではインパルス感度関数がゼロの場合にのみ発振器の制御電圧が更新されるためループ帯域幅が広くなり、ジッタおよびスプリアスが低くなる。65 nm CMOSで試作した10 GHzで動作するプロトタイプは125MHzの基準クロックで-63 dBcのreference spur、175-fsの積分RMSジッタ、-240dBのFOMを実現した。

低ジッタおよび低スプリアスの PLL は、新たな高速 通信システムで強く求められる. 近年, 高い位相検出 ゲインを備えたサンプリング/サブサンプリング PLL は、スプリアス、ジッタ、および消費電力を同時に低 減する能力を示しており、その結果、-65dBc 未満の低 いスプリアスと-258dB未満の優れたジッタ電力指数 (FoM) を実現している。 ただし、100 fs 未満の RMS ジ ッターを達成するには、通常、低 PN で高スルーレー トのクロックを提供するために巨大なリファレンス バ ッファーが必要であり、PLL の電力効率が低下する. PLL の入力負荷と水晶発振器の消費電力を増加させる ことなく, PD の帯域内位相ノイズ (PN) を 3dB 下げ るために、低リップルのダブルサンプリング位相検出 器を備えた基準サンプリング PLL を提案した. 100 MHz の入力リファレンスを使用して、65 nm CMOS の プロトタイプは、-80 dBc のスプリアス レベルで 63 fs の RMS ジッターを達成した。 総消費電力は 3.4GHz で 3.1mW となっている.

高調波ミキサ (Harmonic-Mixer: HM) に基づいたフ ラクショナルN型PLLはキャリブレーションに頼らず に低ノイズの周波数合成を行う上で非常に有効な回路 である. 多くの場合, HM はサンプルアンドホールド (S/H) 回路における入力周波数の変換を活用して実現 され、その出力には多くの不要なトーンがある. その ためこれらを抑えるためにS/Hの前後に適切なフィル タを接続する必要がある. しかし多くの先行研究では これらのトーンの生成メカニズムやそれによるフィル タへの必要要件などが明らかにされておらず、その設 計方針も不明確な場合が多い. そこで本研究では1)ト ーンがどのように生成されるのかの定性的な説明, 2) 結果生じるトーンの位置および大きさ、そして3)ト ーンを十分に抑えるためにフィルタが満たすべき要求 性能について解析した。またこれらの解析の正しさは シミュレーション結果により裏付けられた.

リング発振器に基づくPLLはLC型発振器に基づいた それと比べて様々な利点があり、省面積や磁気的外乱 へのロバストさなどを求められる様々な応用にて有効 な回路である。またそれと同時にキャリブレーション に頼らないフラクショナルN型PLLは動作のロバスト さ, 設計の容易さ, そしてロッキング時間の短さを始 めとする利点があるためこちらも非常に有効な回路で ある. これらのことから分かる通りリング型発振器に 基づきかつキャリブレーションに頼らないフラクショ ナルN型PLLは非常に有効でかつ注目を浴びている回 路である。しかしリング型発振器とフラクショナルN 型PLLはそれぞれLC型発振器やインテジャーN型PLL と比べて大きなノイズを発してしまうため、これらを いかに抑えるかが鍵となる.そこで本研究ではHMに 基づくPLLの中に位相領域フィルタとして動作する補 助PLLを組み込むことでリング型発振器のノイズを抑 える高帯域構造およびフラクショナルN動作によって 生じる量子化雑音の抑制を同時に達成した。実装した 回路は50MHzの参照信号を用いて3.1GHz付近の信号 を生成し、-227.6dBというキャリブレーションに頼ら ないリング型フラクショナルN型PLLの中ではトップ クラスの性能指標を達成した.

ノイズシェーピングにより雑音低減を可能にした従来の2次ΔΣFDC (Frequency-to-Digital Converter) -PLLに基づき,広帯域化とより低い位相雑音の実現のためにより高次のMASH (Multi-stAge noise SHaping) 2-k FDC-

PLLを提案した。初段のADCをSAR ADC, 次段のADCをFIA(Floating Inverter Amplifier)を用いたΔΣADCとすることでMASH 2-1 FDC-PLLを設計した。65nm CMOSプロセスで設計した提案FDC-PLLでは26MHzの参照クロックで帯域内位相雑音-102dBc/Hz, FoM-230dBを実現できることをポストレイアウトシミュレーションにより示した。

# 高精度アナログ-デジタル変換回路とその自動設計技術

飯塚 哲也,李 爍煒,柴田 凌弥,張 浩明,熊野 陽,竹中 理太郎

スタンダードセルに基づくアナログ回路は、高い再 利用性, 高度な統合性, 自動化された設計との互換性, 信頼性, 安定性などの多くの利点を持つため, 現在お よび将来の研究において非常に有望である. 我々は, 標準セルに完全に基づく合成可能な逐次近似レジスタ 容量型アナログ・デジタル変換器 (SAR CADC) の新 しい設計を提案した. これにより、商用のデジタル実 装ツールを使用して自動配置とルーティング (P/R) を実行することができる. また, この設計には差動ア ーキテクチャを提案し、より広い入力範囲を持つイン バータベースの容量型デジタル・アナログ変換器 (CDAC) を利用した. 以前の研究では、MOSFETベー スのゲート電圧非依存型キャパシタに関する研究結果 を発表し、ゲート-チャネル-基板キャパシタンスのバ リエーションをチャンネル-ソース/ドレイン-基板 PNP/NPN接合容量のバリエーションを用いて補償でき ることを発見した。このコンセプトを基に、サンプリ ングと入力電圧の保持、およびDAC電圧生成の目的 で、インバータベースのゲート電圧非依存型キャパシ タを提案した. p-MOSFET と n-MOSFET のソースとド レインをインバータに接続することで、入力電圧に起 因するキャパシタンスの変動を軽減することができた. また、CDACユニットとしてインバータから抽出され たシリーズキャパシタユニットを利用する場合のDAC 電圧の直線性補償の原理を明らかにした。アナログ信 号を切り替えるために、特殊なデジタルセルやプロセ スを必要としないダミースイッチを含んだインバータ ベースのスイッチを提案した.

確率共鳴現象は非線形系においてある一定の強度の 雑音がシステムの性能に寄与するという現象であり, 様々な分野で研究・応用がなされている。この確率共鳴を逐次比較型アナログ-デジタル変換器(SAR ADC)に適用した際の有効性を検証した。SAR ADCにおいて二分探索でアナログ-デジタル変換を行う際に複数回の比較が必要になるが、提案回路では通常のSAR ADCの動作の後に追加で比較を繰り返すことによって高分解能化を図る。また、回路内の雑音を確率共鳴に用いることで、雑音抑制に通常用いられる電力を抑え、低消費電力化を図る。性能解析とシミュレーションによって追加比較回数と雑音強度の最適条件が得られ、通常のSAR ADCよりも提案回路の電力効率は高くなるという結果が得られた。

ダイナミック回路はCMOS集積回路の一種である. スタティック CMOS 回路よりも高速だが、タイミングが複雑なため特性評価が難しく、スタンダードセル設計フローでは通常使用できない。本研究では、ダイナミック回路の特性評価を実測で行うため、まず新たなダイナミック回路のタイミングモデルを提案し、次にこのタイミングモデルに基づいていくつかのタイミングパラメータを定義した。タイミングパラメータの値を取得するために、回路のシミュレーションを行い、これらの値を使用してセルのlibertyファイルを作成することに成功した。その後、スタティックタイミング分析(STA)を実行してタイミング検証を行った。より正確なタイミングモデルを得るために、ダイナミック回路特性評価に必要なタイミングパラメータを実測で評価できるテスト回路の設計を行った。

高精度・高電力効率なADC設計のために、Floating Inverter Amplifier(FIA)を用いた完全ダイナミック離散時間  $\Delta\Sigma$ ADCに関する研究を行った。昨年度から継続している Correlated level shifting(CLS)及びサンプリングノイズキャンセル技術について実測による評価を行ったほか、実測結果を踏まえ、更なる性能向上に向けた取り組みとして新たな技術を検討している。マルチビット化に必要となるディザの雑音効果を打ち消す回路構成及びより DC ゲインの高い積分器構成が求められている。

高速な無線通信や有線通信には、高速かつ高精度なアナログ・デジタル変換回路(ADC)が必要とされている。タイムインターリーブは複数のADCを並列に動作させることで変換速度を高速化する技術であり、数GS/s以上のADCには欠かせない。タイムインターリー

ブ型ADCはDCオフセットやクロックスキューなどの各ADCの特性の差により性能が悪化するため、その対策が重要となる。それぞれの誤差の要因に対して、回路動作の深い理解に基づく理論解析により最適な実装を提案し、28nm FD-SOIプロセスを用いた8チャンネル、4GS/sのADCの設計を行った。レイアウトの寄生成分や雑音を考慮したシミュレーションでは、先行研究と比較して高い161.6dBのSchreier FoMを達成した。

#### 深宇宙探査機向け低雑音受信回路の設計

飯塚 哲也, 堀川 貴道, 加納 創太

近年の小型宇宙探査機の需要に伴い、搭載されるマイクロ波帯無線通信機についても小型軽量化が強く望まれる。現行の無線通信機では民生の電子部品を用いて小型化を実現しているが、低信頼性の部品の組み合わせは、深宇宙での長期のミッション遂行の信頼性の確保を困難にする。小型化と高い信頼性を同時に達成するためには、アナログ高周波フロントエンドおよびデジタル処理回路を含めた送受信回路全体をワンチップに集積することが一つの解決策である。

深宇宙探査における集積回路設計を考える上で,受信機の雑音指数 (NF) と放射線耐性は重要な性能指標となる.遠く離れた地球からの微弱信号が雑音に埋もれるのを防ぐため,回路内部で発生する雑音をできるだけ小さくし受信感度を向上させる必要がある.

本研究では、狭帯域ノイズキャンセリング技術を使 用した7.2 GHz帯オンチップ受信機フロントエンドの 設計を行った。従来の低雑音受信機(LNA)とダウン コンバージョンミキサから成る受信回路に加え、副次 的なノイズキャンセリング経路を並列に追加すること で、LNA内のオンチップインダクタから発生する熱雑 音を打ち消すことができる。提案回路の設計は宇宙空 間における放射線の影響を受けにくい130-nm SiGe BiCMOSプロセスを用いて行った. 局部発振器とGM 回路にビヘイビアモデルを用いた回路図レベルでのシ ミュレーションにより、室温において受信機全体で1.03 dBのNFを達成できることを確認した. これはノイズ キャンセリングを行わない主経路のみの場合と比べて 1.61 dB 改善した値である。また、LNA に与えるバイア ス電圧を適切に校正することにより探査機内の温度変 化に対する性能補償が可能であることを示した.

## 時間領域ニューロン素子の設計・実装とそれらを用い た学習システムの検証

飯塚 哲也,陳 翔宇,ビャムバドルジ ゾルボー,ドラン クリスティアン,伊藤 峻,和久井 優斗