# 巻頭 センター長挨拶

# 第1章 VDEC 概要

# 1.1. VDEC 組織概要

VDECは平成8年度に専任教官5名事務官1名で発足したが、平成9年度に専任教官2名と事務官1名が増員された.さらに、全国の大学と提携を密にする目的で、各大学から2年を単位として2名の教官をVDECに派遣する「流動ポスト制度」が平成9年度からスタートした、平成10年度までは東北大学

と横浜国立大学からそれぞれ1名ずつ、平成11年度からは広島大学と金沢大学からそれぞれ1名ずつ派遣されている。また産業界と協力を行うため、客員教授(I種)が1名おかれている。平成10年度のVDECスタッフは表1のとおり10名の教官と2名の事務官から構成されている。

### 表 1 VDEC定員関係

### (平成10年度)

|           | 连 員<br>(平成8年度) | 進 員<br>(平成9,10年度) | 備 考<br>(平成16年度スタッフ) |

|-----------|----------------|-------------------|---------------------|

| 教授        | 2              | 2                 | 鳳.浅田                |

| 客員教授 (1種) |                | 1                 | 家田                  |

| 助教授       | 2              | 3                 | 平本,池田(講師),中田(助手)    |

| 流動助教授     | -              | 2                 | 羽路, 小谷              |

| 助手        | 1              | 2                 | 韓, 鄭                |

| 事務官       | 1              | 2                 | 松本,清水               |

| 핚         | 6              | 12                |                     |

# 1.2.人事報告

## VDEC 人事

センター長(教授)鳳 紘一郎

教 授 浅田邦博

客員教授 家田信明(平成11年3月まで)

客員教授 田中正文(平成11年4月着任)

助 教 授 平 本 俊 郎

助 教 授 羽 路 伸 夫(平成11年3月まで)

助 教 授 小 谷 光 司(平成11年3月まで)

助 教 授 北 川 章 夫(平成11年4月着任)

助 教 授 小 出 哲 士(平成11年4月着任)

講師 池田 誠

助 手 鄭 若 彤

助 手 伊 浩(平成11年4月着任) 助 手 中 田 明 良(平成11年10月まで)

事務主任 衛 松 本 直 会計掛長 清 水 要

紘一郎 鷹

浅田 邦博

家田 信明

田中 正文

平本 俊郎

羽路 伸夫

小谷 光司

北川 章夫

小出 哲士

池田

誠

韓 小逸

若书 鄭

浩 伊藤

中田 明良

松本 直衛

清水 要

#### 4

# 運営委員会構成(平成10年度)

| 委 | 員 | 長 | 鳳 | 糸 | 太 — | 郎 | 東京大学大規模集積システム設計教育研究センター長 | 教  | 授         |

|---|---|---|---|---|-----|---|--------------------------|----|-----------|

| 委 |   | 員 | 吉 | 田 | 善   | 章 | 東京大学工学系研究科システム量子工学専攻     | 助  | 教授        |

|   | " |   | 浅 | 田 | 邦   | 博 | 東京大学大規模集積システム設計教育研究センター  | 教  | 授         |

|   | " |   | 平 | 本 | 俊   | 郎 | 東京大学大規模集積システム設計教育研究センター  | 助孝 | <b>教授</b> |

|   | " |   | 南 | 谷 |     | 崇 | 東京大学先端科学技術研究センター         | 教  | 授         |

|   | " |   | 宮 | 永 | 喜   | _ | 北海道大学工学系研究科電子情報工学専攻      | 教  | 授         |

|   | " |   | 大 | 見 | 忠   | 弘 | 東北大学工学系研究科電子工学専攻         | 教  | 授         |

|   | " |   | 或 | 枝 | 博   | 昭 | 東京工業大学工学部電気・電子工学科        | 教  | 授         |

|   | " |   | 上 | 田 | 和   | 宏 | 芝浦工業大学システム工学科電子情報システム学科  | 教  | 授         |

|   | " |   | 柳 | 沢 | 政   | 生 | 早稲田大学理工学部電子・情報通信学科       | 教  | 授         |

|   | " |   | 鈴 | 木 | 正   | 或 | 金沢大学工学部電気・情報工学科          | 教  | 授         |

|   | " |   | 島 | 田 | 俊   | 夫 | 名古屋大学工学系研究科電子情報学専攻       | 教  | 授         |

|   | " |   | 田 | 丸 | 啓   | 吉 | 京都大学工学研究科電子通信工学専攻        | 教  | 授         |

|   | " |   | 谷 | П | 研   | = | 大阪大学工学部電子情報エネルギー工学専攻     | 教  | 授         |

|   | " |   | 岩 | 田 |     | 穆 | 広島大学工学部第二類(電気系)          | 教  | 授         |

|   | " |   | 安 | 浦 | 寛   | 人 | 九州大学システム情報科学研究科情報工学専攻    | 教  | 授         |

|   |   |   |   |   |     |   |                          |    |           |

# 協議会構成(平成10年度)

| 協  | 議                                       | 員  | 鳯 | 紘 | _ | 郎 | 東京大学大規模集積システム設計教育研究センター長  | 教  | 授         |

|----|-----------------------------------------|----|---|---|---|---|---------------------------|----|-----------|

|    | ″                                       |    | 中 | 島 | 尚 | 正 | 東京大学工学系研究科長               | 教  | 授         |

|    | ″                                       |    | 浅 | 田 | 邦 | 博 | 東京大学大規模集積システム設計教育研究センター   | 教  | 授         |

|    | ″                                       |    | 神 | 谷 | 武 | 志 | 東京大学工学系研究科電子工学専攻          | 教  | 授         |

|    | "                                       |    | 田 | 中 | 英 | 彦 | 東京大学工学系研究科電気工学専攻          | 教  | 授         |

|    | ″                                       |    | 岡 | 部 | 洋 | _ | 東京大学先端科学技術研究センター          | 教  | 授         |

|    | ″                                       |    | 荒 | Ш | 泰 | 彦 | 東京大学国際・産学共同センター           | 教  | 授         |

| オブ | ゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙゙ | ľ– | 吉 | 田 | 善 | 章 | 東京大学工学系研究科システム量子工学専攻,総長補佐 | 助教 | <b>섳授</b> |

# 1.3.決算報告

### 1.平成10年度経費

| 人  | 件    | 費        | 96,350,145円  | 講 | 師 | 等  | 旅  | 費 | 1,007,000円  |

|----|------|----------|--------------|---|---|----|----|---|-------------|

| 職  | 員 旅  | 費        | 983,000円     | 共 | 同 | 研  | 究  | 費 | 14,880,000円 |

| 校  |      | 費        | 257,276,000円 | 諸 |   | 謝  |    | 金 | 609,200円    |

| (電 | 算機借料 | 196,6    | 42,000円を含む)  | 受 | 託 | 研乡 | こ員 | 費 | 812,000円    |

| 施  | 設整係  | <b>黄</b> | 199,500,000円 | 科 | 学 | 研  | 究  | 費 | 86,400,000円 |

### 2. 平成10年度科学研究費補助金

| 研 究<br>代 表 者 | 研 究 題 目                       | 種類        | 金額     |

|--------------|-------------------------------|-----------|--------|

|              |                               |           | 千円     |

| 浅田邦博         | 二次元情報即時処理システム                 | 特定領域研究(1) | 24,700 |

| 浅田邦博         | 大規模集積回路設計データの知的検証に関する研究       | 基盤研究A(2)  | 30,600 |

| 鳳 紘一郎        | ナノシリコンデバイスのための近接ダブルショットキー     | 基盤研究B(2)  | 6,100  |

|              | MOSFETの研究                     |           |        |

| 平本俊郎         | リソグラフィ限界を超えた制御性の良いシリコンデバイ     | 基盤研究B(2)  | 6,300  |

|              | スの作製に関する研究                    |           |        |

| 浅田邦博         | 新しい同期概念を用いたマイクロプロセッサアーキテク     | 基盤研究B(2)  | 9,600  |

|              | チャの研究                         |           |        |

| 平本俊郎         | 量子効果を積極利用した薄膜 SOI MOSFET の性能向 | 基盤研究B(2)  | 5,900  |

|              | 上とばらつき低減の研究                   |           |        |

| 平本俊郎         | 量子ドットにおけるクーロン閉塞現象を利用した双安定     | 萌芽的研究     | 2,200  |

|              | 状態の発現に関する研究                   |           |        |

| 池田 誠         | 大規模集積システムのチップインターフェースにおける     | 奨励研究A     | 1,000  |

|              | 消費電力削減に関する研究                  |           |        |

|              |                               |           |        |

|              |                               |           |        |

|              |                               |           |        |

|              |                               |           |        |

|              |                               |           |        |

### 3 . 平成10年度奨学寄付金

以下の企業から寄附をいただきました.

日立製作所,日産自動車,三菱電機,日本電気,富士通,スティッチング基金 受入額 計 9,870,820 円

# 第2章 平成10年度 VDEC 事業報告

平成10年度も平成8年度、平成9年度に引き続きチップ試作の安定的運営、CADソフトウエアの配布・運用、およびホスト計算機の運用により「LSI教育情報の発信拠点」「VLSI設計支援教育用CAD

ソフトウエアの整備」「VLSIチップ試作支援」の 3つの柱の円滑な運営を目指した事業を展開した。 以下に平成10年度の事業の概要を報告する。

演習用ワークステーション25台

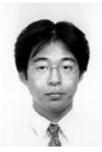

### 図2.1 サーバ計算機、セミナー用のワークステーションおよびネットワークの構成

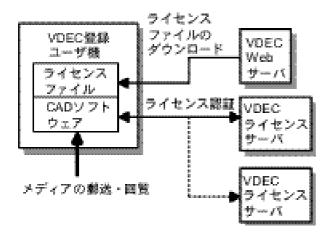

VDECにおけるVLSI設計教育情報の発信拠点、CADライセンスサーバ、VLSIチップ設計データ処理、およびCAD利用技術、VLSI設計技術セミナーに用いるのために平成8年度に導入したサーバ計算機は、4筐体で構成されており、1筐体を情報発信・ライセンスサーバ、1筐体をVLSI設計

データ処理、2 筐体を全国のVLSIチップ申込者の設計データ収集と設計検証のために運用している(図2.1参照)。本サーバ計算機の利用は、原則としてVDECにおけるチップ試作を前提とし、VLSIチップ試作申込者は、各自の計算機でVLSI設計を行っても、VDECのサーバ計算機で設計を行って

もよいが、最終的にはこのアカウントを用いて サーバ計算機に設計データを転送し、VDEC指定 の最終検査プログラムで検証処理を行った後、 VDECに対し設計データを「提出」する。

また、セミナー用ワークステーション 25 台は、 VDEC開催のセミナーのうち東京会場で開催され たものに用いるほか、設計関係の授業・演習、およ びVLSIの設計のために利用されている。

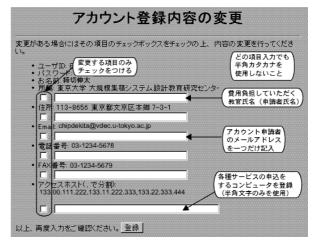

#### 【Webページの整備】

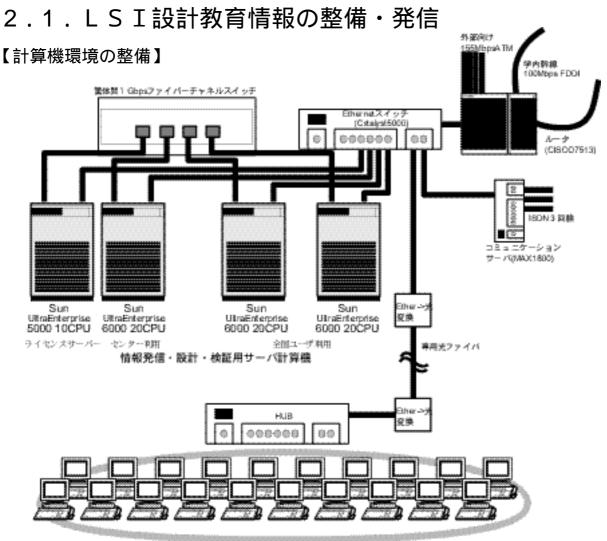

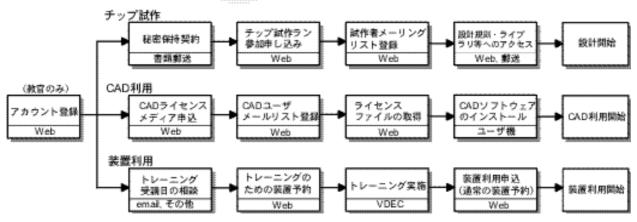

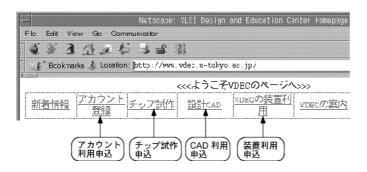

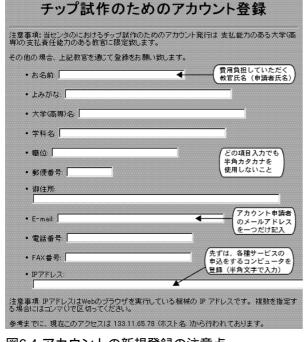

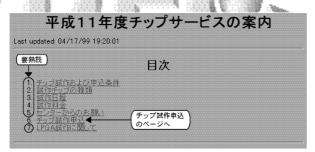

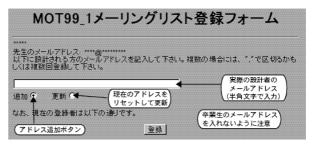

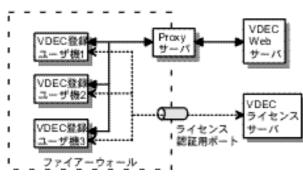

VDECの情報発信の多くはWebを介したものとなっており、また各種利用等の申し込みはすべてWebによるものを原則としている。Webページの構成は図2.2の通りで、それぞれの申し込み、提供情報の内容に応じてアクセス制限を行っている。詳細は第6章「付録」を参照されたい。

### 図2.2 VDECのWebベージ構成

#### 【教材の整備】

VLSI設計法の教材整備では、平成9年度に作成した「論理合成・シミュレーション検証(上流設計)」「セルベースによる自動配置配線(中流設計)」「会話型設計(下流設計)」の教材を、CADツールのバージョンアップにあわせて内容の更新を行な

うとともに、新たに「マクロセル作成のための自習 教材」の作成を行なった。本年度からは、これらの 教材はすべて電子的に配布することとし、全国の 教育関係者が研究・教育目的に自由に改定再配布 が出来るようにした。

# 2.2. CADソフトウエアの整備

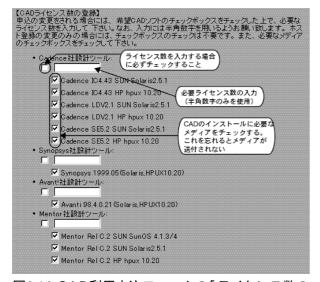

平成8年度に導入されたCADソフトウエア(表2.1)は、図2.3に示す全国地域拠点校10箇所にライセンスサーバを設置し、各大学の利用者が最寄りのライセンスサーバにおいて認証を行うことでCADツールが利用できるようなネットワークを利

用した運用形態となっている。ライセンス数は CADの項目ごとに500から1000程度のフローティングライセンスとなっており、全国の大学・高専において教育・研究目的に限り利用できるよう制限を行っている。

# 表2.1 導入された CADシステム

| 項目              | 用 違                           | メーカ                   |

|-----------------|-------------------------------|-----------------------|

| Verilog HDLを用いた | Verilog HDLベースの入力、シミュレーション、論理 | Cadence Design        |

| 設計システム          | 合成、テスト生成                      | Systems, Inc.         |

| VHDLを用いた設計シ     | VHDLベースの入力、シミュレーション、論理合成、     | Synopsys, Inc.        |

| ステム             | テスト生成                         |                       |

| 自動配置・配線設計シ      | マクロセルを含むセルベースの配置配線設計とバック      | Avant! Co.            |

| ステム             | アノテーション                       |                       |

| 会話型設計システム       | 会話型の回路図およびマスクレイアウト入力、設計       | Mentor Graphics, Co., |

|                 | 検証、回路抽出、回路シミュレーション            |                       |

| アナログ設計システム      | アナログ機能・回路シミュレーション、回路図入力、      | Cadence Design        |

|                 | レイアウト設計、設計検証、回路抽出             | Systems, Inc          |

図2.3 全国地域拠点校

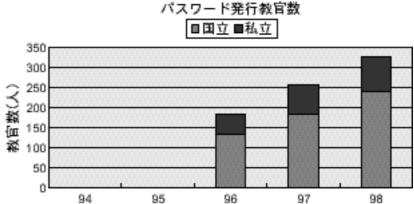

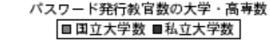

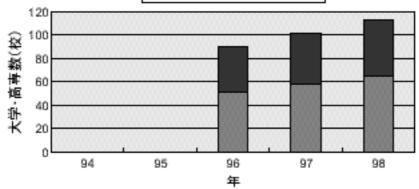

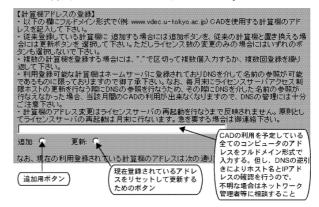

VDECのCADの利用、および後述のチップ試作の利用のためにはあらかじめユーザ登録が必要となっているが、これまでVDECに利用登録している全国教官数およびその所属する大学数およびCADの利用申請があった研究室(教官)数の推移は図2.4の通りである。

年

図2.4 ユーザ登録数およびCAD申込数の推移

### 【CADソフトウエア利用状況】

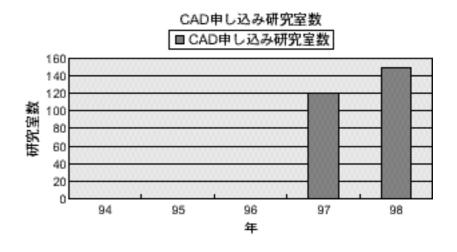

平成10年度までのCADツールの利用状況の推移を図2.5に示す。なお、図2.5は東大および拠点校のライセンスサーバが認証を行なった回数で、申込数だけでなく利用実績も増大していることが

わかる。ただし、97年度は拠点校のライセンス認 証数の調査を行っていないことや、ツールによっ て認証方法が異なるためツール間の利用頻度の比 較は単純には行ななうことは出来ない。

#### ライセンス認証数の推移

図2.5 CADの利用状況の推移

### 【セミナー開催状況】

平成10年度には9月および2、3月に、東京、名古屋、金沢、広島、東北の各地区でCADツール利用法・ライブラリー利用法のセミナーを企画実施した(表2.2)。また、12月には本年度からの新たな試みとして、各大学の教官および企業の一線の設計者を講師として、社会人向けのリフレッシュセミナー(表2.3)を開催したほか、9月に大学若手教官・学生を対象としたVDEC LSIデザイナーズフォーラムを実施している。デザイナーズフォーラムは平成9年度に続き2度目の開催で、大学若手教官・学生が互いの研究成果だけでなく、

研究会などでは聞くことの出来ないチップ設計上の苦労した点、失敗例とその解決策などの情報を共有することで、互いの親睦を深め、大学間・研究室間の連携を深めることを目的としており、平成10年9月5-6日にかけて九州大学および志賀島休暇村において開催され、72名参加という盛況であった。また、本フォーラムは平成11年度以降はIEEE/SSCS/Tokyoの後援が予定されている。また、日本学術振興会第165委員会が主催する「VLSI設計・夏の学校」への協賛も行ない、こちらも120名参加という盛況であった。

### 表2.2 平成10年度のセミナー開催状況

| 講習項目          | 会場    | 開催日                 | 参加<br>人数 | 講習機要                                                                                       |

|---------------|-------|---------------------|----------|--------------------------------------------------------------------------------------------|

| Cadence<br>上流 | 東京大学  | 平成10年<br>9月7日-9日    | 36       | 論理シミュレータVerilog-XL、配置配線<br>ツールCell Ensambleの利用法説明、実習                                       |

| Cadence<br>下流 | 東京大学  | 平成10年<br>9月10日-11日  | 39       | レイアウトエディタVirtuosoの基本的な<br>使い方。Divaを用いた設計規則検査、回<br>路シミュレータSpectreを用いた回路シミ<br>ュレーション手法の説明、実習 |

| Synopsys      | 東京大学  | 平成10年<br>9月16日-18日  | 33       | 論理合成ツールDesign Compiler、論理シ<br>ミュレータVSSの利用法説明、実習                                            |

| Avant!        | 東京大学  | 平成10年<br>9月24日-25日  | 24       | 配置配線ツールAquariusXOの利用法説<br>明                                                                |

| 東大版ラ<br>イブラリ  | 東京大学  | 平成10年<br>9月12日      | 31       | 東大VDECにおいて作成したライブラリ<br>を用いた設計フローの説明、実習                                                     |

| Avant!        | 名古屋大学 | 平成11年<br>2月1日-2日    | 20       | ApolioXOを用いた配置配線、フロア?<br>プラン、バックアノテーションの説明実<br>習                                           |

| Avant!        | 広島大学  | 平成11年<br>3月30日-31日  | 14       | ApolloXOを用いた配置配線、フロア?<br>ブラン、バックアノテーション、他社ツ<br>ールとのインターフェース                                |

| Synopsys      | 金沢大学  | 平成11年<br>3月16日-17日  | 25       | 論理合成ツールDesign Compilerの基本的<br>な利用法説明、実習                                                    |

| Cadence       | 東北大学  | 平成11年<br>3月29日-4月2日 | 25       | Cadence利用者講習会(Layout/Artist系,<br>SKILL, Verilog)                                           |

# 表2.3 社会人向けリフレッシュセミナー実施状況

| 講習項目            | 開催日                 | 譜師                                                                   | 参加<br>人数 | 講習概要                                                 |

|-----------------|---------------------|----------------------------------------------------------------------|----------|------------------------------------------------------|

| VLSI設計の<br>基礎   | 平成10年<br>12月2日-4日   | 浅田(東大・教授)、今井(阪<br>大・教授)、国枝(東工大・教<br>授)、越智(広島市大・助教<br>授)、一色(東工大・助手)   | 66       | VLSIの基礎講義、UNIXの使<br>用法、VerilogHDL, レイアウ<br>トエディタの使用法 |

| デジタル集積<br>回路演習  | 平成10年<br>12月8日-10日  | 池田(東大・講師)、小林(京<br>大・助手)                                              | 34       | VerilogHDLを用いたFPGA<br>の設計演習                          |

| アナログ集積<br>回路演習  | 平成10年<br>12月15日-16日 | 小野寺(京大・助教授)、小<br>谷(東大・助教授)                                           | 43       | レイアウト設計、設計検証、<br>回路シミュレーション                          |

| 最先端VLSI<br>設計事例 | 平成10年<br>12月24日-25日 | 安浦(九大・教授)、岩田(広<br>大・教授)、服部(日立)、飯<br>田(東芝)、松澤(松下)、石<br>原(NTT)、菊池(ソニー) | 63       | デジタルLSI設計の実例、ア<br>ナログ回路方式と設計、アナ<br>ログ・デジタル混載設計       |

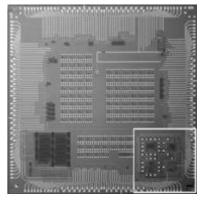

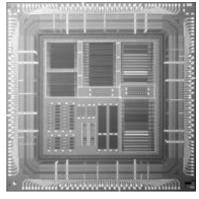

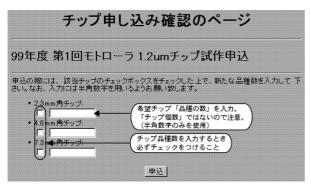

### 2.3. VLSIチップ試作状況

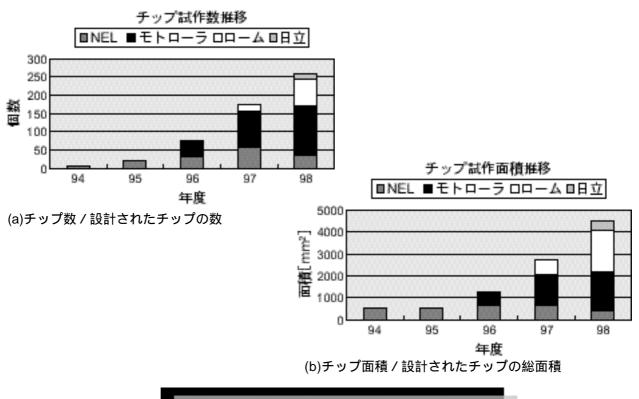

図2.6はVDECおよびそれに先行する通産省のパイロットプロジェクトでのチップ試作数の推移を示したものである。

図2.6(a)は設計されたチップ数の増加傾向を示しており、図2.6(b)は設計面積の増加傾向を示している。平成6,7年度(1994,1995年度)のパイロットプロジェクトでは,ファウンドリはNEL1社であったが,平成8年度(1996年度)のVDEC発足後,日本モトローラが協力を開始し、平成9年度(1997年度)からはこれにロームが加わった,さら

に平成10年度には日立製作所が加わったことで、 試作品種数、試作面積ともに依然として増加傾向 にある。これらとは別にLPGA(レーザでプログラ ムするゲートアレイ)の試作も始まりつつあり、平 成8年度から平成9年度にかけて、先駆的に3大学 が設計試作をおこなっている。

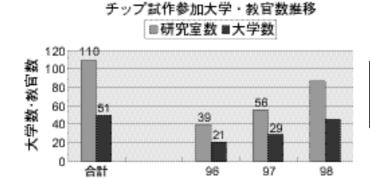

また、図 2.7 にこれまでに試作に参加した教官数、大学数の推移およびその累計を示す。この図より、すでに100を越える教官がチップ試作を行なっていることがわかる。

# 図2.6 VDECチップ試作実績の推移

年度

図2.7 VDECチップ試作参加 教官数・大学数の推移とその累計 また、チップ試作に必要な設計規則等の試作会社 固有の機密情報にアクセスするための「秘密保持 契約」締結教官数はNELが51名、日本モトローラ が79名、ロームが71名、日立が18名となっている。 以下、平成10年度のチップ試作概況、ライブラリ整備状況、新規ファウンドリーのためのチップ試作テストラン、IP開発のためのテストランの実施状況を述べる。

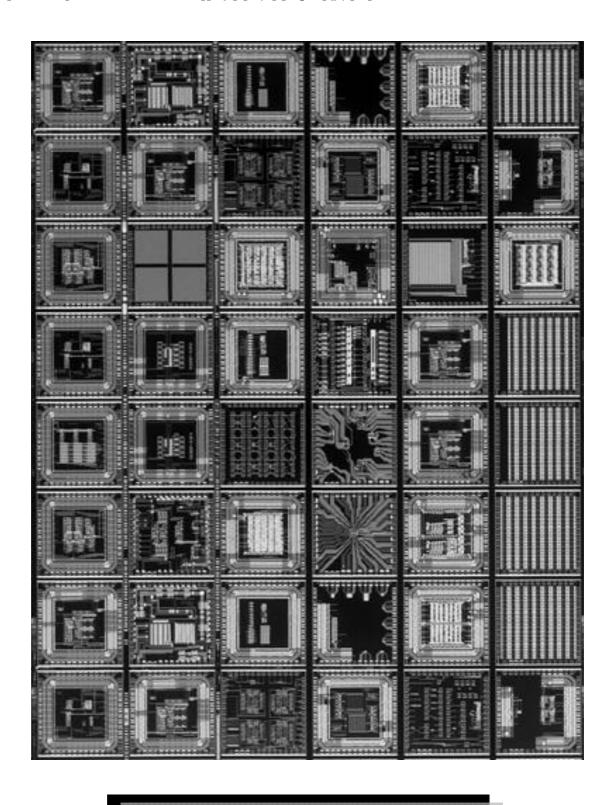

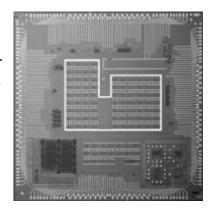

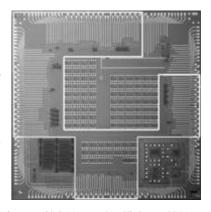

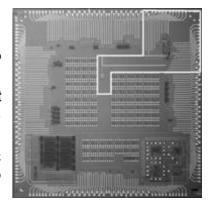

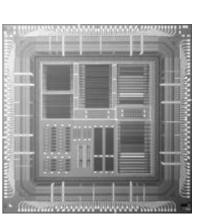

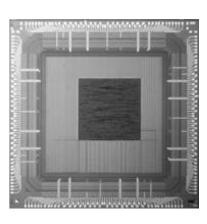

### 【平成 10 年度チップ試作概況】

平成10年度は表2.4に示す日程でチップ試作を 行った。チップ試作の参加者・試作の内容は、第5 章のチップ試作者報告を参照されたい。

# 表2.4 平成10年度チップ試作日程

| プロセス          | 設計維切       | チップ納品       |

|---------------|------------|-------------|

| CMOS0,5μm 第1回 | 平成10年5月11日 | 平成10年9月20日  |

| CMOS1.2μm第1団  | 平成10年7月10日 | 平成10年12月10日 |

| CMOS1.2μm第2回  | 平成10年9月1日  | 平成11年1月5日   |

| CMOS1.2μm第3同  | 平成11年2月10日 | 平成11年6月(予定) |

| CMOS1,2μm第4回  | 平成11年4月1日  | 平成11年7月(予定) |

| CMOS0,6μm第1回  | 平成10年8月20日 | 平成10年12月10日 |

| CMOS0,6μm第2回  | 平成11年1月8日  | 平成11年3月15日  |

| CMOS0.6µm第3间  | 平成11年3月10日 | 平成11年6月(予定) |

| CMOS0.35μm第1同 | 平成11年1月22日 | 平成11年5月7日   |

### 【ライブラリ整備状況】

2.2節で述べたVDEC提供のCADソフトの中に、ライブラリ生成ツールが含まれており、これを利用して平成8年度から順次ライブラリー整備事

業を行ってきている。現状ではVDECにおける各プロセスの試作において使用可能なライブラリは表2.5に示す通りとなっている。

### 表2.5 プロセス毎のライブラリ整備状況

| プロセス           | 名称                     | 作成者                                                                                                                                                                                          | 内容                                                                                                              | 状況                                |  |  |

|----------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

|                | P2lib                  | 京都大学 田<br>丸・小野寺研<br>究室 ・ Synopsys用論理合成ライブラリ<br>・ VerilogXL用シミュレーションライブラリ<br>・ CellEnsamble用配置配線ライブラリ                                                                                         |                                                                                                                 | 試作チップの<br>動作検証完了                  |  |  |

|                |                        | http://www.vde                                                                                                                                                                               | c.u-tokyo.ac.jp/DesignLib/P2lib/NEL05/index.html                                                                |                                   |  |  |

| NEL0.5 μ m     | EXDlib                 | <ul> <li>・Synopsys用論理合成ライブラリー・VerilogXL用シミュレーションライブラリー・VHDL用シミュレーションライブラリー・AquariusXO(ApolloXO対応済み) 用配置配線ライブラリー・CellEnsamble用配置配線ライブラリー・CellEnsamble用配置配線ライブラリー・CellEnsamble用配置配線</li> </ul> |                                                                                                                 | 動作検証中                             |  |  |

|                |                        | http://www.vde                                                                                                                                                                               | e.u-tokyo.ac.jp/DesignLib/Kyushu/NEL05/index.htm                                                                | ml                                |  |  |

|                | P2lib                  | 京都大学 田<br>丸・小野寺研<br>究室                                                                                                                                                                       | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・CellEnsamble用配置配線ライブラリ                                      | 試作チップの<br>動作検証完了                  |  |  |

|                |                        | http://www.vde                                                                                                                                                                               | c.u-tokyo.ac.jp/DesignLib/P2lib/MOT15/index.html                                                                |                                   |  |  |

| MOT1.2μm       | EXDlib                 | <ul> <li>・Synopsys用論理合成ライブラリ</li> <li>東京大学</li> <li>・VerilogXL用シミュレーションライブラリ</li> <li>・AquariusXO(ApolloXO対応済み) 用配置配線</li> <li>ライブラリ</li> </ul>                                              |                                                                                                                 | 動作檢証中                             |  |  |

|                |                        | http://www.vdec.u-tokyo.ac.jp/CHIP/DesignRule/MOT15/rule.html                                                                                                                                |                                                                                                                 |                                   |  |  |

|                | EXDlib                 | 豊橋技科大<br>田所・川人研<br>究室                                                                                                                                                                        | 田所・川人研 ・CellEnsamble用配置配線ライブラリ                                                                                  |                                   |  |  |

|                |                        | http://www.vdo                                                                                                                                                                               | ml                                                                                                              |                                   |  |  |

| ROHM0.6        | EXDlib                 | 東京大学<br>VDEC                                                                                                                                                                                 | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・AquariusXO(ApolloXO対応済み)用配置配線<br>ライブラリ                      | 動作檢証中                             |  |  |

| μm             |                        | http://www.vdec.u-tokyo.ac.jp/CHIP/DesignRule/ROHM06/rule.html                                                                                                                               |                                                                                                                 |                                   |  |  |

|                | バスポ<br>ートラ<br>イプラ<br>リ | -                                                                                                                                                                                            | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・VHDL用シミュレーションライブラリ<br>・ApolloXO用配置配線ライブラリ<br>・RAM, ROMモジュール | ロームから提<br>供                       |  |  |

|                |                        | CDROMICTA                                                                                                                                                                                    | CDROMにて配布                                                                                                       |                                   |  |  |

|                | EXDlib                 | 東京大学<br>VDEC                                                                                                                                                                                 | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・ApolloXO用配置配線ライブラリ                                          | 動作検証中                             |  |  |

|                |                        | http://www.vdo                                                                                                                                                                               | c.u-tokyo.ac.jp/CHIP/DesignRule/HIT35/rule.html                                                                 |                                   |  |  |

| 日立0.35 $\mu$ m | 日立ゲ<br>ートア<br>レイ       | -                                                                                                                                                                                            | ・Synopsys用論理合成ライブラリ<br>・VerilogXL用シミュレーションライブラリ<br>・ApolloGA用配資配線ライブラリ                                          | 日立から提供<br>のセル<br>をApolloGAに<br>移植 |  |  |

|                |                        | CDROMITT                                                                                                                                                                                     | 己布                                                                                                              |                                   |  |  |

|                |                        |                                                                                                                                                                                              |                                                                                                                 |                                   |  |  |

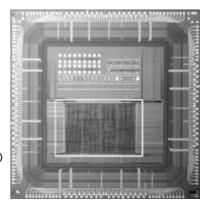

### 【新規プロセスのためのチップ試作テストラン】

平成11年度から予定している日立製作所のチップ試作サービス開始に先駆けて、平成10年度にセルライブラリの整備、設計手法の整備のためのテストランを実施した。テストランは表2.6に示す日程で行われた。本テストランの参加者および試作

内容は表2.7, 2.8に示すとおりである。なお、本テストランの試作内容に関しては第5章チップ試作結果報告も併せて参照されたい。なお本プロセスは平成11年度以降は短TATのゲートアレイに特化して実施することを予定している。

## 表2.6 日立製作所テストラン日程

| 日 時         | 内<br>容                             |

|-------------|------------------------------------|

| 平成10年6月24日  | 日立製作所デバイス開発センターにおいて試作の進め方についての打合せ  |

| 平成10年7月3日   | 設計規則受領・守秘契約取り交わし                   |

| 平成10年7月15日  | 設計規則等の詳細打合せ                        |

| 平成10年8月3日   | チップサイズ、パッケージおよび試作の流れに関する打合せ        |

| 平成10年8月20日  | ゲートアレイ等のセル情報受領                     |

| 平成10年9月14日  | 設計関係の最終打合せマスク関係の打合せ                |

| 平成10年10月下旬  | セルベース設計用上流ライブラリのユーザへの展示            |

| 平成10年11月26日 | 設計および、設計後のアクセサリ組み込みなどに関する打合せ       |

| 平成10年12月中旬  | セルベース設計用配置配線ライブラリの開示               |

| 平成11年1月上旬   | ライブラリのApolloXO対応                   |

| 平成11年1月22日  | 設計締切                               |

| 平成11年       | またでの10~ なのはあり 3.~ なのセ☆エ            |

| 1月22日~2月5日  | 東大でのIOデータのはめ込み、データの検証              |

| 平成11年       |                                    |

| 2月5日~2月22日  | 日立製作所におけるGDSデータの検証、東大でのデータ修正、マスク変換 |

| 平成11年       | フラカルボーイルデ集中体                       |

| 2月22日~4月下旬  | マスク作成、チップ製造                        |

| 平成11年5月上旬   | チップ納品                              |

# 表2.7 日立製作所テストラン参加者

| 参加大学名                                                                                    | 参加教官名                                |

|------------------------------------------------------------------------------------------|--------------------------------------|

| ・東京大学<br>・北海北大学<br>・北東京本学<br>・東京都大学<br>・京都大学<br>・神戸島州大学<br>・九州稲田大学<br>・大和田業大学<br>・芝浦工業大学 | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |

# 表2.8 日立製作所テストラン試作内容あよび使用ツール一覧

| 試作内容                                                                                                                                                                                                                                                                                                                                                                                                                                  | 使用ツール                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| ・ApolloGAを用いたゲートアレイ配置配線設計フロー評価用チップ ・パラメータ取得用デバイス評価TEG ・パストランジスタロジックを用いた基本ロジック回路、ULSIデバイス における低消費電力化を指向した降圧回路とその制御系回路 ・多値集積回路:電流モード多値回路と多値CAM ・Signed-Weight数系に基づくディジタル信号処理用FPGA ・容量パラメータ及びNQSモデルバラメータ抽出用TEG ・低消費電力乗算器の評価チップ ・Verilog-HDLを用いた構造化リカレントニューラルノードの設計 ・クラスタリングネットワークチップ ・高速ウェーブレット変換チップ ・暗号処理用プロセッサ(ISIT-DLX) ・マルチプロセッサ用のスケジューリング支援ハードウェアを搭載したプロセッサ ・データパスのレイアウトとプロセッサの消費電力の関係を調べるTEG ・乗算器、乗加算器およびALU搭載チップ試作 ・画像処理LSIのTEG試作 | Virtuoso,<br>Design<br>Compiler,<br>ApolloGA,<br>ApolloXO,<br>Verilog-XL,<br>VSS,<br>MaxPlusH,<br>DraculaDRC,<br>HSPICE |

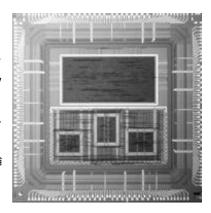

### 【IP開発のためのチップ試作テストラン】

平成10年度は、前述の新規プロセスのためのテストランに加えて、大学における設計の効率化・設計再利用の促進を目指したIP/マクロセル開発のためのテストランを、ローム0.6 µmプロセスを用いて行なった。参加者および試作内容は表2.9

2.10の通りで、検証が終わり次第成果が公開されることを期待している。なお、本テストランの試作内容に関しても第5章チップ試作者報告も併せて参照されたい。

# 表2.9 IP開発のためのテストラン参加者

| 参加大学名                                                  | 参加教官名                                                                                                                                                                                                       |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ・東京大学<br>・豊橋技術科学大学<br>・京都大学<br>・大阪大学<br>・広島大学<br>・九州大学 | <ul> <li>・浅田 邦博</li> <li>・浅田 邦博</li> <li>・旭田 八 野寺 正 田田 八 野井 正 田田 世界</li> <li>・今日 田 神 を 一 日田 神 を 一 年 で 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ 村 上 ・ ・ 村 上 ・ ・ ・ ・</li></ul> |

# 表2.10 IP開発のためのテストラン試作内容一覧

#### 試作内容

- ・フォトディテクターアレイ

- ・終了予測型加算器TEG

- ・センスアンプを用いたCPL回路方式TEG

- ・クロック信号発生用PLL回路

- ・浮動小数点演算器の設計

- ・CMOS rail-to-rail オペアンプ

- ・周波数シンセサイザ(PLL)

- SRAMおよびPLL評価用TEGチップ

- ・逆離散コサイン変換回路

- ・高速ウェーブレット変換チップ

- ・全差動型ΔΣAD変換器

- ・オーバーサンプリングADC用くし型デジタルフィ ルタマクロ

- ・オーパーサンプリングADC用アナログセルおよび32b並列加算器

# 第3章 研究報告

# 3.1.研究室構成員(平成10年度)

#### 鳳・藤島研究室

学部 4 年 (現在大学院浅田研究室) 鳳 紘一郎 教授 中島 祐介 藤島 実 助教授 藤田 隆史 学部 4 年 (現在大学院鳳・藤島研究室) 増田 太郎 北澤 清子 助手 学部 4 年 (現在大学院吉岡研究室) 出原 優一 小逸 助手 韓 学部 4 年 (現在大学院濱田研究室) 辻田 達男 博士3年(現在ザイン) 村上 義則 受託研究員(日産) 天川 修平 義男 博士2年(現在ケンブリッジ大学へ留学中) 宋 研究員(現在韓国) 福岡 哲也 修士2年(現在日立製作所) 大内 真一 修士2年(現在鳳研究室博士課程) 平本研究室 相原祐一郎 修士1年 平本 俊郎 助教授 修士1年 木庭 優治 更屋 拓哉 技官 松浦 修士1年 外国人研究員 研 施 毅 アマリア・ガルニエ 今村 晃 学部 4 年 (現在大学院鳳研究室) 外国人研究員 中澤 仁章 トラン ゴック デュエト 博士 3年(現在NTTドコモ) 学部 4 年 (現在大学院小田研究室) 林 勇樹 石黒 仁揮 学部4年(現在通産省) 博士3年(現在東芝) 平林 雅之 学部 4 年 (現在大学院桜井研究室) 高宮 真 博士2年 大口 康弘 研究員(日立製作所)

#### 浅田・池田研究室

浅田 邦博 教授 池田 誠 講師 鄭 若彤 助手 鈴木 真一 技官 吉柳 稔 博士3年(平成10年10月卒業 現在日産) 伊藤 浩 博士3年(現在東京大学VDEC助手) 三堂 哲寿 博士 3 年 (現在Avant!) 喬 健 博士2年 山下 高廣 博士2年 小松 聡 博士1年 瀬戸 謙修 修士2年(現在浅田研究室博士課程) 根塚 智裕 修士2年(現在浅田研究室博士課程) 青木 秀行 修士1年 星野 将史 修士1年

犬飼 貴士 修士2年(現在平本研究室博士課程)

間島 秀明 修士2年(現在平本研究室博士課程)

高橋 信義 修十1年 小宇羅 寛 修士1年

安田 有里 修士1年(中央大学からの研究生)

永田 英次 学部 4 年 (中央大学からの研究生)

王 海寧 研究生

### 羽路研究室 (横浜国立大学)

羽路 伸夫 助教授

ポンケオ・チャンタマリー 博士3年

新居 尚憲 修士2年(現在日立ソフトウェア)

西尾 正裕 修士2年(現在日立ソフトウェア)

荒川 太郎 助手(現在講師)

高林 俊介 修士1年

安藤 太郎 学部 4 年 (現在大学院羽路研)

石橋 崇 学部4年

海野 直久 学部 4 年 (現在大学院羽路研)

加藤紗和子 学部4年(現在日立ソフトウェア)

渡辺 充剛 学部4年

毛利 重信 学部4年

李 相國 研究生 (ソウル市立大学大学院)

### <u>小谷研究室</u>

小谷 光司 助教授

(東北大学工学部の大見研究室と共同で研究)

#### 家田研究室

家田 信明 客員教授

(NTTエレクトロニクズ(株))

### 3.2.研究概要

# 鳳・藤島研究室

1.極限集積システムのハード・アーキテクチャ 鳳紘一郎,藤島実,韓小逸,大口康弘,平林雅之

集積回路の高密度化に伴い、システムレベルでの信頼性を確保することが重要な課題となる.我々はVLSIを、シリコンだけでなく配線、層間絶縁膜の複合材料から成る積層系としてとらえ、ハード面とシステムレベルの特性を一体とした検討を行っている。本年度は赤外線温度測定装置を用いて、我々が試作したCMOSリングオシレータを動作させた時の温度分布と時間変化の測定に着手した。また光によるクロック供給の実験を行い、クロック用受光回路が600MHzで動作可能であるとの見通しを得た。

2.ショットキー接合ソース・ドレインを用いた SOI MOSFET

鳳紘一郎, 藤島実, 福岡哲也, 松浦研, 中澤仁章

極限的な短チャネル化を目的としてソースとドレインにショットキー接合を用いたMOSFETの開発を行っている、ソース、ドレインをTiシリサイドによるショットキー接触として高抵抗p-SiのSOI基板上でNiゲートによるpチャネル形とCrゲートによるnチャネル形の動作を実現させ、同一基板上でウェルなどを要さずに、ゲート金属を使い分けるだけでCMOSが構成できる見通しを得た.

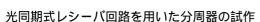

#### 3.カオス集積回路

鳳紘一郎, 藤島実, 北沢清子, 辻田達男, 相原祐一郎, 今村晃

前年度に引き続きCMOSカオスマルチバイブレータの試作と解析を行い、実測のローレンツプロットを回路の動作によって正確に説明できる理論式を得たほか、この素子を結合した場合の動作の検討に着手するとともにランダム信号源としての特性をも評価した。またパイプライン型ADコンバータを、各段ごとの反復一次元写像(ベルヌーイシフト形)によって時系列カオスを発生する回路として捉え、カオスが持続する条件と写像関数のパラメータ、さらにAD変換精度との関係を検証して、カオス持続の成否によって判定しながら変換精度を向上させる回路調整法のアルゴリズムを提唱しその効果を実証した。

Hard Architecture for Ultimate VLSI

Hoh, M. Fujishima, X.-Y. Han, Y. O'guchi, and

Hirabayashi

Regarding VLSI as the multi-layered system with composite materials including interconnection and interlayer dielectrics, the approach with materials, hard ware and system descriptions unified is of great importance. This year, spatial distribution and temporal changes of temperature was measured with the IR thermometer for the CMOS ring oscillator we have fabricated. Besides, the chip including light receiver circuit was designed for the optical distribution of clocks and its operation at 600 MHz was experimentally observed.

2. SOI MOSFET with Schottky-Contact Source/Drain K. Hoh, M. Fujishima, T. Fukuoka, K. Matsuura, and N. Nakazawa

MOSFETs on SOI utilizing Schottky contacts at their source anddrain were developed aiming the realization of ultimately shortchannel length. Tisilicide was used for source/drain and p-channel devices were fabricated with Ni gate while Cr gate realized n-channel. This promises the fabrication of CMOS by simply selecting gate metals on the same substrate without introducing well structure.

3. Integrated Chaos-Generating Circuits K. Hoh, M. Fujishima, S. Kitazawa, T. Tsujita, Y. Aihara, and A.Imamura

Amongthechaos-generating circuits of compacts tructure we have developed, the operation of the CMOS chaos multivibrator (CMV) was analyzed in detail and the equation which accurately explained the experimental Lorenz plot was established. The characteristics of the random signal source using CMV was experimentally examined and the coupled operation of CMVs was also investigated. Besides, the chaos-generating nature of the pipelined AD converter was studied. The relationship between the sustainability of chaotic output, the shape of the return-map function and the conversion accuracy as an AD converter was clarified. Based upon this, the algorithm of adjustment of the pipelined AD converter for the maximum conversion accuracy was demonstrated which utilized the sustainability of the chaotic output as monitor.

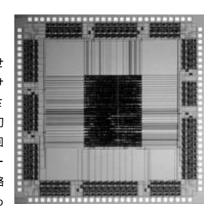

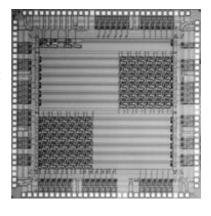

### 4.マイクロヒューマンセンサー 藤島実,鳳紘一郎,木庭優治

4. Micro Human Sensor M. Fujishima, K. Hoh, and Y. Kiniwa

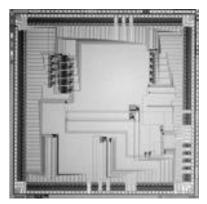

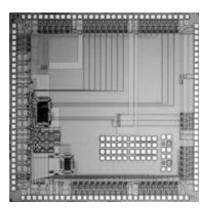

健康の維持管理に用いるための、心拍・体温などの情報を長期間記録するマイクロセンサーの研究を行っている。小型バッテリーと半導体メモリーを用い長期間記録するためには、データの高圧縮率だけでなく低消費電力が要求される。我々は、身体情報の中で急激に変化する情報が特に重要であることに着目し、重要度の低い小さな揺らぎの中から急激な変化点を抽出するアルゴリズム、Band Runlength (BRL)コーディングを考案した。BRLでは、平均値を算出するデータ数を2のべき乗に限定することにより、消費電力を増加させる乗算および除算の必要がない。0.6 μ mCMOSプロセスを用いて試作したチップでは、400kHzのクロック周波数においてわずか30μWの消費電力を実現できる。

Micro sensors for long-term recording of the human information such as heart rate and body temperature are studied in order to monitor human health. Low power as well as highcompression are required for a long-term recorder using a small battery and a semiconductor memory. Since rapid and large change in the body information is more important than slow andsmallone, we have proposed a new algorithm, named Band Runlength (BRL) coding, which extracts large change from small fluctuations in the input signal. Neither multiplier nor divider consuming much power is necessary in BRL because the number of data to calculate section average is restricted to the power of two. The fabricated chip for BRL coding using 0.6  $\mu$  m CMOS process consumes only 30  $\mu$  W at 400kHz clock frequency.

5. 単電子エレクトロニクスの応用 藤島実,鳳紘一郎,天川修平,大内真一,林勇樹 5. Application of Single-Electron Devices and Circuits M. Fujishima, K. Hoh, S. Amakawa, S. O'uchi, and Y. Hayashi

単電子トンネリングの応用に関してデバイスと回路の両面を考慮に入れつつ研究を行っている。本年度は単電子メモリについて、鏡像電荷の効果を考慮に入れたデバイスモデルの定式化を行い、またトンネル障壁のポテンシャル形状の動的変化を取り入れた計算法を確立して、従来提唱されているいくつかの回路の正しい動作を明らかにした。さらに単電子メモリのうちフラッシュ型ならびに直接トンネル型について動作の解析を厳密に行い、特に後者については読み書き時間と保持時間がチャネル抵抗ならびに蓄積ドットへのトンネル抵抗で決定される様相の解析を行って、動作条件を明らかにした。

A device model of the single-electron memory was formulated with the image-charge effect taken into account. The exact calculation was conducted incorporating the dynamical change of the tunnel barrier. This provided the correct description of the features of hithertoproposed circuits. Detailed analysis was made regarding to the effects of channel- and tunneling resistance on the read/write and retention times of the direct-tunneling memory.

6 集積回路による量子コンピューティングのエミュレーション 藤島実 , 鳳紘一郎 , 大内真一 , 天川修平 6. Emulation of Quantum Computing by Using Integrated Circuits

M. Fujishima, K. Hoh, S. O'uchi, and S. Amakawa

量子状態の重ね合わせと干渉を利用して大規模な因数分解やファイル検索を多項式時間で実行できると期待されている量子コンピューティングを,工学上現実的なハードウェアで実現する道を探るために,フーリエ変換回路を用いて量子ビットを周波数スロットに割付け,周波数領域で状態の重ね合わせとユニタリ変換を実行するエミュレーション方式の検討を行っている.

Quantum computing is a novel computation scheme that is expected to execute large volume computation such as factoring within a polynomial time by using the superposition of quantum states and their interference. To seek the way to realize this by using present-day VLSIs, an emulation engine was proposed which executed superposition of states and their unitary transformation by Fourier-transforming them into frequency domain.

### 浅田・池田研究室

1 . SOI MOSFET及びGTBT パワーデバイスの検討 浅田邦博, 伊藤浩, 村上義則

SOI MOSFETのサブスレッショルド係数に着目し,膜厚及びキャリア濃度等のデバイスパラメータを同定する手法を検討した.

サブスレッショルド係数のバックゲート特性において、完全空乏型SOIデバイスに特有な谷状の特性を示すことを明らかにした.

断面TEM観察の結果,サンプル間の膜厚揺らぎを含め本 手法による同定結果が妥当であることが確認された.フィッ ティング誤差解析による本手法の妥当性の検討も行った.

GTBT(Grounded-Trench-MOSassistedBipolar-modeFET) という新しいパワーデバイスを提案した。この素子はノーマリオフ型の新型高耐圧パワー素子で,オン抵抗の低さ,スイッチングの高速性という点でIGBTなど既存のデバイスを凌駕し,高温環境でもこの特性は劣化せず,安全動作領域も広い。GTBTは単位セルが複雑な立体構造をしており,各部分の寸法・距離が特性に大きく影響する事を解析的および,デバイスシミュレーションにより明らかにした。また,移動度など物理定数の結晶方位依存性も特性に影響を与えることを確認した。

2. VLSI 中の信号線・電源線の最適化 浅田邦博, 伊藤浩, 青柳稔, 三堂哲寿, 青木秀行, 中島祐介

多層配線における容量行列を直接抽出するテスト構造を 提案した.本テスト構造では,各容量に流れ込む電流を直接 測定することが可能であるため,誤差の要因となる測定値 から容量値を導く演算を必要としない.測定と検証の結果, 本手法はフェムトファラッドオーダーでの測定が可能であ ることが示された.

相互接続配線内の信号伝送における誘導要素の影響に関して,表皮効果を考慮した評価を行い,表皮効果が出現する高周波においては,自己インダクタンスが線路インピーダンスの支配要因になり,表皮効果はその2次的効果としての効果に留まることを明らかにした.

複数のトランジスタが同時に遷移することによる,電源電流の変動が,電源線の抵抗成分RIやインダクタンス成分L(dI/dt)といった電源電圧変動をひき起こす.この変動により,論理エラーや信号伝搬遅延の増加といった問題が生じるため,設計の段階で電源電圧変動を抑制する必要がある.電源電圧変動を解析するにあたり,電源線で発生するノイ

1. Studies on SOI MOSFETs and GTBT Power Devices K. Asada, H. Ito, and Y. Murakami

Wehavedevelopeda methodonextracting device parameters of Fully-Depleted SOI MOSFETs using sub-threshold slope factor versus backgate voltage characteristics. We explained the valley feature of the characteristics curve especially in FD-SOI MOSFETs.

The extracted parameters by our method has a good agreement with TEMobservation results even when there are fluctuations of film thickness of SOI layer and buried oxide layer. We also discussed the accuracy of the fitting results which have very small fitting errors.

GTBT(Grounded-Trench-MOSassisted Bipolar-mode FET) is a novel high-voltage power device which has a low on-state resistance and a high switching speed compared with other devices.

GTBT is a current-driven type like BJT, and has a high currentgain.

We have found that the main effect comes from the complex 3D-geometry of GTBT cell by analyses and simulations. However, the experimental results are still two times higher than those from calculations. The rest major effect is supposed to come from the anisotropicality of the carrier mobility or lifetime.

2. Interconnections and Power Supply Line Optimization in VLSI

K. Asada, H. Ito, M. Aoyagi, T. Mido, H. Aoki, and Y. Nakashima

We have been studying a test structure for direct extraction of component capacitance matrix for the multi-layer interconnections. With this new method, component capacitance can be directly obtained from the measurement data without any calculation which may cause the degradation of significant digits. As a result, we are able to measure components capacitance matrix with a precision of femto-farad order.

Moreover, we have evaluated the magnitude of inductive effects onpropagation delay in VLSI system with taking skin effect into account. As a result, we conclude that in such a high frequency operation asskine ffect appears, inductance will become the dominant factor of interconnection characteristic impedance while skine ffect will play a secondary rollindelay time characteristics.

Currentchangesinsimultaneouss witchingtransistors will cause voltage fluctuation noise in power supply line, which may destroy the logical information or may increase the signal delay.

ズを測定するためのチップを設計試作し、測定により電源線の電圧を ,時間分解能2ns ,電圧分解能20mV以下で測定できることを確認した.

3.パストランジスタを用いた回路方式の検討 浅田邦博,山下高廣,増田太郎,宋義男

nMOSトランジスタをスイッチとして使うパストランジスタ回路は低消費電力と高速化の可能性が期待されている.パストランジスタ回路の信号電圧回復回路としてセンスアンプを用いた回路において,キャパシタを介してパストランジスタとセンスアンプを接続した回路を提案する.演算毎にパストランジスタ回路の各ノードをGndにディスチャージすることで低振幅を保ちパストランジスタのVgs電圧を確保することでトランジスタのgmの高い領域のみで動作させる.

一方 たンスアンプは感度の高い1/2 Vdd付近にて動作させるため,キャパシタにて電位レベルを変換し信号電位のみ伝達させる.このキャパシタはセンスアンプが動作する際にパストランジスタの負荷を軽減する役割も果たす.このキャパシタにはトランジスタのゲート容量を用いた.

提案回路を用いた8bitパリティージェネレータ回路の試作を行い,測定結果から,従来のCMOS回路より約1.7倍速く動作することを示した。また,提案回路は電源電圧が低下した場合にも高速に動作することが分かった。

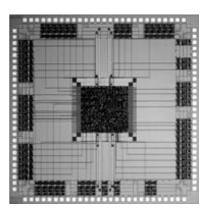

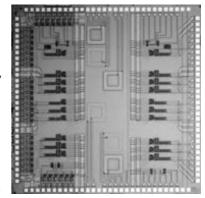

4.スマート画像センサの研究 浅田邦博、根塚智裕、星野将史,藤田隆史

センサ面上に信号処理回路を集積したイメージセンサの研究を行っている。センサ面上に,画素並列もしくは,列並列に信号処理回路を配置することにより,高速な画像処理を実現する。このような,画像センサは「スマート画像センサ」と呼ばれている。

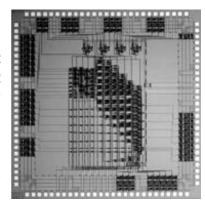

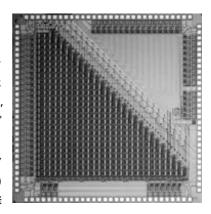

スマート画像センサの一つとして、動きベクトル検出 2 値画像センサを試作した 動きベクトルの検出は前のフレームの画像をブロックマッチングすることにより実現する センサアレイ内に構成した 2 次元シフトレジスタにより画像のシフトを行い,画素並列に配置したXOR回路により画像の比較を行う.画像の差分がもっとも小さくなる位置を検索することにより動きベクトルを検出する このセンサでは対象のサイズに合わせたブロックサイズ

We designed and fabricated the chip to measure the simultaneous switching noise on power supply line. We used voltage comparatorcircuitand measured the voltage of power supply line comparing with a reference voltage. Test of the chipshows that it could measure the voltage of power supply line with 2ns time resolution and less than 20 m V voltage resolution.

Circuit technique with Path-Transistors

K. Asada, T. Yamashita, T. Masuda, and E.N. Song

We have been studying on extended CPL (Complementary Pass-transistor Logic) for low power and high speed logic. The advantage of CPL is known as a circuit with low hard ware cost and small input capacitance due to the fact that PMOS is eliminated in the logic of the CPL.

However, CPL circuit also has disadvantages, such as a slow pull-up speed and a large power consumption at pull-up status. In this study, a method for reducing the delay time is proposed.

In CPL, we use transistors in series from Source to Drain. However, using long series transistors decreases the pull-up speed at the outputs. Thus, in case of the conventional CPL with CMOS inverters, number of the series transistors is limited by about four for high speed operation.

Conventional CPL adder has CMOS inverters as sense amplifiers at each stage. We have proposed a new circuit of sense amplifier forlow power and high speed adder.

In this circuit, a sense amplifier is placed every several CPL adders in the adder chain in order to amplify signals with small swing, while it is placed in each adder in the conventional CPL adder chain. This sense amplifier has two CMOS inverters whose inputs are connected to the other 's outputs, and the voltage of one node goes high when the another goes low.

Studies on Smart Image Sensors

Asada, T. Nezuka, M. Hoshino, and T. Fujita

We have been studying on image sensors with processing elements.

Images are processed at high frame-rate with pixel-parallel or column-parallel processing images ensors, which are so called "smart sensors".

We developed a kind of image sensor for motion vector detection, which is realized by comparing the image of previous frame and current frame. The image of the previous frame is shifted by the 2-D shift-register in sensor array and compared with the image of the current frame by XOR circuit in each pixel. The motion vector is determined by finding the location of shift with minimum difference. This sensor can vary the block-size and the search area of motion vector detection flexibly.

や 速度に合わせた動きベクトルの検索範囲を設定することが可能であり,高い柔軟性を持つのが特徴である.

三次元計測システムはコンピュータビジョン,ロボットビジョン,CG等の多くの分野での応用が考えられ,高速性と柔軟性を備えた三次元形状入力装置の開発が必要である.

本研究では 任意の矩形領域に対してブロックごとアクセスを行うことが可能なスマート画像センサを設計試作した.レーザースポットの高速ポジションディテクタとしてスマート画像センサを用いる.対象をレーザースキャナで走査し,対象に当たったレーザーのスポットの位置を連続的に特定し,センサとレーザーの位置関係から対象の三次元情報を取得する スマート画像センサによりスポットの位置の特定を高速かつ高精度に行い,システムの高速化,高精度化を図る点がこのシステムの特徴である.

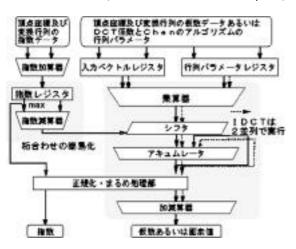

5. プロセッサシステムの高速化に関する検討 浅田邦博, 池田 誠, 鄭若彤, 小松聡, 出原優一

将来のシステムチップにおけるデータ転送のスループット向上を目指して、様々なデータ圧縮符号化手法について、データ圧縮率、回路規模、レイテンシなどの面から比較、検討を行い、システムチップに適したデータ圧縮手法の指針を示した。また、チップインタフェースを含むバスにおける消費電力削減方式として、従来から提案してきた適応型コード帳符号化方式について、一般的なバスに適合できるように符号化アルゴリズムに改良を行い、その際の消費電力削減についての検討を行った。

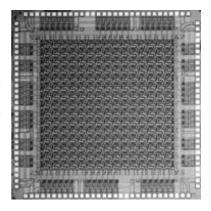

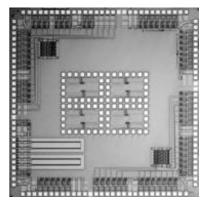

データ圧縮,画像認識等において重要である最小距離検 出回路方式として,時間領域方式の検討を行い,汎用の CAMの試作を行った.

マイクロプロセッサやDSPなどの演算処理を中心とするハードウェアにおいて、システム全体の性能に影響を与える基本ユニットは加算器である.新たに提案した終了予測加算器では、キャリーの伝搬パスを中断せずに演算を実行し、加算動作が終了次第完了信号を出すため、入力データに依存する平均動作速度を実現できる.本加算方式は、高速クロックで駆動されるシフトレジスタを用い、加算操作と並列に、最大連続キャリー伝搬距離から演算終了時間を予測し、完了信号を出力する.本方式では、従来設計した終了検出加算器と比べより速くかつ正確に演算終了時間を計算でき、従来の同期式RCA、BCLAよりそれぞれ66%、20%の平均演算速度が向上することが分かった.

3-D scan systems can be applied in fields such as computer vision, robot vision, computer graphics and so on.

In the seusage, high speed and flexibility are necessary.

In thisstudy, we have designed a smart image sensor thatcan access desired portion in the image area flexibly. We use this smart image sensor as the position detector of the laser spot in 3-Dscansystem. Thesystemscansan object using a laser beam and locates the laser spots on the surface of the object. The system obtains the 3-D information of the object using the relationship between the position of the laser device and the position of the laser spot in the image plane. The system accomplishes high speed and accuracy in 3-D measurement by locating the laser spotsquickly and accurately.

Studies on High-Speed Processors

Asada, M. Ikeda, R. Zheng, S. Komatsu, and Y. Idehara

Wehavestudiedon various data compression encoding method of future system chips, in terms of improving throughput of data transfer. Wehave evaluated some encoding methods in terms of compression rate, design size and latency, and indicated the data compression method which is suitable for system chips. Furthermore, we improved the adaptive code-booken coding method, which is proposed for low power chip interface, so that this method was adapted for general bus. We also

evaluated the power reduction with the improvedenceding method. We have studied time-domain minimum distanced etector, which can be applied to data compression and image recognition. We have implemented a general purpose CAM test chipusing the minimum distanced etector.

In dataprocessing usage such as microprocessor and DSP, adder is theunitwhichcanconsequentlyinfluencethesystem performance. The novel completion prediction adder we designed take advantage of carry signals from the operands to calculate the operation time without interfering with the addition speed. To implement this, as hift register driven by a high frequency clock is utilized to calculate the operation time from the maximum successive carry signallength. As a result average case operation speed is achieved against the worst-case speed in conventional synchronous circuits. The adder, which is designed based on RCA and BCLA, gets a 66% and 20% average case speed improvement respectively.

6 . FPGA 向け論理合成手法およびSPFDを用いた論理最 適化手法の検討

浅田邦博, 鈴木真一, 喬健, 瀬戸謙修

論理合成の中の関数分解は,従来共有関数の抽出とテクノロジマッピングの二段階で行われている.FPGA向け論理合成では,これらの関数分解を同時に行うことで効率向上が可能となる.ここでは、各出力関数の間での共有関数を最大に抽出するため,多関数分解における集合の選択、多出力関数の分割,及びグローバル関数のエンコーデングの手法を検討している.

識別対集合(SPFD)とは、山下らによって新しく発見された論理回路変形における自由度の指標である。ここでは、識別対集合による最適化手法を、マッピング後のスタンダードセルのネットリストに適用した、与えられたブーリアンネットワークの各ゲートに対し、識別対集合を適用して、そのファンインを除去、または他の配線と置き換えることによって、回路の面積と遅延を改善することを試み、山下らによるFPGAへの適用結果との比較を行うことで、スタンダードセルに対する識別対集合の最適化の効果をに関する考察を行った.

6. Logic Synthesis for FPGA and Logic Optimization using SPFD

K. Asada, S. Suzuki, J. Qiao, and K. Seto

In logic synthesis for FPGAs, functional decomposition is an effective technique to make feasibility of given networks. Especially, multiple-output decomposition technique which combines the step of common sub-function extraction and the step of technology-mapping, is considered a promising approach to FPGAs-specific logic synthesis.

We are studying on the problems of set selection, multipleoutputpartitionand global encoding for sharing more commonsub-functions among the multiple outputs.

SPFDs(SetsofPairsofFunctionstobeDistinguished)isanewly found flexibility to change logic circuits by Yamashita et al. In this research, we investigated the effectiveness of optimization using SPFDs over circuits that are mapped to logic cells in standard cell libraries.

Given a boolean network, we take each gate in it and try to remove its fan-ins or to replace them with other gates using SPFDs for optimizing area or delay. In this research, we compared our result with that of FPGAs and considered the way of improving the result.

### 平本研究室

1 .0.5V動作超低消費電力MOSFET(しきい値制御デバイス) 高宮真,小宇羅寛,平本俊郎

VLSIには低消費電力化が強く要求されており,15年後に は電源電圧が0.5V以下に低下することが予測されている. 動作電圧0.5Vではしきい値電圧も低く設定必要があり,ス タンバイ消費電力と高速性を両立させることは極めて困難と なる.本研究では,動作時とスタンバイ時でしきい値電圧を 変化させることにより両者を両立させる方式について デバ イスサイドから研究を行っている.これまでに,ゲートとボ ディを接続したDynamic Threshold MOS (DTMOS)で 基板 バイアス定数を極めて大きくできるElectrically Induced Body (EIB) DTMOS構造を提案した .SOI基板に電圧を印加する ことによりSOIバック界面に電荷を誘起しボディを形成す る 本デバイスの有用性を実験とシミュレーションにより実 証した.この成果は,1998年の国際電子デバイス会議 (IEDM)において発表を行った.一方,ウェル電位を制御す ることによりしきい値電圧をコントロールするVariable Threshold MOS (VTMOS)について スタンバイ電流を抑え つつ最も性能を向上させるための基板バイアス定数とウェル 電位の最適条件を検討している.

Extremely low power MOSFET operating at 0.5 V

Takamiya, H. Koura, and T. Hiramoto

Low power operation is essential for VLSI devices. It is predicted that the operation voltage will be reduced down to 0.5 V in 15 years. In 0.5 V operation, the threshold voltage should be very low and it will be very hard to attain both high speed and low stand-by current. In this study, we investigate the optimal deviceparameters for the variable threshold voltages chemes. We have proposed electrically induced body (EIB) dynamic threshold MOSFET (DTMOS) where the body effect factor is extremely high. The large voltage is applied to the SOI substrate to induce carriers and the body region is formed in the back interface. Highperformanceoperation has been demonstratedby experiments and simulation. This idea was presented in 1998 International Electron Devices Meeting (IEDM). The optimal device conditions are also investigated for variable thresholdvoltageMOS(VTMOS) wherethethresholdvoltage is controlled by well potential.

### 2. 不純物の統計的ゆらぎ 安田有里,高宮真,平本俊郎

デバイスの微細化に伴い、チャネル空乏層中の不純物数が減少するため、統計的な不純物数の揺らぎによりデバイスのしきい値電圧ばらつきが増大することが予測されている。また、デバイス中の不純物数が同じでも実際には不純物の分布は一様ではなく、不純物が存在する位置によってもしきい値電圧はばらついてしまう。本研究では、SOIMOSFETについてシミュレーションを行い、しきい値電圧はらつきにおける不純物の数と位置の効果を分離することにより、不純物の位置の効果が微細化とともにどのように増大するかについて検討した。その結果、デバイスが適正にスケールされた場合には、不純物位置のばらつきによるしきい値電圧ばらつきの絶対値は増大するものの、不純物数の効果に対する割合は一定に抑えられることが明らかとなった。また、不純物位置の効果は、短チャネルMOSFETのチャージシェア係数で決定されることを明らかにした。

### 3.極微細MOSFET の物理 更屋拓哉,トラン ゴック デュエト,平本俊郎

部分空乏型SOI MOSFETの最大の課題は基板浮遊効果である.基板浮遊効果の代表例であるパスゲートリークにつき,過渡電流のゲート電圧依存性を測定することによりそのリーク機構を検討し,バイポーラ電流よりサブスレッショルド電流の方が支配的であることを初めて明らかにした.一方,チャージポンピング法を用いることにより,これまで困難であったSOI構造の酸化膜界面を正確に評価する新手法を開発した.パルスバイアス電圧をボディに印加し形状効果を抑制する.この方法により,SOI界面準位のエネルギー分布および空間分布も測定可能であることを実験により実証した.

### 4.ゲート酸化膜厚のスケーリング限界 犬飼貴士,平本俊郎

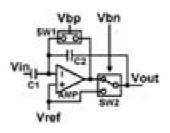

MOSFETのゲート酸化膜厚は性能向上のため薄膜化が進んでいるが、ゲート酸化膜厚が3nmを切るとゲートトンネル電流が発生しスタンバイ電流が増大してしまう.そのため、ゲート酸化膜厚のスケーリング限界は1.5 - 2.0 nm程度と言われている.本研究では、極薄膜ゲート酸化膜の利点を最大限に生かすため、回路によりゲートトンネルスタンバイ電流を抑制する方式を提案し、ゲートトンネル電流によるスタンバイ電力が必ずしもゲート酸化膜厚のスケーリングリミットを決定しないことを示した.

#### 2. Statistical impurity fluctuations

#### Y. Yasuda, M. Takamiya, and T. Hiramoto

As the device size is scaled down, the number of impurity atomsinchanneldepletionlayer is reduced and the impurity number fluctuations are enhanced, thus enhancing the threshold voltage fluctuations. Even when the channel impurity number is the same, threshold voltage will be fluctuated by the random impurity position distribution. In this study, the effects of the number fluctuations and position distribution are separated in the simulation, and the influence of position distribution has been investigated. It is found that the threshold voltage fluctuations by the position distribution will be larger but the contribution ratio by the position will remain constant when the device is properly scaled. It is also found that the effect of the impurity position distribution is well explained by the charge share model.

#### 3. Physics of scaled MOSFET

#### T. Saraya, T. N. Duyet, and T. Hiramoto

One of the most serious problems in partially depleted SOI MOSFETs is the floating body effect. We have investigated the mechanisms of dynamic pass leakage current. It is found that the dominant current is subthreshold current rather than bipolar current by measuring the gate voltage dependence of pass leakage. On the other hand, we have developed a new chargepumping technique to measure the interface statedensity of SOI MOSFETs. The pulse voltage is applied to the body to suppress the geometric component. The energy distribution and spatial distribution are successfully measured by this technique.

#### 4. Scaling limit of gate oxide thickness

#### T. Inukai and T. Hiramoto

The thickness of the gate oxide in MOSFETs is becoming thin-ner for higher performance. However, the stand-by power consumption by the gate tunnel leak age current will be come dominant when the gate oxide is thinner than 3 nm. Therefore, it is considered that the scaling limit of gate oxide is about 1.5 - 2.0 nm. In this study, we have proposed a new circuit where the gate tunnel stand-by current can be suppressed and showed that the scaling of gate oxide is not limited by the stand-by power.

### 5 . 極微細MOSFETにおける量子効果 間島秀明 , 平本俊郎

高濃度にドープされたMOSFETや極薄膜SOI MOSFETでは、キャリアの面内閉じこめにより量子効果が起こり、しきい値電圧が上昇することが知られている。本研究では、極狭チャネルMOSFETにおいては、キャリアが面内のみでなく横方向にも閉じこめられ、さらに強い量子効果が起こることを実験とシミュレーションにより実証した。実験では、チャネル長が20nm以下の極狭チャネルMOSFETを試作し、チャネル長が10nmを切る領域で、しきい値電圧が急激に上昇することを確認した。また、シミュレーションにより狭チャネルMOSFETの電子状態を計算し、しきい値電圧の上昇が量子効果によるものであることを明らかにした。

### 6.シリコン単電子デバイスの物理 石黒仁揮,高橋信義,平本俊郎

将来のVLSIデバイスへの応用を考慮して,Siにおいて極 微細構造を作製し,単一電子現象の物理の探究を行ってい る.単一電子現象は,化合物半導体や金属においてよく研究 されているが,我々は当初からシリコンを材料に用いVLSI への整合性を考慮したアプローチをとってきた 現在ではシ リコンナノデバイスは広く研究されるようになったが 我々 の研究はその先駆的な研究のひとつに数えられる.まず,リ ソグラフィに依らず微細なSi細線構造(線幅10nm以下)を作 製するプロセスを開発した .SOI基板に異方性エッチングと 選択酸化を施すことにより、SOI膜厚に応じた線幅の細線構 造が作製される.この構造をチャネルとする極微細 MOSFETを試作し,室温においてクーロンブロッケード振 動の観測に成功している.また,高温で動作するシリコン単 電子デバイスでは シリコンドットにおける量子効果が重要 な役割を果たすことを明らかにし 量子効果による特性のば らつきを補償する新しい単電子デバイス構造を提案した .こ れらの成果は1998年の国際電子デバイス会議(IEDM)におい て発表を行った シリコン極微構造においてシリコンドット が自然に形成される機構についても検討を行った.

# 7.シリコン量子ドットのデバイス応用施 毅,永田英次,平本俊郎

シリコン微結晶をフローティングゲートとする単一電子 メモリを試作し,室温において明瞭なメモリ動作(ヒステリシス特性)を観測した.6桁以上のオン/オフ比が得られ,保持時間は数時間以上である.シリコン微結晶中の界面準位や格子欠陥により保持時間が極めて長くなっていることを世界で初めて明らかにした.また,シリコンドットのランダムな配置により,メモリのチャネル幅が短くなるに従い,メモリの特性ばらつきが増大することを明らかにした.

# Quantum mechanical effects in very narrow MOSFETs H. Majima and T. Hiramoto

It is well known that the threshold voltage increases in highly doped MOSFETs or very thin SOI MOSFETs by quantum confinement effects. In this study, we have demonstrated by experiments and simulation that the carriers are confined not only vertically but also horizontally and stronger quantum confinement is attained in very narrow channel MOSFETs. In the experiments, nano-size MOSFETs with width narrower than 20 nm are fabricated and threshold voltage increase is clearly observed when the width is less than 10 nm. The numerical calculation of energy states in narrow channel is also performed and it is verified that the observed threshold voltage increase is due to the quantum confinement effects.

6. Physics of silicon single electron devices H. Ishikuro, N. Takahashi, and T. Hiramoto

Fabrication and physics of siliconsingle electron devices have been extensively studied for the future VLSI device applications.Althoughthesingleelectrondeviceswerestudiedinmetalsand III-V semiconductors, we adopt silicon as a material to consider the compatibility with the VLSI process. Our research work is recognized as one of the pioneering works in this field. A new fabrication process has been developed to fabricate silicon nanostructures smaller than the lithography resolution. Thesize is determined by the SOI thickness by an isotropic etching. MOSFETsfabricated using this techniques hows the Coulomb blockade oscillations at room temperature. We also clarified that the quantum mechanical effects in dots play an important role in transport of single electron transistors operating at room temperature. We have proposed a new single electron structures where the characteristics fluctuations due to thequantum effects are compensated. These results we represented in 1998 International Electron Devices Meeting (IEDM). The formation mechanisms of silicon dots in nano-size MOSFETs are also discussed.

# 7. Applications of silicon quantum dots Y. Shi, E. Nagata, and T. Hiramoto

SingleelectronMOSmemories with siliconfloating nano-crystals gates are fabricated and the memory effect is demonstrated at room temperature. The on/off ratio is more than million and the retention time is longer than several hours. It is clarified for the first time that the interface states and defects in silicon nano-dots makes the retention time longer than expected. It is also found that the characteristics fluctuations become larger as the channel width becomes narrower.

### 羽路研究室

1.液相堆積(LPD)法によるSiO2薄膜 羽路伸夫,荒川太郎,ポーンケオ・チャンタマリー,毛利重信

液相堆積法(LPD)は飽和珪フッ化水素酸水溶液において,40 程度に加熱するか,水で希釈することにより化学平衡をずらせて,浸漬した基板上にシリコン酸化薄膜を堆積する方法であり,低温(室温)プロセスであることが最大の特長である.堆積時の水溶液濃度を変化させることにより,フッ素含有量や誘電率は変化し、特に誘電率は~3程度にまで小さくすることができた.また,クロム配線上をLPDシリコン酸化膜を用いて平坦化できることも示した.これらにより,VLSI配線の層間絶縁膜として有効であることを明らかにした.

2.極薄シリコン酸化膜の評価 羽路伸夫, 荒川太郎, 西尾正裕, 安藤太郎, 加藤紗和子

極薄シリコン酸化膜(膜厚3,5,8nm)のSi MOSダイオードにDC定電圧および定電流ストレスを印加し,絶縁破壊やストレス誘起リーク電流SILC等について評価・検討を行った. 絶縁破壊電荷Qbdはストレス電流や膜厚に依存せずほぼ一定であること、3,5nmの膜厚の試料ではばらつきが大きいことが明らかになった. 極薄膜ではQbdより小さなストレス電荷でもリーク特性が不安定となり, フラッシュメモリ等のデバイスに悪影響を及ぼす.また,界面準位密度はストレス電荷量により決まるが, 絶縁破壊との関係は明らかにはならなかった.

3.高誘電率薄膜(プラズマ励起PLD法) 羽路伸夫 ,荒川太郎 ,新居尚憲 ,高林俊介 ,石橋崇 ,海野直久 渡辺充剛 , 李相國

パルスレーザ蒸着法(PLD)および酸素プラズマを用いたプラズマ励起PLD法(PAPLD)により,高誘電率材料であるBaSrTiOの堆積を行い,評価した.基板はNbドープSTO,およびPt/Ti/SiO2/SiであるPAPLD法ではPLD法に対し,dropletの消滅,酸素欠損の抑制等により,AFMによる表面モフォロジーやリーク特性ははるかに優れているが,X線回折による結晶性は悪く,このため,比誘電率はSTO基板上でそれぞれ~200,300程度である.堆積条件の最適化が必要である.

また,簡単なシミュレーションにより,高誘電薄膜をゲート絶縁膜とした短チャネルMOSFET特性を計算し,この結果,比誘電率50~100程度が適当と考えられる.

Liquid Phase Deposited Silicon-Dioxide Films

Haneji, T. Arakawa, P. Chantamary, and S. Mouri

Liquid Phase Deposition(LPD) is a method to deposit silicondioxide films onto Si substrates through shifting the chemical equilibrium of H2SiF6O4 solution by either heating up to 40 or adding water. Liquid Phase Deposition is low (room) temperature process compared to LPCVD. By changing the concentration of the H2SiF6O4 solution, the amount of F atoms contained in the films and the dielectric constants of the films were changed. The dielectric constant reduced to 3. The LPD films can be deposited on Si, SiO2 and Cr metal wire, and this techniqueispromisingfortheinterlayerinsulatingfilmsinVLSI.

Evaluation of Ultra Thin Silicon-Dioxide Films

Haneji, T. Arakawa, M. Nishio, T. Andou, and S. Katoh

The dielectric breakdown and the stress induced leak current (SILC) were studied by applying DC constant voltage and constant current stress to the Si MOS diode (the thickens of silicon dioxide films were 3,5,8 nm). The charge to break down Qbd was not dependent to the stress current and the thickness of the films, but was varied for the 3 and 5 nm samples. For the ultra thin films, leak characteristics became unstable under the stress chargesmaller than Qbd, and this affects the device characteristics such as flash memory. The density of the interface states were decided by the stress charge, but the relation to the breakdown mechanism was not clear so far.

High K Thin Films (Plasma Assisted PLD)

N. Haneji, T. Arakawa, N. Arai, S. Takabayashi, T. Ishibashi,

N. Unno, M. Watanabe, and S.K. Lee

High dielectric constant BaSrTiOthin films were deposited using pulse laser deposition (PLD) and plasma assisted PLD (PAPLD) in oxygen plasma. The substrates were Nb doped STOandPt/Ti/SiO2/Si. For the samples prepared by PAPLD, the surface morphology and the leak characteristics were superior to the samples prepared by PLD, but the crystalinity was not so good. The electric constant was about 200 and 300, respectively. The optimization of the deposition condition is required.

The characteristics of short channel MOSFET using high dielectric constant material as the gate insulator were calculated, and the dielectric constant of  $50 \sim 100$  was desirable.

# 小谷研究室

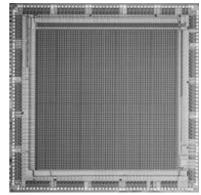

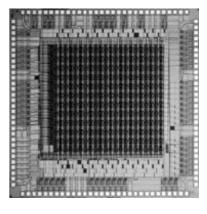

1.極低消費電力A/Dコンバータの研究 小谷光司,大見忠弘

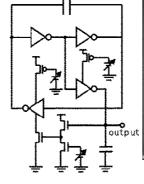

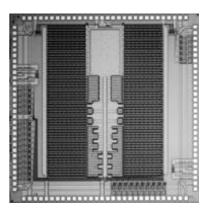

極低消費電力A/Dコンバータの研究を行っている。電荷転送増幅器とダイナミックラッチからなる電圧比較器を開発した。定常電流を流さない完全ダイナミックモードで動作するため,極めて低消費電力化が実現できた。さらに,電荷転送増幅器の低ゲインと低速度動作特性を改善するため,正帰還回路を付加した新しい正帰還電荷転送増幅回路を開発し,高精度,低消費電力電圧比較器を実現した。試作した完全差動型正帰還電荷転送電圧比較器回路は,比較器当たり12μW/MS/sの消費電力を示した。

2.瞬時応答を可能にするビットフロー型データフローパ スミニマムプロセッサ

小谷光司, 今井誠, 野沢俊之, 藤林正典, 大見忠弘

「柔軟な解釈」、「大枠の判断」、「直感による類推」といっ たしなやかな情報処理を得意とし,瞬時応答性を持った知 的電子システムを実現する事が21世紀へ向けての最大の課 題である .この目的のため ,基本素子であるトランジスタの 機能を飛躍的に向上させる四端子デバイス技術を確立した. 四端子デバイスであるニューロンMOSトランジスタを用い ることにより、論理演算機能を制御信号により瞬時に切り 換えることが可能なFlex wareを実現した. さらに,現在の フォン・ノイマン型計算機のボトルネックを根本的に解消 するデータフローパスミニマムアーキテクチャ, さらにそ れを発展させ、「大枠の判断」をディジタルコンピュータの 世界で実現するMSD先行ビットフローアーキテクチャを実 現した.冗長数系を用いることにより,通常では下位からの 演算である算術演算と,上位からの演算である比較演算が, 共に上位からのビットフローにより実現できる. 結果は上 位のビットから出力されるので,判断が付いた時点で,下位 の演算をストップすることが可能で,無駄な演算を省略す ることができる.まさに「大枠の判断」が可能となるのであ る.

1 . Low Power, High Accuracy A/D Converter K. Kotani and T. Ohmi

Wehavestudiedlow power A/Dconverter. A very low-power voltagecomparator circuitry, which consists of a charge transfer preamplifier and a dynamic latch circuit, has been developed. It operates in purely dynamic mode, resulting in very low power consumption. In addition, in order to solve the problem of small gain and slow operation of charge transfer amplifier, we have newly introduced a positive feedback mechanism, resulting in the realization of a high-accuracy and low-power comparator. Fabricated test circuit of fully differential positive-feedback charge-transfer comparator exhibits very low power operation capability of 12 uW per MS/s per comparator.

2 . Data Flow Path Minimum Processor for Real-Time Response Capability

K. Kotani, M. Imai, T. Nozawa, M. Fujibayashi, and T. Ohmi

The most important issue, as we head to ward the 21st century, is the development of a real-time responsive intelligent electronic system featuring human-like capabilities such as "flexibleinterpretation", "overall judgment" and "intuitive problem solving". For this purpose, a four terminal device technology which greatly enhances the functionality of the basic circuitelement-thetransistor-hasbeen developed. A new form of hardware, which we named "Flex ware" because of the ability to alter its logic function in real-time through the application of externalcontrolsignals, hasbeen developed based onfourterminaldevicetechnologyemployingtheneuron-MOStransistor. A new "Most-Significant-Digit-First Bit-Flow Architecture" whichenablestheperformanceof"overalljudgment"inthedigitalcomputerworldhasbeenrealizedinconjunctionwith"Data-Flow-PathMinimum Architecture" which solves the busbottleneck problem faced by present Von Neumann computers. Conventionally, arithmetic operations are computed beginning from the Least-Significant-Digit (LSD) while comparison operations are carried outfrom the MSD. Using redundant number systems, it is possible to perform both operations using the "MSD-First Bit-Flow Architecture". In this architecture, computation results are obtained MSD-first and further computation is immediately terminated once the judgment is delivered.Hence, nounnecessary computation of the lower bits is ensured. This bears a strong resemblance to "overall judgment". It is our objective to develop an intelligent electronic system through the extension of these original technologies.

### 3.3. 発表論文

### 1.研究論文

- (1) 大見 忠弘, 今井誠, 小谷光司,

- 「知能集積回路 瞬時応答を可能にするビットフロー型データフローパスミニマムプロセッサ 」,

- 電子情報通信学会論文誌C-I, Vol.J81-C-I, No. 4, pp. 179 186, 1998年4月.

- (2) K. Kotani, T. Shibata, M. Imai, and T. Ohmi, "Clock-Controlled Neuron-MOS Logic Gates," IEEE Transactions on Circuits and Systems-II, Vol. 45, No. 4, pp. 518 - 522, April, 1998.

- (3) 平本俊郎,

- 「微細MOSトランジスタの動作原理」, 応用物理 ,Vol. 67, No. 5, pp. 571 - 575, 1998年5月.

- (4) K. Kotani, T. Shibata, and T. Ohmi, "CMOSCharge-TransferPreamplifierforOffset-FluctuationCancellationin Low-PowerA/D Converters," IEEE Journal of Solid-State Circuits, Vol. 33, No. 5, pp. 762 - 769, May, 1998.

- (5) 関根慶太郎, 中井貞雄, 西村敏博, 下位紘一, 西村和夫, 浅田邦博,

- 「電子・情報・システム分野における歩み」, 電気学会誌 ,110周年記念特集 電気電子技術10年の歩 み, Vol.118, No.6, pp.348-354, 1998年6月.

- (6) T. Irita, T. Tsujita, M. Fujishima, and K. Hoh, "A Simple Chaos-Generator for Neuron Element UtilizingCapacitance-npn-TransistorPair", Journal of Computers & Electrical Engineering, Vol. 24, pp.43-61,June,1998.

- (7) Hiroki Ishikuro and Toshiro Hiramoto, "Hopping Transport in Multiple-Dot Silicon Single Electron MOSFET", Solid State Electronics, Vol. 42, No. 7-8, pp. 1425 - 1428, July-August, 1998.

- (8) Toshikazu Mukaiyama, Ken-ichi Saito, Hiroki Ishikuro, Makoto Takamiya, Takuya Saraya, and Toshiro Hiramoto, "Fabrication of Gate-All Around MOSFET by Silicon Anisotropic Etching Technique", Solid State Electronics, Vol. 42, No. 7-8, pp. 1623 - 1626, July-August, 1998.

- (9) T. N. Duyet, H. Ishikuro, M. Takamiya, T. Saraya, and T. Hiramoto,

"Suppression of Geometric Component of Charge Pumping Current in Thin Film SOI MOSFET",

Japanese Journal of Applied Physics, Part 2, Vol. 37, No. 7B, pp. L855 L858, July, 1998.

- (10) Y. Shi, K. Saito, H. Ishikuro, and T. Hiramoto, "Effectsoftrapsonchargestoragecharacteristicsin metal-oxide-semiconductormemorystructuresbasedonsilicon nanocrystals", Journal of Applied Physics, Vol. 84, No. 4, pp. 2358 - 2360, August, 1998.

- (11) M. Song and K. Asada, "Design of Low Power Digital VLSI Circuits Based on a Novel Pass-transistor Logic", IEICE Trans. Electronics, Vol. E81-C, No. 11, pp. 1740 -1749, November, 1998.

- (12) M. Sugahara, H.F. Lu, H.Q. Yin, Y. Kumagai, M. Miyata, H. Kaneda, N. Haneji, and N.Yoshikawa, "Anomalous Hysteretic Dielectric Polarization inc-Axis-Oriented La2-xSrxCuO4Film" Advances in Superconductivity (K. Osamura, I. Hirabayashi eds. Springer, Tokyo, 1998), Vol. 1, pp. 115 - 118

- (13) Toshiro Hiramoto and Hiroki Ishikuro, "Quantum Energy and Charging Energy in Point Contact MOSFETs acting as Single Electron Transistors", Superlattices and Microstructures, Vol. 24, No. 1/2, pp. 263-267,1999.

- (14) S. Amakawa, K. Kanda, M. Fujishima, and K.Hoh, "A Simple Model of a Single-Electron Floating Dot Memory for Circuit Simulation", Japanese Journal of Applied Physics, Vol. 38, Part 1, No. 1B, pp. 429 - 432, January, 1999.

- (15) Hiroki Ishikuro and Toshiro Hiramoto, "Fabrication of Nano-Scale Point Contact Metal-Oxide-SemiconductorField-Effect-TransistorsUsingMicrometer-Scale Design Rule", Japanese Journal of Applied Physics, Vol. 38, Part 1, No. 1B, pp. 396 - 398, January, 1999.

- (16) Yi Shi, Kenichi Saito, Hiroki Ishikuro, and Toshiro Hiramoto,

"Effects of Interface Traps on Charge Retention Characteristics in Silicon-Quantum-Dot-Based Metal-Oxide-Semiconductor Diodes",

Japanese Journal of Applied Physics, Vol. 38, Part 1, No. 1B, pp. 425 428, January, 1999.

- 1B, pp. 425 428, January, 1999.

(17) Hiroki Ishikuro and Toshiro Hiramoto,

"On the origin of tunneling barriers in silicon single electron and single hole transistors",

Applied Physics Letter, Vol. 74, No. 8, pp. 1126 1128,

February,1999.

- (18) M. Sugahara, S. Mitani, H.F. Lu, Y. Kumagai, H. Kaneda, N. Haneji, and N. Yoshikawa,

- "TheoryandExperimentalEvidenceforPairFQHEState Caused by Zero-Point Harmonic Oscillation in Block-LayerPotential",

- Symmetry and Pairing in Superconductors (M. Ausloos, S. Kruchinin eds., Kluwer, Netherlands, 1999), pp. 395 403.

- (19) H.Q. Yin, Y. Ueda, T. Arakawa, H. Kaneda, N. Yoshikawa, N. Haneji, and M. Sugahara, "Plasma Activated Pulsed Laser Deposition for Synthe-

sis of Particle-Free La2-xSrxCuO4 Films",

Thin Solid Films, Vol. 338, pp. 20 - 23, 1999.

#### 2.国際会議

- T. Tsujita, T. Irita, M. Fujishima, and K. Hoh, "Self-Oscillating Chaos Generator Using CMOS Multivibrator",

- Proceedings of 2nd International Conference on Knowledge-Based Intelligent Electronic Systems, Adelaide, pp. 213 217, April, 1998.

- (2) K. Hoh, T. Irita, T. Tsujita, and M. Fujishima, "Generation of Chaos with Simple Sets of Semiconductor Devices."

- Proceedings of 2nd International Conference on Knowledge-Based Intelligent Electronic Systems, Adelaide, pp. 250 259, April, 1998.

- (3) K. Asada,

- "Microelectronics education in Japan", Microelectronics Education 1998, The Hague, The Netherlands, pp. 195 - 198, May, 1998.

- (4) S. O'uchi, S. Amakawa, M. Fujishima, and K. Hoh, "Simulation of a Single-Electron Flash Memory", Collected Abstracts of 1998 International Symposium on Formation, Physics and Device Application of Quantum DotStructures(QDS'98),HokkaidoUniversityConference Hall, Sapporo, pp. 78 - 79, June, 1998.

- (5) S. Amakawa, K. Kanda, M. Fujishima, and K. Hoh, "A Simple Model of a Single-Electron Floating Dot Memory for Circuit Simulation", Collected Abstracts of 1998 International Symposium on Formation, Physics and Device Application of Quantum DotStructures(QDS'98),HokkaidoUniversityConference Hall, Sapporo, pp. 80 - 81, June, 1998.

- (6) Yi Shi, Kenichi Saito, Hiroki Ishikuro, and Toshiro Hiramoto,

- "Effects of Interface Traps on Charge Retention Characteristics in Silicon-Quantum-Dot-Based MOS Diodes".

- 1998InternationalSymposiumonFormation,Physicsand DeviceApplicationofQuantumDotStructures(QDS'98), Hokkaido University Conference Hall, Sapporo, Hokkaido, pp. 6 7, June, 1998.

- (7) Hiroki Ishikuro and Toshiro Hiramoto, "Fabrication of Nano-Scale Point Contact MOSFETs Using Micrometer-Scale Design Rule", 1998InternationalSymposiumonFormation,Physicsand Device Application of Quantum DotStructures (QDS'98), Hokkaido University Conference Hall, Sapporo, Hokkaido, pp. 76 - 77, June, 1998.

- (8) Kenichi Saito, Yi Shi, Hiroki Ishikuro, and Toshiro Hiramoto,

- "Narrow Channel MOS Memory Based on Silicon Nano-Crystals",

- 1998 IEEE Silicon Nanoelectronics Workshop, Hilton Hawaiian Village, Hawaii, USA, pp. 17 18, June, 1998.

- (9) Toshiro Hiramoto,

- "Quantum mechanical effects in 10 nm point-contact MOSFETs".

- $Second Sweden-Japan QNANOW orkshop, Saro, Sweden,\\ June, 1998.$

- (10) Toshiro Hiramoto, "Characteristics of decanano-scale MOSFETs", FED-PDIJointConferenceon21stCenturyElectronDevices,Magnus-HausBerlin,Berlin,Germany,June,1998.

- (11) Yuri Yasuda, Makoto Takamiya, and Toshiro Hiramoto, "Scaling of Delta-Doped Channel MOSFET with Suppressed Statistical Vth Fluctuations", 1998 International Workshopon Advanced LSIs-Scaled Device/Process and High Performance Circuits --, Hokkaido University, Sapporo, pp. 13 - 18, July, 1998.

- (12) Toshiro Hiramoto and Hiroki Ishikuro, "Quantum Energy and Charging Energy in Point Contact MOSFETs acting as Single Electron Transistors", EleventhInternationalConferenceonSuperlattices,Microstructures, and Microdevices, Hurgada, Egypt, July, 1998.

- (13) Hiroki Ishikuro and Toshiro Hiramoto, "The Origin of Tunnel Barrier in Silicon Single Electron Transistor", InternationalConferenceonPhysicsofSemiconductors, Mo-P140, Jerusalem, Israel, August, 1998.

- (14) S. Amakawa, M. Fujishima, and K. Hoh, "Single-ElectronTunnelingthroughanAsymmetricTunnel Barrier", Extended Abstracts of 6th International Workshop on Computational Electronics, Osaka, pp. 137 - 140, 1998.

(15) T. Tsujita, Y. Aihara, M. Fujishima, and K. Hoh, "DesignandExperimentofaMultivibrator-BasedSimple CMOS Chaos Generator" Proceedings of 1998 International Symposium on Nonlinear Theory and Its Applications (NOLTA 98), Crans-

Montana, Vol. 3, pp. 951 - 954, September, 1998.

- (16) M. Ikeda and K. Asada, "Time-Domain Minimum-Distance Detector and Its Application to Low Power Coding Scheme on Chip Interface", 24th European Solid State Circuit Conference, The Hague, The Netherlands, pp. 464 - 467, September, 1998.

- (17) TranNgocDuyet,Hirokilshikuro,YiShi,TakuyaSaraya, Makoto Takamiya, and Toshiro Hiramoto, "Measurement of Energetic and Lateral Distribution of Interface State Density in FD SOI MOSFETs", 1998InternationalConferenceonSolidStateDevicesand Materials (SSDM'98), International Conference Center Hiroshima, Hiroshima, Japan, pp.322 - 323, September, 1998.

- (18) Makoto Takamiya, Takuya Saraya, Tran Ngoc Duyet, Yuri Yasuda, and Toshiro Hiramoto, "High Performance Accumulated Back-Interface Dynamic Threshold SOI MOSFET's (AB-DTMOS) with Large Body Effect at Low Supply Voltage", 1998InternationalConferenceonSolidStateDevicesand Materials (SSDM'98), International Conference Center Hiroshima, Hiroshima, Japan, pp. 312 - 313, September, 1998.

- (19) Yi Shi, Kenichi Saito, Hiroki Ishikuro, and Toshiro Hiramoto, "Characteristics of Narrow Channel MOSFET Memory Based on Silicon Nanocrystals", 1998InternationalConferenceonSolidStateDevicesand Materials (SSDM'98), International Conference Center Hiroshima, Hiroshima, Japan, pp. 172 - 173, September, 1998.

- (20) Tran Ngoc Duyet, Hiroki Ishikuro, Makoto Takamiya,

Takuya Saraya, and Toshiro Hiramoto,

"Effects of Body Reverse Pulse Bias on Geometric Component of Charge Pumping Current in FD SOI MOSFETs",

- 1998IEEEInternationalSOIConference,Stuart,Florida, USA, pp. 79 80, October, 1998.

- (21) K. Hoh, T. Tsujita, T. Irita, Y. Aihara, and M.Fujishima, "Semiconductor Chaos-GeneratingElements of Simple Structure and TheirCoupled Operation", Proceedings of 5th International Conference on Soft ComputingandInformation/IntelligentSystems,Iizuka, Vol. 1, pp. 126 - 130, October, 1998.

"Non-destructiveExtractionofStructuralParametersof Fully-depletedSOIMOSFETsusingSubthresholdSlope Characteristics"

(22) H. Ito and K. Asada,

- 1998 Conference on Optolectronics and Microelectronics Materials and Devices, Parth, Australia, TO-6, pp. 153-154.December.1998.

- (23) Hiroki Ishikuro and Toshiro Hiramoto, "Influence of Quantum Confinement Effects on Single Electron and Single Hole Transistors", 1998 IEEE International Electron Devices Meeting, San Francisco, USA, pp. 119 - 122, December, 1998.

- (24) Makoto Takamiya and Toshiro Hiramoto, "HighPerformanceElectricallyInducedBodyDynamic Threshold SOI MOSFET (EIB-DTMOS) with Large Body Effect and LowThreshold Voltage", 1998IEEEInternationalElectronDevicesMeeting,San Francisco, USA, pp. 423 - 426, December, 1998.

- (25) M. Ikeda and K. Asada, "CAM Macro Cells with Minimum Distance Detector using Time-Domain Technique", International Workshop on IP Based Synthesis and System Design, INPG, Grenoble, France, pp. 137 - 140, December, 1998.

- (26) R. Zheng and K. Asada, "A High Speed Completion Prediction Adder Based on Binary Carry Lookahead Adder", International Workshop on IP Based Synthesis and System Design, INPG, Grenoble, France, pp. 149 - 153, December,1998.

- (27) K. Kotani and T. Ohmi, "FeedbackCharge-TransferComparatorwithZeroStatic Power," 1999IEEEInternationalSolid-StateCircuitsConference (ISSCC), San Francisco, pp. 328 - 329, February, 1999.

- (28) E. Nagata, N. Takahashi, H. Ishikuro, and T. Hiramoto, "Width Dependence of Threshold Voltage Shift in Narrow MOSFET Memories with Silicon Nano-Crystals", The ThirdSymposium on Surface and Interface Dynamics, Across Fukuoka, Japan, March, 1999.

- (29) S. Komatsu, M. Ikeda, and K. Asada, "Low Power Chip Interface Based on Bus Data Encoding with Adaptive Code-Book Method", 9th GREAT LAKES SYMPOSIUM ON VLSI, Ypsilanti Marriot, Michigan, USA, pp. 368 - 371, March, 1999.

- (30) T. Mido and K. Asada,

"An Analysison Hi-Frequenacy Interconnection in VLSI

Considering Inductive Effects",

International Workshop on Timing Issues In the Specifi-

cationandSynthesisofDigitalSystems(TAU'99),pp.173 - 178, Doubletree Hotel, Monterey, CA, USA, March 1999.

(31) T. Mido, H. Ito, and K. Asada, "TEST Structure for Direct Extraction of Capacitance Matrix in VLSI",

Proceeding of International Conference on Microelectronic Test Structures (ICMTS), Gothenburg, Sweden, pp. 200 - 205, March, 1999.

- (32) K. Hoh, T. Tsujita, T. Irita, and M. Fujishima, "IntegratedChaos-GeneratingCircuitswithSimpleStructure for the Bio-Inspired Information Processing", ProceedingsofInternationalSymposiumonFutureofIntellectual Integrated Electronics, Sendai, pp. 389 - 393, March. 1999.

- (33) K. Hoh, A. Imamura, T. Tsujita, and M. Fujishima, "Generation of Chaos by Extended Operation of the Pipelined AD Converter", ProceedingsofInternationalSymposiumonFutureofIntellectual Integrated Electronics, Sendai, pp. 395 - 397, March, 1999.

- (34) K. Asada, T. Nezuka, T. Fujita, M. Ikeda, and J. Akita, "An Image Sensor for Motion Detection using Variable Block Access", International Symposium on Future of Intellectual Integrated Electronics, Sendai International Center, Sendai, Japan, ex12, March, 1999.

- (35) K. Asada, T. Nezuka, T. Fujita, M. Ikeda, and J. Akita, "Image sensors with flexible access methods to pixels for adaptivespatialandtimeresolution", International Symposium on Future of Intellectual Integrated Electronics, Sendai International Center, Sendai, Japan, pp. 49 - 62, March, 1999.

- (36) T. Hiramoto, Y. Yasuda, M. Takamiya,

"Threshold Voltage Fluctuations Induced by Statistical

Position Distribution of Dopant Atoms in Scaled

MOSFETs",

InternationalSymposiumonFutureofIntellectualIntegratedElectronics(ISFIIE),SendaiInternationalCenter,

Miyagi, Japan, pp. 131 - 135, March, 1999.

- (37) T. Ohmi, M. Imai, M. Konda, T. Nozawa, T. Morimoto, T. Nakayama, M. Fujibayashi, and K Kotani, "Intelligence Implementation to Silicon Chip," ProceedingsofInternationalSymposiumonFutureofIntellectual Integrated Electronics, Sendai, pp. 3 - 20, March, 1999.

- (38) M. Imai, T. Nozawa, M. Fujibayashi, K Kotani, and T. Ohmi,

"Computational Architecture with Decreasing Calcula-

tionStepsUsingMost-Significant-Digit-FirstCalculation Scheme."

ProceedingsofInternationalSymposiumonFutureofIntellectual Integrated Electronics, Sendai, pp. 469 - 472, March, 1999.

(39) T. Nozawa, M. Imai, M. Fujibayashi, K Kotani, and T. Ohmi

"A Parallel Vector Quantazation Processor Having the FeatureofLow HardwareComplexity,"

ProceedingsofInternationalSymposiumonFutureofIntellectual Integrated Electronics, Sendai, pp. 473 - 475, March, 1999.

(40) T. Hiramoto,

"CharacterizationofSiliconSingleElectronTransistors", Japan-UK 10+10MeetingonNewDevelopmentsinAdvancedElectronicandOpticalMaterialsandDevices,Oxford University, UK, March, 1999.

### 3. 国内学会,研究会

(1) 浅田邦博, 根塚智裕, 秋田純一,

「4進木アクセス機能を有する多階調イメージセンサの設計試作」,

重点領域研究「極限集積化シリコン知能エレクトロニクス」公開シンポジウム,機械振興会館(東京), pp. 202-208, 1998年4月.

- (2) 平本俊郎,安田有里,高宮真,

- 「不純物揺らぎによるしきい値電圧ばらつきを考慮した デルタドープ型MOSFETのスケーリング」, 重点領域研究「極限集積化シリコン知能エレクトロニク

ス」公開シンポジウム,機会振興会館(東京), pp. 168 - 174, 1998年4月.

(3) 佐藤義則,鄭若彤,浅田邦博,

「終了検出パイプライン加算器を用いた疑似非同期マイクロプロセッサの設計」,

電子情報通信学会,会津大学(福島),信学技報,ICD98-17,CPSY98-17,FTS98-17,pp.47-52,1998年4月.

- (4) 石黒仁揮,平本俊郎,

- 「シリコン単一電子素子における量子効果の評価」, 電子情報通信学会電子デバイス,シリコン材料デバイス 合同研究会技術研究報告,広島大学工学部(広島), ED98-4, SDM98-4, 1998年4月.

- (5) 平本俊郎,

「超低消費電力高速デバイスプロセス技術」, 関西セミコン98ULSI技術セミナーセッション5「プロセス・デバイス技術 - 実用化迫る0.18 µ mプロセス - 」, ハイアットリージェンシーオオサカ(大阪),pp. 5-1 - 5-6, 1998年6月. (6) 鳳紘一郎,

"VDEC の役割とその将来".

電気学会センサ・マイクロマシン部門総合研究会, pp.23-30, 1998年9月.

- (7) 辻田達男, 相原祐一郎, 藤島実, 鳳紘一郎, 「CMOSカオスマルチバイブレータの解析と動作」, 電子情報通信学会1998年基礎・境界ソサイエティ大会, 山梨大学(山梨), A-1-24, p.24, 1998年9月.

- (8) 三堂哲寿, 伊藤浩, 浅田邦博, 「集積回路における容量行列要素の直接抽出手法」, 1998年電子情報通信学会ソサイエティ大会, 山梨大学 (山梨), C-12-1, p.92, 1998年9月.

- (9) 鄭若彤, 浅田邦博,

「終了予測加算器の設計」、

1998年電子情報通信学会ソサイエティ大会 山梨大学, C-12-22, pp.113, 1998年9月.

(10) 小松聪, 池田誠, 浅田邦博,

「低消費電力チップインタフェースのための適応型コード帳符号化方式」.

1998年電子情報通信学会ソサイエティ大会 山梨大学 (山梨) C12-23, pp.114, 1998年9月.

(11) 浅田邦博, 根塚智裕, 池田誠,

「階層アクセスパスによる高速イメージセンサの実現」, 1998年電子情報通信学会ソサイエティ大会, 山梨大学 (山梨) SC-10-5, pp184-185, 1998年9月.

(12) 福岡哲也, 藤島実, 鳳紘一郎,

「Ni ゲート電極を用いた P型ショットキー障壁SOI-MOSFETの試作」,

1998年秋季第59回応用物理学会学術講演会 広島大学 西条キャンパス(広島),15a-P9-9, p.777, 1998年9月.

(13) 天川修平, 藤島実, 鳳紘一郎,

「単電子効果が現れる系でのトンネリングレートの計算」, 1998年秋季第59回応用物理学会学術講演会,広島大学西 条キャンパス(広島),17p-ZK-11, p.147, 1998年9月.

(14) 青柳稔, 浅田邦博,