2009年 7月15日 第1号

- ◆65nm チップ試作「次世代回路アーキテクチャプロジェクト」正式募集

- ◆0.18um チップ試作の高耐圧オプション計画

- ◆ローム 0.18um チップ試作でよくある間違い:テープアウト担当者からのお願い

- ◆MOSIS 試作サービス申込み開始

## 同じ内容は http://www.vdec.u-tokyo.ac.jp/Tayori/ にも掲載されています。

## VDEC からの大事なお知らせです。

# ◆65nm チップ試作「次世代回路アーキテクチャプロジェクト」 正式募集が始まります

平成 20 年度から、経済産業省のプロジェクト「次世代回路アーキテクチャ」を半導体理工学研究センター(STARC)が受託することで開始された 65 nm チップ試作ですが、7月 14日の経済産業省のプロジェクト応募の開札後ただちに今年度も試作の正式募集が開始されます。本プロジェクトでは、3月に予備的調査を行い、部分的に仮採択を行っておりますが、まだプロジェクト枠には余裕がありますので、多数の応募を期待しております。応募は、STARC により組織される産業界・大学メンバーによる評価委員会により審査をされ採否が決定されます。採択された場合、

STARCによるチップ試作の進捗管理が行われるほか、試作評価結果の報告書、および試作内容のIPのデータベース化へのご協力をいただくことになります。

なお、応募に先立って VDEC に NDA をお送りいただくことで、設計資料などの入手が可能ですので、ぜひアイデアを検証いただいた上でより具体的な提案内容として応募いただきますことを期待しています。

詳細は VDEC の WEB ページを参照ください。(池田 誠)

## ◆0.18umチップ試作の高耐圧オプション計画

平成 1 7年度から開始し、現在 VDEC の主流となっております ローム 0.18 um CMOS チップ試作に関して、オプションとして、高耐圧トランジスタの導入を検討しています。 0.18 um トランジスタに関してはほぼコンパチかつ、最大 40V の耐圧(基板を基準とするとプラスマイナス 20V)を有するものです。 RF などにも適した高抵抗基板を使用するほか、これまでの 0.18 um と比較して

深い接合が利用可能となることから光感度の改善などが期待されます。現在、従来の 0.18 um との設計、製造、組み立て工程まで含めたコンパチビリティの確認を行っており、詳細を近日中にはメールなどで連絡いたします。ぜひ新しいメニューにもご期待ください。(池田 誠)

# ◆ローム 0.18um チップ試作でよくある 間違い: テープアウト担当者からのお願い

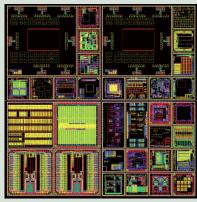

今年度から、ローム 0.18um チップ試作頻度を毎月から 2ヶ月おきにすると変更する代わりに、従来は 1ヶ月程度あったチップ納品の誤差をなくす取り組みを開始しました。毎回のチップ試作では図のように約 30 区画のチップが相乗りしています。テープアウト担当者から、ローム 0.18um チップ試作でよくある間違い 2点について、お知らせいたします。

- (1) チップ四隅のレイアウト禁止領域にレイアウトしてしまう。

- (2) レイアウト提出時のパッケージの指定で、パッケージの形式 や個数の指定を間違える。

(1) の具体的なレイアウト禁止領域のサイズに関しましては、VDEC の設計規則の web を参照して下さい。チップ四隅には、LSI 製造に必要なマークを VDEC でのテープアウト時にはめ込みますので、皆様のレイアウトが禁止領域にあると、製造することができません。

ローム 0.18um チップの相乗り試作

(2) を間違えると、納品されたチップを見てビックリすることになりますので、ご注意下さい。今後とも、ローム 0.18um チップ試作をよろしくお願いいたします。(高宮 真)

## ◆MOSIS 試作サービス申込みを開始しました

今年度も、MOSIS を通したチップ試作サービスを VDEC ユーザの皆様に提供する準備が整いました。既に、申込みを受け付けております。利用可能なプロセス・試作日程・申込み方法は、

VDECホームページの「チップ試作日程」からご覧になれます。皆様のご利用をお待ちしております。(松本 剛史)

VDECセンター長 浅田 邦博

#### VDECだより発行について

ユーザの皆様に「VDEC だより」を定期的にお送りすることにしました。1996 年の VDEC 発足時、電子メールはまだまだ新鮮で大変有効な情報伝達の方法でした。しかし今日ではスパムの嵐の中、大量のメールが飛び交い、もはや確実性の高い方法ではなくなってしまったようです。たとえば昨年より 65 nm 試作を開始していることをご存知でないユーザがおられるとお聞きしました。そこで確実に情報をお伝えする手段とし て古典的ですが、紙媒体を用いることにしました。本誌では新しいサービスや変更点、VDEC の現状等をタイムリーにお知らせする予定です。ぜひご一読ください。

#### VDEC デザイナーズフォーラム開催

#### http://www.vdec.u-tokyo.ac.jp/DesignersForum/Forum09.html

6/5(金)-6/7(日)、東大の武田ホールにおいて VDEC デザイナーズフォーラムが開催され、88人の参加者が集まりました。学生発表講演、参加者によるショート講演、ポスターセッション、大学院の学生の立案による Ph.D. 企画セッションなど、試作経験やノウハウ、失敗談なども含めて、研究発表だけではなく普段の学会では聞けないような話を聞くことができました。また、今年は Workshop として「CAD インストール講習会」を併設し、「これまで CAD 環境を整備していた先輩が卒業してしまい、環境整備をできる人がいなくなって困っていたので、この講習会で CADインストール方法を学べてよかったです。」という声を聞きました。

今年も、著名な先生を招いた特別講演を開催し、東大の柴田先生、Michigan State University の Chakrabatty 先生、芝浦工大の宇佐美先生、元 STARC/ルネサス/東大客員教授の益子さまからの講演も好評でした。

普通の学会に出席するよりも役に立ち、楽しく、刺激的なフォーラムだったと思います。来年もたくさんの教員・学生の参加をよろしくお願いします。(名倉 徹)

## 夏の CAD 講習会ストリーミング配信開始

毎年、夏の VDEC CAD 講習会は東大で集中開催してきましたが、今年からの新たな試みとして、東大で開催する CAD 講習会の様子を VDEC 拠点校(北大・東北大・金沢大・東工大・名大・京大・阪大・広大・九大)にストリーミング配信し、拠点大学でも受講できるようにする予定です。

各会場の都合もあって、全ての大学で全項目を開催することは

#### http://www.vdec.u-tokyo.ac.jp/CAD/CADTraining.html

困難ですし、そもそもストリーミング配信で有効な講習となり得るのかも疑問です。まだまだ試験的な運用であるとご理解ください。これまでの東大のみの開催に比べ、多少なりとも利便性が向上できればと願っております。

CAD 講習会をとおして設計力向上にご活用いただければ幸いです。(名倉 徹)

#### アドバンテスト D2T 寄付研究部門の活動紹介

SoC テストシステム T2000

株式会社アドバンテストからの寄付によって、2007年10月に「アドバンテストD2T寄付研究部門」がVDEC内に設立されて以来、2年近くが経過致しました。

VDEC ユーザの皆様に対する活動としては、(1) テスト分野における海外/国内の著名な研究者の講演会の開催、(2) 東大VDEC 所有の LSI テスタの利用環境の整備、を行なってきました。前者については、設立以来、1年に1度のペースでシンポジウムを開催しており、150名前後の方々に参加して頂いております。後者については、アドバンテスト社の SoC テストシステム T2000を公開しており、ネットワーク経由で遠隔地からの利用も可能となっておりますので、VDEC で試作した LSI チップの評価に利用希望の場合にはご連絡下さい。

また、寄付研究部門設立以来、Bremen 大学の Goerschwin Fey 博士、University of California, Santa Barbara の Kwang-Ting (Tim) Cheng 教授を客員教員として招へいし、D2T のネットワークを広げています。

皆様の研究・教育活動の一助となるよう、今後もこれらの活動 を継続して参りますので、よろしくお願い致します。(小松 聡)

# 研究室便り

## 神戸大学 永田研究室

VDEC の設立当初から、CAD ツール利用サービスや LSI チップ試作サービスを活用してきました。古くは 0.8 um CMOS から、最近の 65 nm CMOS まで、7-8 世代に渡り最先端の半導体技術をタイムリーに提供頂いており、世界でも稀なるサービスに日頃よりたいへん感謝しています。

思えば最初の頃は、LVS 検証のルールセットの提供も経験も無くて、10mm 角チップの接続をひたすら目視・手作業で確かめました。近年は、アカデミック・ユーザとはいえファウンドリからほぼフルセットの設計環境が提供されるので、チップ開発の心配と失敗がだいぶん減り、設計の内容にフォーカスできるようになりました。VDEC とユーザによる経験知の蓄積の現れの一つと思います。

さて、当研究室はミックストシグナル VLSI の設計技術とシステム応用技術をテーマにしています。とくに最近は、「ノイズなどの環境擾乱に強いアナログ / RF / デジタル LSI の設計手法と構築技術」に幅広く取り組んでいます。ものづくりの技術基盤としてLSI 設計を極めること、産業に貢献し得る具体的な研究をまとめ

ること、をモットーに、総勢 18名(社会人博士3名、博士3名、修士6名、学部6名、2009年6月末時点)の学生達と共に、研究課題を鋭意進めています。

# 九州大学 石原研究室

石原研究室はシステム LSI の設計技術やその応用技術の研究をしています。現在はマルチコアプロセッサの省電力化の研究をしています。VDEC のローム 0.18 um、ASPLA90 nm、e-shuttle65 nm お よ び ル ネ サ ス テ ク ノ ロ ジ の M32R、SH3-DSP、東芝の MeP を利用させて頂いています。我々の設計は大きいものでは 1 千万トランジスタを超えますから、設計資産(IP)を流用しているとはいえ、設計時間は膨大です。学生さんに何度が徹夜をしてもらったおかげで大規模チップを作るノウハウが蓄積されてきました。一昨年に設計した多電源電圧マルチコアプロセッサは LSI IP デザイン・アワードの MeP 賞を受賞しました。今後もありがたく VDEC を利用させて頂いて、学生と一緒にチップ作りを楽しみたいと思います。

#### VDECスタッフより…

## あっと言う間の13年

皆様 こんにちは。

VDEC を蔭ながらささえている スタッフの一人、秘書の吉田直美 です。

どうしても解決できない難問に ぶつかって、最後の頼みの綱の VDECの電話の向こうの先にいる 秘書二人のうちの一人です。わか ることはお答えし、技術的なことは 先生方にバトンタッチして、誠心誠意、対応させて頂いています。でも、 VDECとはメールでの連絡が原則となっているのは、ご存知ですね。

VDEC が発足して4ヶ月後に採用になったので、足かけ13年の在籍になります。体育会系運動部(テニス部)で鍛えた体力と、十二支の亥年生まれなので、VDECに何事が起ろうとも猪突猛進で突っ走って来ました。秘書に要求されるのは、事務処理能力、突然の変化球の対処、世間の話題の蓄積(VDEC の先生方との会話に必要)、お客様へのお茶の入れ方、出し方、そして気配りと場かい笑顔です。これからもよろしくお願いします!

## 本年度4月よりVDEC助教に着任しました!

皆様はじめまして。飯塚哲也と申します。私は2007年3月までVDECの浅田教授のご指導のもと、VLSIの設計自動化に関する研究に取り組んでおりました。卒業後は某ファブレス半導体メーカーに所属しアナログIP開発等の業務に従事しておりましたが、本年度から助教としてVDECに参加させ

て頂くことになりました。これからどうぞよろしくお願いいたしま す!

VDECでの業務の傍ら、研究活動にも欠かせない体力作りのためランニングを始めました。大学の近くの上野公園の周りをよく走っています。運動をすると体も頭もリフレッシュされてとても気分がいいですね。最近は暑くなってきて汗だくになってしまうのが難点ですが…。

こんな私ですが、まだまだ力不 足の点が多く、これより皆様のご 協力を賜ることが多々あるかと存 じます。今後ともご指導ご助言を 頂ければ誠に幸いでございます。 何卒よろしくお願いいたします。