| 10:00 |

Opening remarks |

| 10:15 |

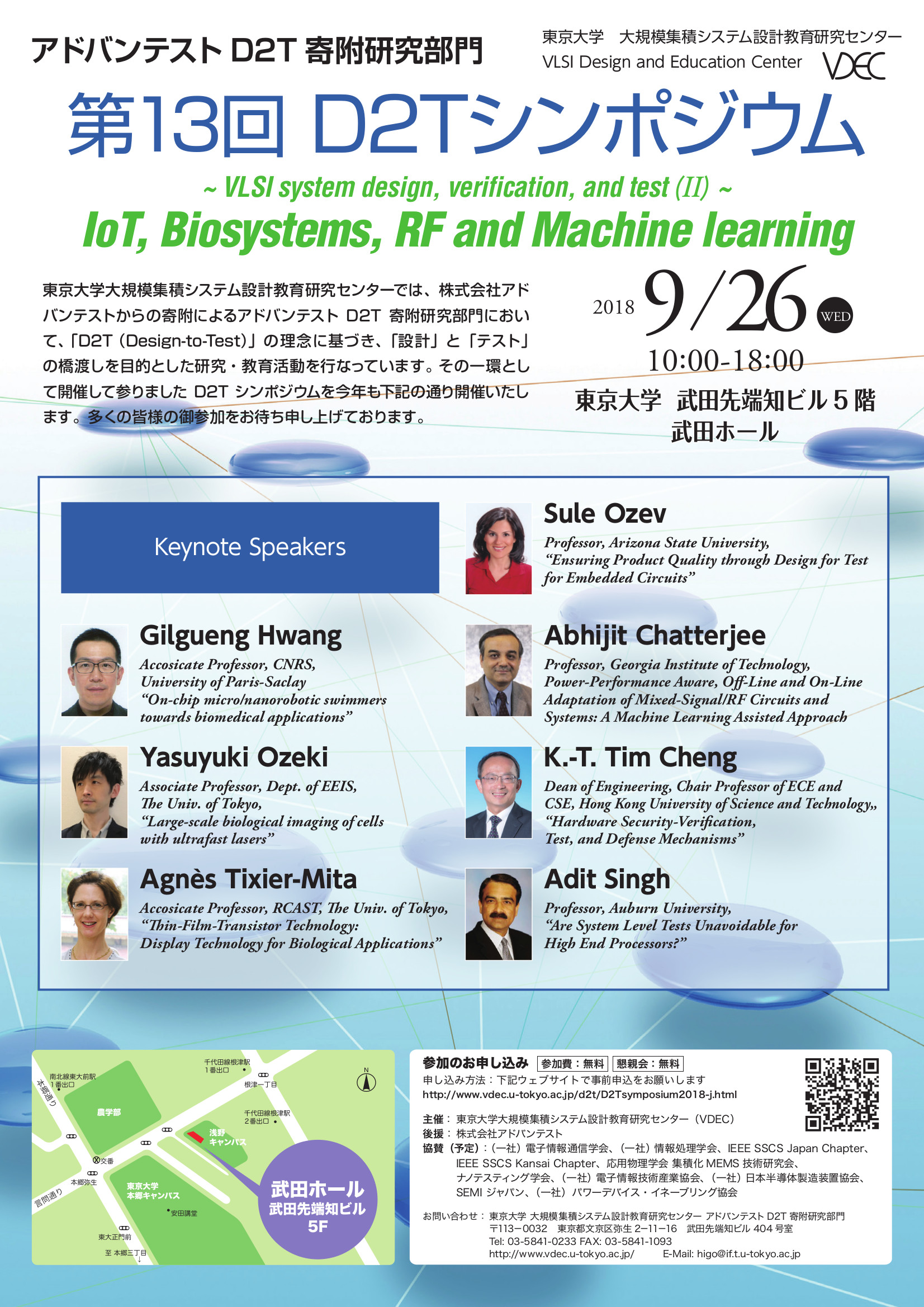

Session 1 - Special Lecture I Nano-Bio Electronics and Bio Photonics

|

|

"On-chip micro/nanorobotic swimmers towards biomedical applications"

Gilgueng Hwang (CNRS, University of Paris-Saclay)

|

|

Abstract

Micro/nanorobotic swimmers can serve as alternative microfluidic tools toward biologic or biomedical applications. We aim to develop highly energy efficient and fully controllable on-chip magnetic micro/nanorobotic swimmers with remote controlled functions such as cargo transport and sensing. In this talk, I will introduce our recently developed micro/nanorobotic swimmers including their fabrications by two-photon laser 3D nanolithography, force characterizatons and their microfluidics applications. Two applications to simulate their future in-vivo and lab-on-a-chip applications are demonstrated. First, the micro/nanorobotic swimmer serves as mobile micromanipulator inside microfluidic device to transpose microscale objects. Second, we demonstrate their physical sensing applications inside microfluidic control platform.

|

|

"Large-scale biological imaging of cells with ultrafast lasers"

Yasuyuki Ozeki (Dept. of EEIS, The University of Tokyo)

|

|

Abstract

Our research aims at rapid imaging of intracellular biomolecules using ultrashort pulsed laser to find cells which are capable of highly efficient bioproduction from a large heterogeneous population of cells. In the presentation, I will introduce our research on high-speed biological imaging, and introduce various analog/digital signal processing used therein.

|

|

"Thin-Film-Transistor Technology: Display Technology for Biological Applications"

Agnes Tixier-Mita (RCAST, The University of Tokyo)

|

|

Abstract

Thin-Film-Transistor (TFT) technology has been the primary technology for liquid crystal displays (LCD) fabrication for the past 30 years. With this technology, a large array of pixels is obtained, each pixel being individually controllable by a corresponding array of TFTs. This configuration is of great interest for electrical sensing and studies of biological entities: transparent devices with a wide and dense array of microelectrodes, controlled individually by an array of TFTs can then be obtained. Our group is investigating the usage of this technology for applications as wide as cells manipulation, neurons stimulation and excitation, culture monitoring and biomolecule sensing.

|

| 12:30 |

Lunch break |

| 14:00 |

Session 2 - Special Lecture II

|

|

"Ensuring Product Quality through Design for Test for Embedded Circuits"

Sule Ozev(Arizona State University)

|

|

"Power-Performance Aware, Off-Line and On-Line Adaptation of Mixed-Signal/RF Circuits and Systems: A Machine Learning Assisted Approach"

Abhijit Chatterjee (Georgia Institute of Technology)

|

|

Abstract

Real-time systems for wireless communication, digital signal processing and control experience a wide gamut of operating conditions (signal/channel noise, workload demand, perturbed process conditions, failures). As a consequence, they need to be tuned post-manufacture and in the field to maximize performance and error-resilience while minimizing power consumption. To enable such adaptation, we propose to sense device operating conditions using built-in sensors and/or low-overhead function encoding techniques. A key capability is that of being able to deduce multiple performance parameters of the system-under-test using compact optimized stimulus. The sensors and function encodings assess the loss in performance of the relevant systems due to workload uncertainties, manufacturing process imperfections and field degradation. These are then mitigated through the use of algorithm-through-circuit level compensation techniques. A key aspect of this work is in the use of machine learning algorithms for both performance estimation and post-manufacture/in-field tuning. The key objective is to deliver end-to-end desired application level Quality of Service (QoS), while minimizing energy/power consumption across dynamically changing operating conditions. Applications to mixed-signal designs, wireless communications systems and control applications are discussed.

|

| 15:30 |

Break |

| 16:00 |

Sesson 3 - Special Lecture III |

|

"Hardware Security - Verification, Test, and Defense Mechanisms"

K.-T. Tim Cheng (Hong Kong University of Science and Technology)

|

|

Abstract

In this talk I will illustrate several types of Hardware Trojans and security threats they create, as well as opportunities of Trojan insertion in all steps of the design, fabrication, and testing processes. I will then discuss their defense mechanisms, verification techniques for Trojan detection and prevention, and test-specific need and challenges for hardware security.

|

|

"Are System Level Tests Unavoidable for High End Processors?"

Adit Singh (Auburn University)

|

|

Abstract

A major new test challenge encountered by industry over the past 4-5 years is the rapidly growing need for expensive system level functional tests as a final test screen for processor SOCs. Traditional low cost scan based structural tests no longer suffice in delivering acceptable defect levels in shipped product. This presentation aims at explaining why system level tests (SLTs) have become unavoidable in the test flow for complex smartphone, notebook and other processor SOCs. We take an in-depth look at the limitations of traditional low cost scan based test methodology that appear to necessitate the use of functional SLTs as an additional final test screen. We then consider possible improvements to structural test that may mitigate these shortcomings and minimize the need for SLTs.

|

| 17:30 |

Session 4 - VDEC D2T Research Division |

|

"Activities of D2T research division"

Akio Higo (VDEC D2T, The University of Tokyo)

|

| 17:45 |

Closing |

| 18:00 |

Reception |