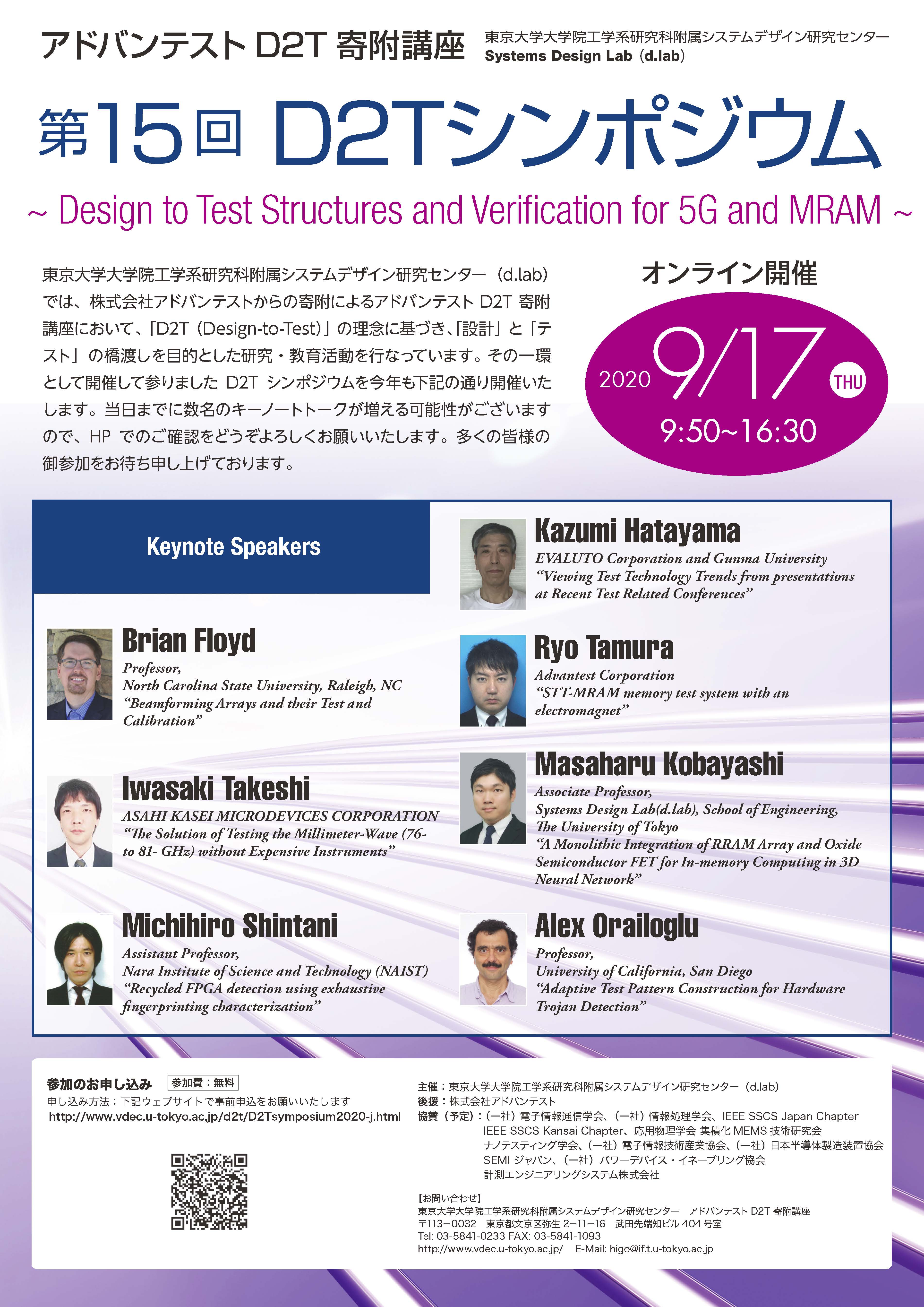

The 15th D2T Symposium, The University of Tokyo

September 17th (Thu.), 2020

Virtual Conference

News:

- Symposium homepage was opened. (2020/7/13)

- Symposium homepage was updated. (2020/7/17)

- Symposium homepage was updated. (2020/7/26)

- Symposium homepage was updated. (2020/8/09)

- Registration started. (2020/8/10)

- D2T special seminar HP (English) is opened. (2020/09/06)

- This symposium is over. Thank you. (2020/9/17)

Symposium Overview

From the organizer:

"D2T Symposium" will be held on 17th September, 2020, as

15th meeting of symposium series first started in 2008.

We have been pursuing in "design", "test", and their bridging technologies

in the symposia

as indicated in the name "D2T" that means "Design to Test".

This year, we will invite lecturers overseas, Professor Brian Floyd from North Carolina State University, Professor Alex Orailoglu from University of California, San Diego, Mr. Takeshi Iwasaki from ASAHI KASEI MICRODEVICES, Kazumi Hatayama-sensei from EVALUTO Corporation and Gunma University, Assistant Professor Michihiro Shintani from NAIST, Associate Professor Masaharu Kobayashi from d.lab, the University of Tokyo and Mr. Ryo Tamura from Advantest Corporation for their distinguished research topics.

We look forward to all of your participation in the symposium.

Symposium Abstract (日本語版, Japanese version)

| 9:50 | Opening remarks |

|

Tadahiro Kuroda, Director, d.lab, school of Engineering, the University of Tokyo Yoshiaki Yoshida, President & CEO, ADVANTEST Corporation |

|

| 10:00 | Session 1 - Special Lecture I |

|

"Beamforming Arrays and their Test and Calibration" Brian Floyd, Professor (North Carolina State University, Raleigh, NC) |

|

|

Abstract Millimeter-wave systems rely on beamforming to shape and steer a beam to enhance gain and/or reduce interference. This presentation will provide an overview of beamforming front-ends and the requirements for achieving desired patterns. This will be followed by an in-depth presentation of a code-modulated built-in self-test and calibration technique which can be used within any array to achieve an optimized response when packaged with antennas. |

|

|

"Adaptive Test Pattern Construction for Hardware Trojan Detection" Alex Orailoglu, Professor (University of California, San Diego) |

|

|

Abstract As society becomes increasingly reliant on products and systems that make use of integrated circuits, the defense against potential hardware Trojan attacks by an untrusted foundry becomes an important part of any certification flow for critical components. While there have been many recent proposals, they fall short by either requiring impractical design/test pattern cost or achieving insufficient detection capabilities, primarily challenged by the noise induced by process variation. We put forth a methodology to remedy this, leveraging an adaptive approach which applies superposition to perform a fine-grained circuit analysis and expose any existing Trojan circuitry. Iterative test pattern modifications, circuit response analysis, and adaptive decision-making are deployed, all working within the design-for-test and test pattern cost paradigms of a common industrial circuit. We demonstrate the efficacy of this technique on the standard combinational Trust-Hub Trojan benchmark circuits, showing significant improvement over prior techniques. This methodology provides a reliable and effective means for Trojan detection, covering an important piece of the overall circuit certification puzzle. |

|

|

"The Solution of Testing the Millimeter-Wave (76- to 81- GHz) without Expensive Instruments" Takeshi Iwasaki (ASAHI KASEI MICRODEVICES CORPORATION) |

|

|

Abstract For the last decade, the automotive industry has been growing fast. The brake assistance and collision avoidance protect and save our lives. The Monolithic Millimeter-wave Integrated Circuit (MMIC) for the automotive radar is an important component. But, the MMIC production testing requires expensive instruments. This presentation will introduce how to measure the wave in 80GHz without using expensive instruments. |

|

| 12:00 | Lunch break |

| 13:00 | Session 2 - Special Lecture II |

|

"Recycled FPGA detection using exhaustive fingerprinting characterization" Michihiro Shintani, Assistant Professor (Nara Institute of Science and Technology) |

|

|

Abstract Recycled field-programmable gate arrays (FPGAs) are now becoming a rising concern as a major incident. We present an accurate recycled FPGA detection method that fully characterizes frequencies on all paths of FPGAs. Experiments using commercial FPGAs demonstrate that our method successfully recognizes aged FPGAs that cannot be detected by conventional methods. |

|

|

"Viewing Test Technology Trends from presentations at Recent Test Related Conferences" Kazumi Hatayama (EVALUTO Corporation and Gunma University) |

|

|

Abstract Never ending demands on performance, power, area and so on have been driving many areas of semiconductor technology, including test technology. To meet these demands, many solutions have been presented at technical conferences. This presentation shows test technology trends based on the presentation at ITC and VTS in this decade and foresees the next decade. | |

|

"STT-MRAM memory test system with an electromagnet" Ryo Tamura (ADVANTEST Corporation) |

|

|

Abstract The magnetic field application is needed for STT-MRAM(Spin-transfer-torque Magnetic Random Access Memory) testing since STT-MRAM use a magnetization direction in free layer of an MTJ (Magnetic Tunnel Junction) to store the digital information. In this presentation, developed new memory test system with an electromagnet for STT-MRAM wafer-level testing will be introduced. |

|

|

"A Monolithic Integration of RRAM Array and Oxide Semiconductor FET for In-memory Computing in 3D Neural Network" Masaharu Kobayashi, Associate Professor (d.lab, the University of Tokyo) |

|

|

Abstract We have developed a monolithic integration of RRAM array and oxide-semiconductor access transistor in 3D stack, achieved uniform memory characteristics of 1T1R cells at each layer, and demonstrated basic functionality of in-memory computing. 3D neural network built by this architecture has high potential to enable area-efficient, low-power and low-latency computing. |

|

| Session 3 - Advantest D2T Research Department | |

|

"Activities of Advantest D2T Research Department" Akio Higo (d.lab D2T, the University of Tokyo) |

|

| Closing |

Registration (free of charge)

This symposium is closed. Thank you.

Access to the Symposium

Please look at the MAP.

D2T Symposium history

Contact

ADVANTEST D2T Research Department,

Sysmtems Design Lab (d.lab), School of Engineering, The University of Tokyo

Room 404, Takeda Building,

Yayoi 2-11-16, Bunkyo-ku, Tokyo, 113-0032, Japan

Tel: +81-3-5841-0233 FAX: +81-3-5841-1093

E-mail: higo[at]if.t.u-tokyo.ac.jp

Sysmtems Design Lab (d.lab), School of Engineering, The University of Tokyo