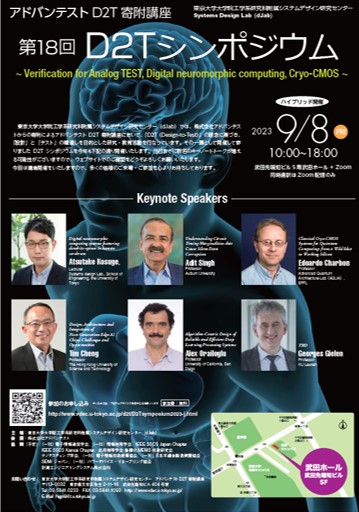

The 18th D2T Symposium, The University of Tokyo

September 8th (Fri.), 2023

On site only: Takeda Hall, 5th floor of

Takeda Building,

The University of Tokyo

MAP

News:

- Symposium homepage was opened. (2023/7/19)

- Registration started. (2023/8/1)

- The seminar is closed. (2023/9/8)

Symposium Overview

From the organizer:

"D2T Symposium" will be held on 8th September, 2023, as 18th meeting of symposium series first started in 2008.We have been pursuing in "design", "test", and their bridging technologies in the symposia as indicated in the name "D2T" that means "Design to Test".

This year, we will invite lecturers overseas, Lecture, Atsutake Kosuge from d.lab University of Tokyo, Edoardo Charbon, Professor from EPFL, Georges Gielen, Professor from KU Leuven, Alex Orailoglu, Professor from University of California, San Diego,

Adit Singh, Professor, Auburn University, K.-T. Tim Cheng, Professor, from U-Tokyo Fellow and Hong Kong University of Science and Technology, for their distinguished research topics.

We look forward to all of your participation in the symposium.

This symposium is early days of The 7th International Test Conference in Asia 2023 (ITC-Asia 2023) (Sep. 12-14) at Kunibiki Messe, Matsue, Shimane. Please also attend the conference.

Time table (日本語版, Japanese version)

10:00 |

Opening remarks |

||||||||||||||||||||||

Tadahiro Kuroda, Director, d.lab, school of Engineering, the University of Tokyo

|

|||||||||||||||||||||||

10:15 - 11:45 |

Session 1 - Special Lecture I

|

10:15 - 11:00 |

" Classical Cryo-CMOS Systems for Quantum Computing: from a Wild Idea to Working Silicon"

|

11:00 - 11:45 |

"Digital neuromorphic computing systems featuring dendrite-spines in human cerebrum"

|

11:55 - 13:00 |

Lunch Break |

11:45 - 14:00 |

Lunch Break |

14:00 - 15:30 |

Sesson 2 - Sepecial Lecture II

|

"Boosting defect coverage for analog/mixed-signal ICs: machine learning to the rescue"

|

|

"Algorithm-Centric Design of Reliable and Efficient Deep Learning Processing Systems"

|

|

15:30 - 15:45 |

15 min break |

15:45 - 17:15 |

Session 3 - Special Lecture III

|

"Understanding Circuit Timing Marginalities that Cause Silent Data Corruption Ratio based Resistive Memory Cells for Low Error Rate and High Energy Efficiency"

|

|

"Design, Architecture and Integration of Next-Generation Edge AI Chips: Challenges and Opportunities"

|

|

17:15 - 17:30 |

Sesson 4 - Activities of D2T Research Department

|

"Activities of D2T Research Department"

|

|

Closing

|

Symposium abstract (日本語版, Japanese version)

Registration (free of charge)

D2T Symposium history

Contact

ADVANTEST D2T Research Department,

Sysmtems Design Lab (d.lab), School of Engineering, The University of Tokyo

Room 404, Takeda Building,

Yayoi 2-11-16, Bunkyo-ku, Tokyo, 113-0032, Japan

Tel: +81-3-5841-0233 FAX: +81-3-5841-1093

E-mail: higo[at]if.t.u-tokyo.ac.jp

Systems Design Lab. (d.lab), School of Engineering, The University of Tokyo